【產品單頁】5G AIoT開發套件V2

產品單頁見下方附件*附件:5G AIoT開發套件V2--20240316(1).pdf

2024-03-15 20:31:13

M.2 NVME/M.2 SATA SSD PCIE X4

2024-03-14 22:02:08

M.2 NVMe SSD PCIe 4.0 Adapt w/HS

2024-03-14 22:02:08

6 6 Pin PCIe to (2) SATA 15 Pin

2024-03-14 22:02:05

1.PCIe 3.0 x16配置下,支持8路4K(3840x2160p)@60Hz的采集與顯示2.PCIe 3.0 x8配置下,支持4路4K(3840x2160p)@60Hz的采集與顯示3.PCIe

2024-03-13 13:59:45

stm32F407ADC+DMA 10路采集2路數據異常(通道9/10)使用的是0/1/2/38/9/10/11/12/13 通道9與通道10 雖然有數據但不變化好像與外邊是斷開的配置都是相同的其余各通道采集正常

2024-03-13 07:38:09

(Queue or Non-Queue,Ring)(3) V4L24 交付清單可交付資料:1. 詳細的用戶手冊2. 設計文件:源代碼或網表3. 時序約束4. 測試或Demo工程5. 技術支持:郵件,電話,現場,培訓服務6. Email:neteasy163z@163.com

2024-03-07 13:54:29

什么是PCIe?PCIe有什么用途?什么是PCIe通道,x1、x4、x8和x16是什么意思?PCIe 5.0有何不同? PCI-Express(peripheral component

2024-01-30 16:09:25 503

503 /步進伺服驅動器;(2)聯動軸數最高可達16軸,運動周期最小為100μs;(3)標配8進8出,其中4路高速鎖存輸入和8路高速PWM、PSO輸出,更多IO請選配ACC37接線板擴展板;(4)支持PWM

2024-01-24 09:48:21

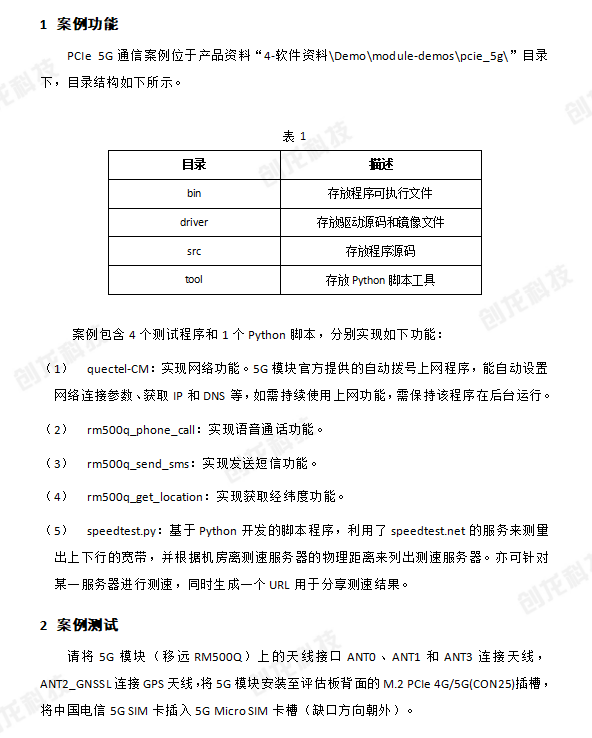

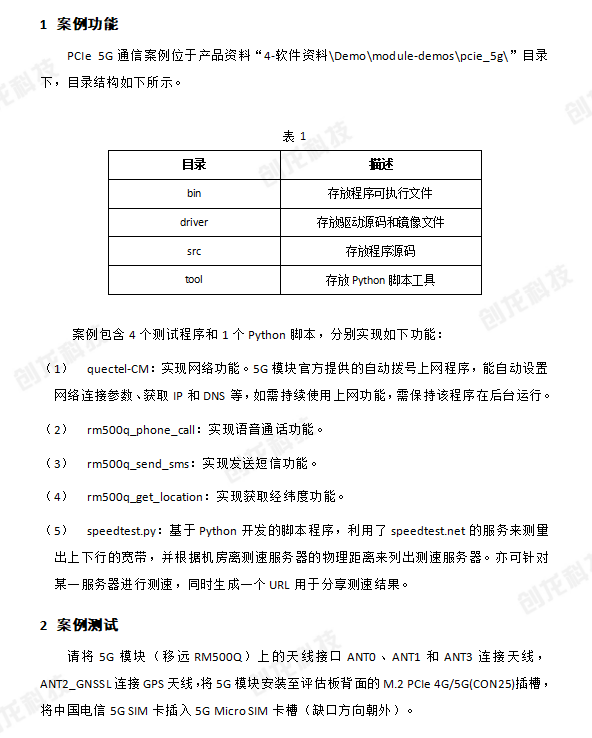

RK3568-PCIe 5G通信測試手冊

2024-01-18 14:53:55 227

227

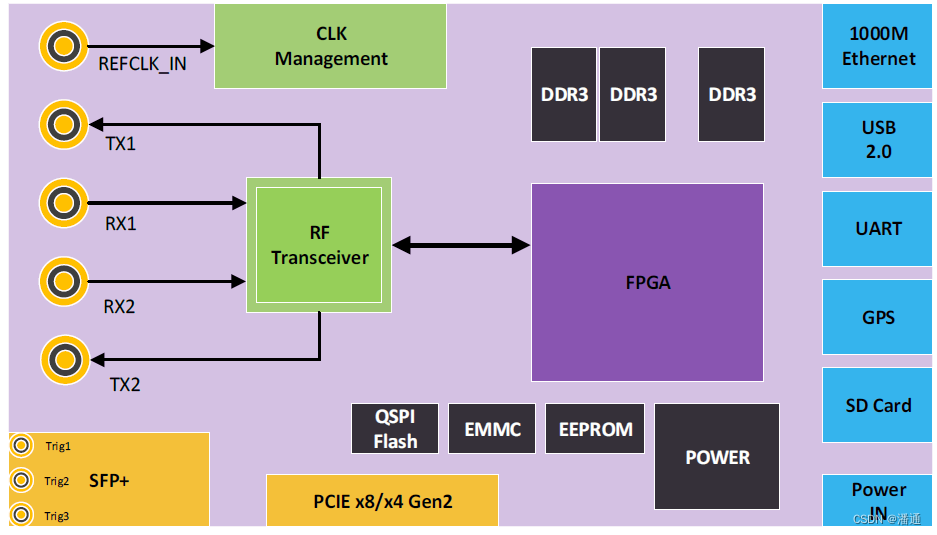

的數據交互時鐘頻率最高到 533MHz,2顆DDR3的數據位寬為32bit,總數據帶寬最高到34112(1066×32)Mbps,充分滿足了高速多路數據存儲的需求。另外,盤古200K帶有4路HSST高速收發器,每路速度高達 6.6Gbps,非常適合用于光纖通信和 PCIe 數據通信。

2023-12-28 15:26:19

到 533MHz,2顆DDR3 數據位寬32bit,總數據帶寬最高到34112(1066×32)Mbps,充分滿足高速多路數據存儲的需求;另外帶有4 路HSST高速收發器,每路速度高達6.6Gbps,非常適合用于光纖通信和PCIe 數據通信;電源采用多顆 EZ8303(艾諾)來產生不同的電源電壓。

2023-12-28 15:17:43

實驗室數據采集 , 視頻數據收發卡 , 信號采集、分析 , PCIe的視頻數據卡 , 模擬輸出,存儲

2023-12-22 09:40:16 145

145

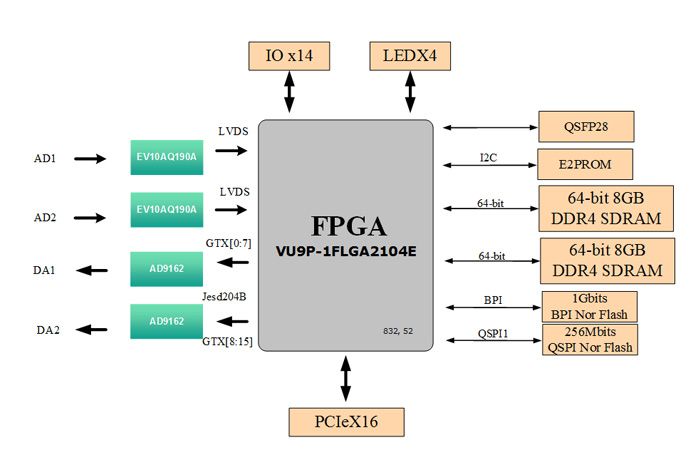

一、產品概述 基于PCIe的一款分布式高速數據采集系統,實現多路AD的數據采集,并通過PCIe傳輸到存儲計算服務器,實現信號的分析、存儲。

產品固化FPGA邏輯,適配2路1Gsps/2路

2023-12-11 11:36:40

,可實現 AI 加速卡與4G、5G 通信等多種功能模塊的擴展。

開發板的外觀如圖1和圖2所示。

圖1 開發板正面

圖2 開發板背面

在功能分布方面,參見圖3和圖4所示。

圖3 正面布局

圖4

2023-12-07 11:26:12

電路示波器時序見附件:

通過示波器觀察和軟件測試,都發現ad3-4路輸出為0x0000或0xffff。第1、2路采樣ok。

您能否幫忙看看問題在哪不?

詳細的各種圖,波形請見word附件,我已經進行了整理。謝謝

2023-12-04 07:27:54

二次開發,滿足各種功能的自定義

2+8口千兆5G路由器帶來新的方式,讓您項目輕松接入更多設備,節省交換機投入和位置空間更合理

路由器內置802.11ax (Wi-Fi 6) 技術,單個5G WiFi6

2023-11-30 15:27:34

隨著英特爾Alder Lake CPU的發布,以及AMD 7000 Ryzen CPU的即將發布,PCIe 5.0 硬件終于成為現實。但什么是 PCIe 5.0?

2023-11-18 16:48:14 1300

1300

紫光的logos系列的PGL50H/PGL100H、logos-2全系列都集成gen2×4的PCIE硬核,且官方也提供了例程。

紫光的PCIE用起來還是挺方便的,生成IP的同時生成了對應的PCIE

2023-11-17 14:35:30

TG463 5G千兆工業路由器 TG463系列5G千兆工業路由器,支持5G網絡,具備5路千兆網口,4路POE口。接口豐富,同時接入更多設備及傳感器。支持IEC101、IEC104電力規約以及

2023-11-13 10:17:12

9.5mm。這種創新的移動硬盤盒能夠裝入單個PCIe x4擴展插槽,可輕松從PCIe插槽中拆卸U.2/U.3 NVMe SSD,同時最大程度地減少數據和電源線的混

2023-11-03 11:49:55

多種設備的連接。

2、傳輸速率簡介

PCIe 分類、速度,按lane的個數分有 x1 x2 x4 x8 x16 (最大可支持32個通道),按代來分 有 gen1 gen2 gen3 gen4

PCIe

2023-11-02 09:31:28

1.4 P1.5是否為0,把該值放入數組1

3.CRC校驗放入數組2,P5.4作為收發控制。把上述數組依次用串口發出,P3.0 P3.1作串口收發

4.當P1.2為0的值通過串口發到上位機后,上位機接通相應的繼電器后返回一值然后在P3.6輸出低電平

斷開相應的繼電器后返回一值然后在P3.6輸出高電平

2023-10-07 06:16:43

支持HOST/DEVICE

底板參數:

POWER: 電直流電源輸入接口

SWITCH: 電源開關

EEPROM: 支持

MINI PCIE2.0: 支持4G模塊和5G模塊

PCIE3.0接口: 1個

2023-09-28 11:15:05

本文我們將向大家介紹PCIe引腳定義以及PCIe協議層。

2023-09-26 11:39:14 5653

5653

SATA、2路USB2.0、2路USB3.0、LAN、RS232、VGAHDMI等,底板資料開源,提供底板的原理圖和PCB工程文件,用戶可以很方便靈活的進行目標產品定制,快速開發高穩定行業產品。

國產

2023-09-26 10:33:47

220V電源再安裝,某些服務器,在

220V輸入時,PCIe插槽有漏電。

2、 安裝完后,先不要蓋好后蓋,power on上電,從上側觀察LED狀態,如下圖所示,4個

燈的狀態,藍藍綠紅,為SC5上電正常

2023-09-20 06:11:27

應用場合。

底板方面:底板分為連接器與郵票孔兩種版本,雙路千兆以太網、SATA3.0PCIE 3.0、MIPI、HDMI、MIPI、CAMERA、4G、5G等接口一應俱全。

系統方面:支持國產實時操作系統

2023-09-13 11:06:39

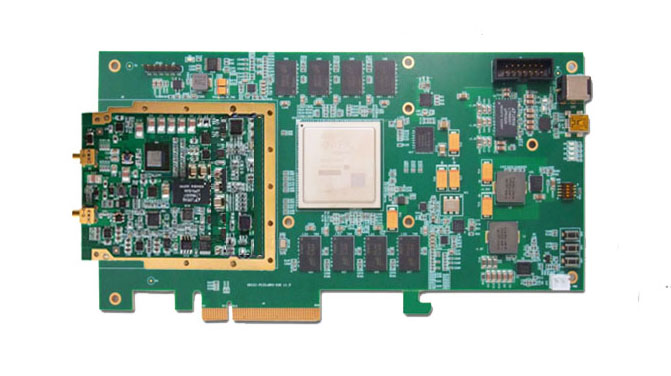

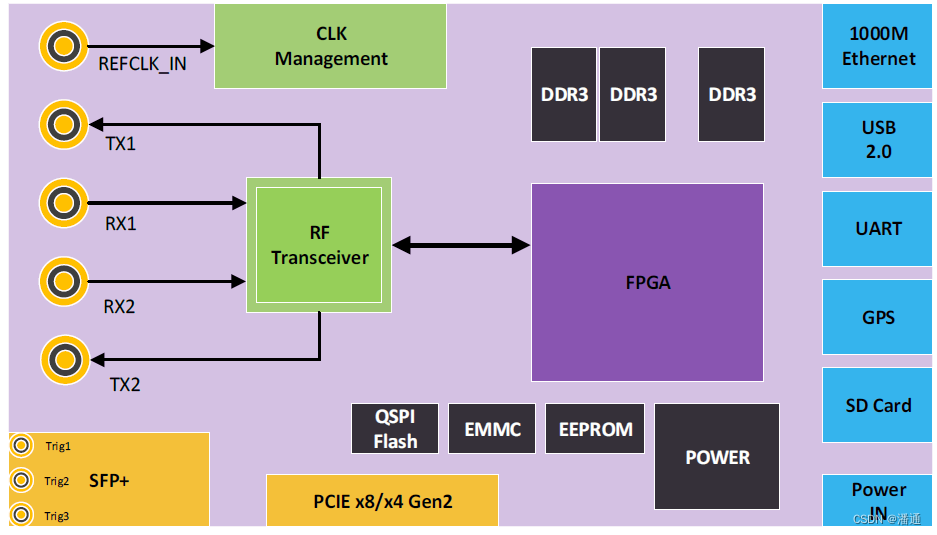

QT1509RF射頻收發板卡是一款基于RF IC架構的零中頻PCIe總線軟件無線平臺。可實現雙路射頻接收、雙路射頻發送,支持帶寬可達200MHz,能夠適應不同頻段和功率要求,調諧范圍75MHz~6GHz。頻段可覆蓋2G/3G/4G/5G平臺應用;可應用于通信、雷達、衛星測試驗證、系統構建等場合。

2023-09-09 17:22:21 519

519

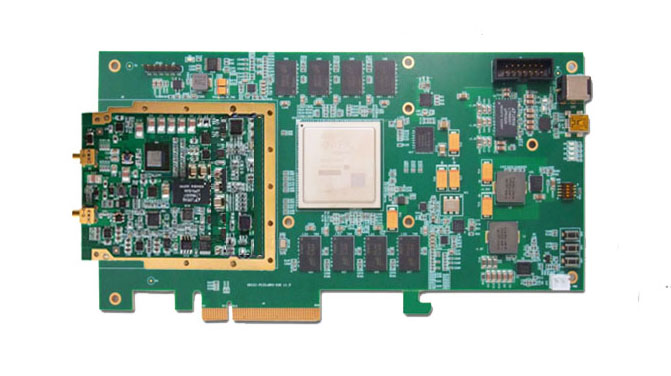

Atlas200I A2+PCIE X4接口測試FPGA 實物圖片

全愛科技QA200A2 Altas200I A2開發套件做了驗證。

圖 1-2 QA200A2 Atlas200I A2 開發套件實物圖

2023-09-05 14:39:57

25Mbit,支持PCIE3.0串行總線接口,最高功耗7.6W。產品特性 標準3U PXIe萬兆網卡對外提供2路10GE SFP+接口支持網絡協議(TCP/UDP,IP,FCOE)加速,支持數據中心協議加速

2023-08-22 11:53:18

本文檔旨在提供關于將PCIe接口集成到基于AMBA的片上系統(SoC)的指導。

假設PCIe接口通過基于AXI或ACE協議的互連連接到SoC的其余部分。

讀者應熟悉PCIe、AMBA AXI

2023-08-17 07:25:03

)

待機不接屏功耗

Andriod 11:400mA

核心板尺寸

68mmx45mm

核心板層數

8層沉金工藝

接口方式

BTB 80P 0.5mm 4條共320P

USB2.0

2路,獨立USB2.0

2023-08-10 16:52:37

,可通過雙網口訪問和傳輸內外網的數據。擁有WIFI/BT,PCIE 3.0接口及 SIM 座,可接 4G 通信模塊,提高網絡傳輸效率。滿足NVR、工業網關等多網口產品需求。

板載 5路 串口,能夠

2023-08-07 10:00:25

自2003年推出以來,PCIe發展至今已經從最初的1.0升級到了6.0,在上一篇文章中為大家介紹了PCIe基礎知識:《什么是PCIe?》 ,本文則為大家簡單介紹一下 PCIe 標準的演進歷史以及

2023-07-26 08:05:01 867

867

PCIe2 to S-RIO2 Bridging and Switching Evaluation Platform 原理圖

2023-07-11 20:31:47 0

0 PCIe是一種高速串行計算機擴展總線標準,自2003年推出以來,已經成為服務器(Server)和PC上的重要接口。今天為大家簡單介紹一下PCIe的發展歷史以及它的工作原理。 一、PCIe的由來

2023-07-04 18:15:03 9778

9778 單路3G帶寬模擬信號源卡由DA子卡和PCIe底板組成,二者通過標準FMC連接器互聯,可以實現將PCIe總線數據轉換為一路高速的模擬量輸出。該板可廣泛用于雷達、通信、光電領域的噪聲信號、毛刺、脈沖信號模擬產生等領域。

2023-06-15 11:35:17 567

567

4GPCIe 5G

USB WIFIADC

4 開發資料(1)提供核心板引腳定義、可編輯底板原理圖、可編輯底板PCB、芯片Datasheet,縮短硬件設計周期;(2)提供系統固化鏡像、內核驅動源碼

2023-06-13 17:18:31

refclk1(硬件上已固定),可參考下圖:

4. 其他設置可保持默認,點擊 Generate 生成 PCIE IP;:

5.關閉本工程,按此路徑打開 Example 工程:

2

2023-06-13 15:50:05

我是一名PCIe新手,想了解以下問題:

1、如何測試PCIe?

2、如何讀寫PCIe(兩塊開發板通過PCIe線互連,分別配置為RC和EP)?

3.如何支持NTB?

2023-06-12 06:05:51

根據 S32G-VNP-RDB2 原理圖:SPF-47440_D3.pdf,有一個名為 LLCE_ERR1_B 的信號連接到 PF_00 (GPIO[80])。信號通過接線與方式形成 6 個 CAN

2023-06-06 06:56:22

充分考慮信號完整性EMC電磁兼容、以及工業級寬溫設計

底板

底板引出多路PCIE、4路SATA、2路USB2.0、2路USB3.0、LAN、RS232、VGAHDMI等,底板資料開源,提供底板的原理圖

2023-05-23 10:36:29

PCI Express? 6.0 (PCIe? 6.0) 規范由 PCI-SIG? 于 2022 年 1 月發布。最新一代的 PCIe 標準帶來了許多激動人心的新功能,旨在提高計算密集型工作負載的性能,包括數據中心、 AI/ML 和 HPC 應用程序

2023-05-22 17:27:51 4394

4394

多層板材,運行穩定可靠、器件生命周期長,已批量生產,可長期提供技術支持原理框圖: 主要技術參數:產品配置:l PCIe3.0x8接口,支持帶寬≥5GB/sl 2組獨立DDR3: 64bit位寬,最大

2023-05-21 18:27:41

想在 Layerscape 平臺上使用 5G 模組?隨附的應用說明將幫助您做到這一點。

該 AN 將幫助您:

1.在Layerscape平臺上設置5G環境

2. 將 5G 模塊連接

2023-05-17 06:24:06

插入機箱時能夠查到PCIE設備,但是不使用擴展板,直接將插針式連接器插入機箱則無法識別。想問一下是耦合電容的問題嗎,或者其他什么原因?

pcie連接器原理圖如下

2023-05-16 11:07:40

適合用于光纖、PCIe 等高速數據通信的接口。

MES100P 開發板上還擴展了豐富的外圍接口,其中包含了一個 PCIe X4 接口、兩路光纖通信模塊接口、一路 HSSTLP 的同軸電纜接口、一路千兆

2023-05-16 11:06:44

PCIe2 to S-RIO2 Bridging and Switching Evaluation Platform 原理圖

2023-05-15 19:20:08 0

0 :

SecurityModeComplete

SecurityModeComplete消息用于確認安全模式命令的成功完成。發送此消息,加密將被啟用。請注意,該消息是受完整性保護的。

SecurityModeFailure

安全模式建立失敗,則發送該消息。消息內容,如圖所示:

原作者:Ms多多 5G微課堂

2023-05-10 15:38:50

、軟件無線電處理平臺2)通信、衛星、雷達等信號處理3)數據采集存儲、波形生成與回放4)接口控制、脈沖處理、測控儀器5)高性能計算、服務器硬件加速、算法驗證平臺、Net FPGA主要技術參數一)產品配置1

2023-05-09 20:07:51

5G天線被廣泛使用。2G和3G頻段已經很少實用,現在使用較多的大多是4G和5G。有很多客戶對5g天線和4g天線通用都不是很確認,答:明確告訴你,4G和5G天線不能通用,5G天線用到是不能用到4G

2023-05-09 14:26:32

你好

作為我們在 ls1028 上努力的一部分

我們通過 pcie 將自定義 fpga 連接到 M.2 連接器(通道 C/2 - j16)

相關uboot日志:

U-Boot

2023-05-09 12:00:30

和8K@30fps H265/H264視頻編碼。

核心板

核心板+底板結構,拆卸方便,核心板引腳320PIN全部引出滿足擴展需求助力產品開發。

接口豐富

雙路千兆以太網、5G/4G模塊、HDMI輸入、HDMI輸出

2023-05-09 10:31:24

4G,2x2MIMO已經成了標配,4x4MIMO屬于高配;而到了5G時代,4x4MIMO則已成為了標配,主流的手機都可以支持。

因此,地鐵覆蓋必須要考慮對4x4MIMO的支持。由于MIMO系統發送

2023-05-06 15:01:40

MIMO(多入多出)。

由下圖可見,不同頻段下,手機的能力是不一樣的。在中國5G的主流頻段3.5GHz或者2.6GHz上,手機可支持4路接收,2路發射;毫米波頻段次之,能支持2路接收,2路發射;像

2023-05-06 14:34:55

:一,周期廣播,二,動態發送,即網絡根據UE發送的請求來觸發。(這一點,是5G NR新增的內容,在4G中,系統消息的發送均是周期性廣播的)

總結:UE開機接入NR小區后,MIB和SIB1是一定會解讀

2023-05-06 12:40:52

Phase compensation

與4G不同,5G NR支持多種可變的載波帶寬以及載波內BWP的分配,因此收發兩端的中心頻點不一致是一個非常典型的場景,如不進行合適的相位補償會出現接收機無法正確解調

2023-05-06 11:49:57

,5G毫米波技術對于用戶峰值速率仍有很大提升空間。

圖2:OoklaSPEEDTEST實測數據。

5G毫米波的第二個優勢是易與波束賦形技術結合。5G毫米波的頻段高、波長短,使得其在

2023-05-05 10:49:47

1.前言

同步是通信系統最關鍵的功能之一。然而,在5G的環境中,特別是對于上行鏈路和下行鏈路傳輸在同一頻率上的時分雙工(TDD),干擾的可能性要大得多。因此,我們看到了TDD-LTE

2023-05-05 10:36:02

了前傳的負載。性能優化的要求不僅限于前傳,因為資源實例化的位置、訪問和管理都很大程度上取決于服務切片的要求。在這種情況下,基于 SDR 和SDN/NFV 的架構(圖 4)可以提供幫助。

5G 優化

2023-05-05 09:48:29

) 連接到處理器的單個 PCIe x4 控制器。

如果是,這是否稱為 PCIe 分叉?

(我想我在這里遺漏了一些明顯的東西,從以前的經驗/記憶來看,似乎上面應該是可能的。但也請指出 PCIe 標準的相關部分,以便我提高對此的理解。)

2023-05-05 07:35:41

信息

以太網

2路千兆RJ45

USB接口

2路USB2.0 HOST,其中一路與4G模塊接口復用

LCD接口

1路LCD接口(支持24位輸出)

按鈕

2個(電源、復位按鈕)

LED燈

4個用戶

2023-04-27 08:59:02

#s32g3 RDB3 S32G399A我正在基于 SDK BSP35 在 CPU 為 S32G399A 的 S32G RDB3 板上開發 PCIe。我發現,通過將 0x4 寫入

2023-04-18 07:45:06

。全功能接口集成底板擴展網口、雙路千兆以太網、SATA3.0、PCIE3.0、MIPI、EDP、HDMI、CAMERA、4G/5G等全面接口,滿足各領域產品功能接口需求。多個操作系統

2023-04-17 10:14:03

intel X550 10Gb NIC。NIC 以模塊和卡正確協商的 Gen2 速度工作,pcie 鏈路以 Gen2 速度運行(最大吞吐量為 4Gb/s)。使用iperf3 測試速度,在主機PC 中使

2023-04-17 08:44:56

2 組 64bit 的DDR4 SDRAM,每組容量2GB,可穩定運行在2400MT/s。支持PCIE Gen3 x8模式及一路FMC HPC接口。同時可提供 Windows,Linux 上位機驅動

2023-04-13 15:56:21

: B??AR[5] [??? 0x00000000 標志 0x0] [ 5.348569] sprd-pcie-ep-device 0000:00:00.0: 不能 ioremap BAR 4

2023-04-11 06:30:27

M31 PCIe 5.0 PHY IP,用于存儲和高帶寬連接 M31 PCIe 5.0 PHY IP為高帶寬應用提供高性能、多通道功能和低功耗架構。PCIe 5.0 IP支持一系列PCIe

2023-04-03 19:57:12

用程序,并符合PIPE 4.3規范。IP集成了高速混合信號電路,以支持8Gbps的PCIe 3.1流量。它向后兼容5.0Gbps的PCIe 2.1數據速率和2.5G

2023-04-03 19:50:56

M31 PCIe 2.1 PHY IP M31 PCIe 2.1收發器IP提供了一系列完整的PCIe 2.1基本應用程序。它符合PIPE 3.0規范。該IP集成了高速混合信號電路,以支持

2023-04-03 19:47:28

硬件:S32R45 評估板 Crucial 英睿達 P3 1TB PCIe M.2 2280 固態硬盤我通過一根M.2轉PCIE線將SSD連接到EVB的PCI接口,如下圖:EVB板啟動后,在shell界面輸入如下命令:

2023-04-03 08:56:25

是 VDD_PCIE_DIG_1P8_3P3引腳——我們在定制板中將其設置為 1v8。但是,MEK 板使用 3v3。定制板i.MX8QXP-MEK VDD_PCIE_DIG_1P8_3P3電壓變化是否也需要更改設備樹?PHY 鏈路問題是否是由模塊和處理器之間的阻抗不匹配引起的?

2023-04-03 06:31:15

PI3PCIE2415EVALBOARD

2023-03-30 11:41:37

PI2PCIE2412-EVALUATIONBOARD1

2023-03-30 11:41:15

PCIE-52P90H

2023-03-29 22:43:17

0 配置為 RootComplex(x2)為 PCIe1 使用外部時鐘為 PCIe1 配置的頻率 125Mhz將 PCIe1 配置為 SGMII [XPCS0 1G, XPCS1 OFF(PCIex1

2023-03-29 06:13:08

1 個上游和 4 個下游)來支持 4 個 USB 端口。我還想知道是否可以使用 PCIe 到 USB 主機控制器將 USB 端口連接到 PCIe X2。

2023-03-27 08:54:43

電子發燒友App

電子發燒友App

評論