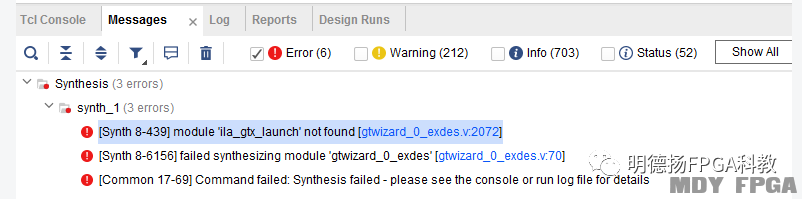

Vivado在使用A7芯片時,使用內部邏輯分析儀時,在非AXI總線下最多只能綁定64組信號(例化一個或者多個ILA模塊,信號組數相加不能超過64),如果超過64組會出現錯誤。

Xilinx Vivado軟件ILA使用心得

- Xilinx(119162)

相關推薦

如何在下載Bitstream后自動觸發(fā)ILA采集

在硬件調試時,經常需要用 ILA 采集一些 FPGA 內部或者對外的初始化信號,然而在下載完 Bitstream 后立即采集這些變化稍縱即逝的信號,比如在 1uS 內手動觸發(fā) ILA 采集信號

2024-02-23 09:45:49 373

373

373

373

如何禁止vivado自動生成 bufg

在Vivado中禁止自動生成BUFG(Buffered Clock Gate)可以通過以下步驟實現。 首先,讓我們簡要了解一下什么是BUFG。BUFG是一個時鐘緩沖器,用于緩沖輸入時鐘信號,使其更穩(wěn)

2024-01-05 14:31:06 454

454

454

4541-2B參數規(guī)模大模型的使用心得

大模型時代,根據大模型縮放定律,大家通常都在追求模型的參數規(guī)模更大、訓練的數據更多,從而使得大模型涌現出更多的智能。但是,模型參數越大部署壓力就越大。即使有gptq、fastllm、vllm等推理加速方法,但如果GPU資源不夠也很難保證高并發(fā)。

2023-12-28 11:47:14 432

432

432

432

VIVADO安裝問題解決

vivado出現安裝問題剛開始還以為是安裝路徑包含中文空格了,重裝的注意了一下,發(fā)現還是這個問題。。。。后來又一頓操作猛如虎,終于發(fā)現了問題。出這個問題的原因是vivado壓縮包解壓的路徑包含中文了把解壓文件放到不含中文的地方,再重新安裝,安裝路徑也不能含中文。然后。。。。。然后就安裝完成了

2023-12-22 10:56:33 0

0

0

0關于PCB板ESD設計的實用心得

在做ESD放電測試時通常采用兩種方法:接觸放電和空氣放電。接觸放電就是直接對待測設備進行放電;空氣放電也稱為間接放電,是強磁場對鄰近電流環(huán)路耦合產生。這兩種測試的測試電壓一般為2KV-8KV,不同地區(qū)要求不一樣,因此在設計之前,先要弄清楚產品針對的市場。

2023-12-08 15:26:55 162

162

162

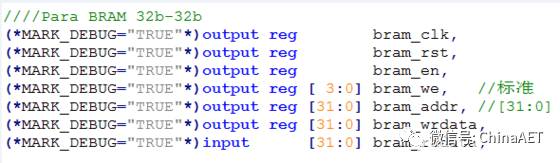

162FPGA實現基于Vivado的BRAM IP核的使用

Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 317

317

317

317怎樣單獨使用modelsim仿真xilinx呢?

直接在modelsim軟件內執(zhí)行.do文件進行仿真,不通過vivado調用modelsim,vivado僅用于生成IP核。

2023-12-04 18:26:34 477

477

477

477

如何實現ILA Cross Trigger

ILA Cross Triggering功能使得ILA核心之間、以及ILA核心與處理器(例如,AMD Zynq 7000 SoC)之間可以進行Cross Trigger。這個功能在你需要在不同時鐘域的兩個ILA核心之間觸發(fā),或者在處理器和ILA核心之間執(zhí)行硬件/軟件跨觸發(fā)時非常有用。

2023-11-30 10:17:59 503

503

503

503

HT for Web (Hightopo) 使用心得(5)- 動畫的實現

其實,在 HT for Web 中,有多種手段可以用來實現動畫。我們這里仍然用直升機為例,只是更換了場景。增加了巡游過程。 使用 HT 開發(fā)的一個簡單網頁直升機巡邏動畫(Hightopo 使用心得

2023-11-29 11:04:52 262

262

262

262

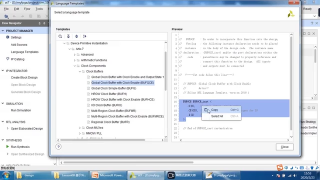

FPGA新IP核學習的正確打開方式

的情況時,總會遇到一些以前未曾接觸過的新內容,這些新內容會讓我們感到陌生和恐懼,不知道該如何下手。

那么今天以xilinx vivado 為例分享學習FPGA 新IP核的正確打開方式。

一、常規(guī)

2023-11-17 11:09:22

Vivado Design Suite 用戶指南:編程和調試

《Vivado Design Suite 用戶指南:編程和調試》 文檔涵蓋了以下設計進程: 硬件、IP 和平臺開發(fā) : 為硬件平臺創(chuàng)建 PL IP 塊、創(chuàng)建 PL 內核、功能仿真以及評估 AMD

2023-10-25 16:15:02 352

352

352

352

MySQL窗口函數使用心得

服務,實際驗證了一部分新功能,確實帶給我新的認知。接下來就分享給大家使用心得。 概述 Mysql是小編從事開發(fā)行業(yè)三年多來,接觸的最多的數據存儲介質,它屬于關系型數據庫,以開源免費、體積小、速度快、使用成本低等優(yōu)點,深得大部分用戶喜愛,同時也

2023-10-07 16:26:40 798

798

798

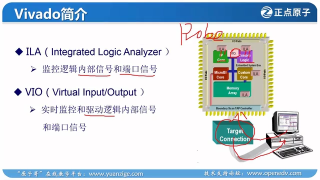

798集成邏輯分析儀(ILA)的使用方法

兩大主流廠商的軟件集成邏輯分析儀供使用,Altera的Quartus自帶SignalTap、Xilinx的Vivado自帶ILA邏輯調試工具。

2023-10-01 17:08:00 1443

1443

1443

1443

Vivado設計流程指導手冊

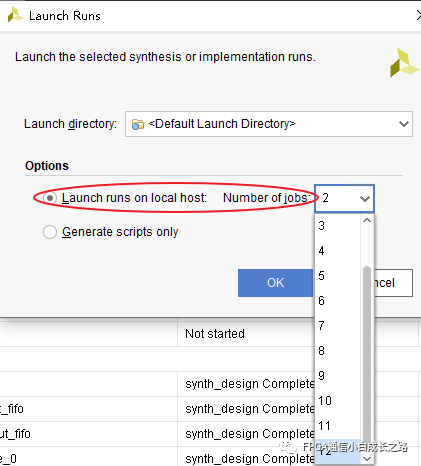

Vivado 設計分為 Project Mode 和 Non-project Mode 兩種模式,一般簡單設計中,我們常用的是 Project Mode。在本手冊中,我們將以一個簡單的實驗案例,一步一步的完成 Vivado的整個設計流程。

2023-09-20 07:37:39

vivado使用誤區(qū)與進階資料

Applications”,其實也是專為 Vivado 而設的一個部門,從 Vivado 的早期計劃開始,我和我的同事們就投入到了 Xilinx?和Vivado 的客戶們的推廣和支持中,我們給客戶做培訓

2023-09-20 06:31:14

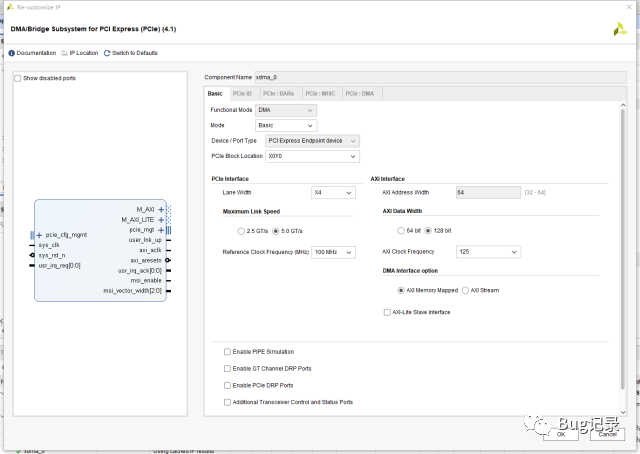

為什么說Vivado是基于IP的設計?

Vivado是Xilinx公司2012年推出的新一代集成開發(fā)環(huán)境,它強調系統(tǒng)級的設計思想及以IP為核心的設計理念,突出IP核在數字系統(tǒng)設計中的作用。

2023-09-17 15:37:31 1059

1059

1059

1059

【KV260視覺入門套件試用體驗】Zynq超強輔助-PYNQ配置,并使用XVC(Xilinx Virtual Cable)調試FPGA邏輯

\', 52054)

需要在vivado hardware中執(zhí)行的操作:

連接成功后,會出現下圖所示結果:

連接成功后,我們就可以使用ILA進行調試了。此處我們隨意設個觸發(fā)條件,計數器到100時觸發(fā)

2023-09-16 14:15:14

Vivado設計套件用戶:使用Vivado IDE的指南

電子發(fā)燒友網站提供《Vivado設計套件用戶:使用Vivado IDE的指南.pdf》資料免費下載

2023-09-13 15:25:36 3

3

3

3基于Xilinx FPGA的邊界掃描應用

上一篇文章,介紹了基于STM32F103的JTAG邊界掃描應用,演示了TopJTAG Probe軟件的應用,以及邊界掃描的基本功能。本文介紹基于Xilinx FPGA的邊界掃描應用,兩者幾乎是一樣。

2023-09-13 12:29:37 654

654

654

654

如何用Python實現Vivado和ModelSim仿真自動化?

我們在Windows系統(tǒng)下使用Vivado的默認設置調用第三方仿真器比如ModelSim進行仿真時,一開始仿真軟件都會默認在波形界面中加載testbench頂層的信號波形

2023-09-13 09:23:49 712

712

712

712

HT for Web (Hightopo) 使用心得(1)- 基本概念

本章主要介紹了 HT for Web 中的一些基本概念,包括:基礎數據 ht.Data、數據模型 ht.DataModel 和選擇模型 ht.SelectionModel、視圖組件以及序列化和反序列化。這些概念是 HT for Web 中最基礎的概念,幾乎在每次開發(fā)過程中都會用到。掌握它們的功能以及其互相之間的邏輯之后,對于后續(xù)的開發(fā)以及理解 HT for Web 的各個組件操作邏輯都有著非常重要的作用。

2023-09-11 10:45:28 458

458

458

458

Vivado使用指南

的的Vivado 工具把各類可編程技術結合在一起,能夠擴展多達1 億個等效ASIC 門的設計。Vivado設計界面如下圖:圖1. Vivado設計界面1.2芯片支持Vivado支持Xilinx的IC如下

2023-09-06 17:55:44

Vivado中BRAM IP的配置方式和使用技巧

FPGA開發(fā)中使用頻率非常高的兩個IP就是FIFO和BRAM,上一篇文章中已經詳細介紹了Vivado FIFO IP,今天我們來聊一聊BRAM IP。

2023-08-29 16:41:49 2604

2604

2604

2604

【KV260視覺入門套件試用體驗】+02.開發(fā)環(huán)境安裝Vitis/Vivado(zmj)

./xsetup

3.3軟件使用

軟件使用說明:

//------環(huán)境變量配置(Vitis的環(huán)境變量配置包括了Vivado)

source /tools/Xilinx/Vitis/2022.2

2023-08-27 21:22:34

嵌入式HLS 案例開發(fā)步驟分享——基于Zynq-7010/20工業(yè)開發(fā)板(1)

案例的使用說明,適用開發(fā)環(huán)境: Windows 7/10 64bit、Xilinx Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4

2023-08-24 14:40:42

10 8_工具篇_Vivado Simulator仿真軟件的使用 - 第7節(jié) #硬聲創(chuàng)作季

fpga硬件代碼Vivado

充八萬發(fā)布于 2023-08-18 07:46:51

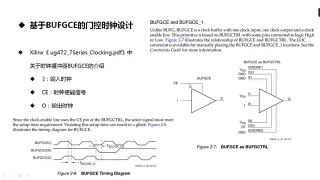

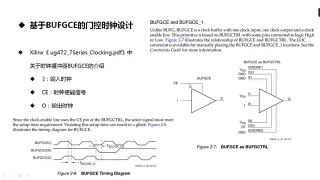

08 104 基于Xilinx BUFGCE原語的門控時鐘設計 - 第2節(jié) #硬聲創(chuàng)作季

軟件函數代碼Vivado

充八萬發(fā)布于 2023-08-18 04:59:59

08 6_工具篇_Vivado軟件的硬件調試:ILA的使用(第一講) - 第7節(jié) #硬聲創(chuàng)作季

軟件函數代碼Vivado

充八萬發(fā)布于 2023-08-18 04:28:35

如何利用ila(邏輯分析儀)調試nice?

仿真和生成mcs文件后運行的結果如下(仿真的結果和實際傳回的數據結果不同,并且相同的c程序前后兩次傳回的結果都不同),目前想用ila調試,看錯在那一步了,但ila一直不出波形,三種加debug的方法

2023-08-16 06:37:13

Arm Cortex-M1 DesignStart FPGA Xilinx版用戶指南

Cortex-M1 DesignStart?現場可編程門陣列-Xilinx版本包提供了一種在Xilinx Vivado設計環(huán)境中使用Cortex-M1處理器的簡單方法。

Cortex-M1處理器

2023-08-16 06:10:25

E203移植到自己開發(fā)板之后,ila抓取信號,IFU模塊輸出的ir和pc不對應的原因?

為mcs文件,load進去,在串口也打印出了相應的輸出內容。當用ila查看IFU模塊的兩個關鍵輸出信號時,發(fā)現和之前用testbench進行verilog仿真的輸出波形有差異。

按照官網給出的ppt上上解

2023-08-12 07:26:52

Arm Cortex-M3 DesignStart? FPGA Xilinx版用戶指南

Cortex-M3 DesignStart?現場可編程門陣列-Xilinx版封裝提供了一種在Xilinx Vivado設計環(huán)境中使用Cortex-M3處理器的簡單方法。

Cortex-M3處理器專為

2023-08-12 07:02:46

蜂鳥E203 V2的FPGA實現之后,上板測試想用ila抓取內部信號沒有波形是為什么?

RISC-V 蜂鳥E203平臺在黑金的AX7050上移植搭建,想查看IFU模塊的內部信號,于是調用ila查看,卻發(fā)現沒有任何波形輸出,FPGA實現是可以正常run編譯之后可執(zhí)行文件的。圖1是用ila

2023-08-12 06:25:08

vivado軟件和modelsim軟件的安裝方法

本文詳細介紹了vivado軟件和modelsim軟件的安裝,以及vivado中配置modelsim仿真設置,每一步都加文字說明和圖片。

2023-08-07 15:48:00 1478

1478

1478

1478

如何實現基于FPGA Vivado的74系列IP封裝呢?

雙擊桌面圖標打開Vivado 2017.2,或者選擇開始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2023-07-30 09:39:11 399

399

399

399

Xilinx Vivado DDS IP使用方法

DDS(Direct Digital Frequency Synthesizer) 直接數字頻率合成器,本文主要介紹如何調用Xilinx的DDS IP核生成某一頻率的Sin和Cos信號。

2023-07-24 11:23:29 1720

1720

1720

1720

Vivado調用Modelsim仿真

Modelsim是十分常用的外部仿真工具,在Vivado中也可以調用Modelsim進行仿真,下面將介紹如何對vivado進行配置并調用Modelsim進行仿真,在進行仿真之前需要提前安裝Modelsim軟件。

2023-07-24 09:04:43 1817

1817

1817

1817

vivado創(chuàng)建工程流程

vivado的工程創(chuàng)建流程對于大部分初學者而言比較復雜,下面將通過這篇博客來講解詳細的vivado工程創(chuàng)建流程。幫助自己進行學習回顧,同時希望可以對有需要的初學者產生幫助。

2023-07-12 09:26:57 1098

1098

1098

1098

在Vivado中使用邏輯分析儀ILA的過程

FPGA綜合出來的電路都在芯片內部,基本上是沒法用示波器或者邏輯分析儀器去測量信號的,所以xilinx等廠家就發(fā)明了內置的邏輯分析儀。

2023-06-29 16:08:56 2536

2536

2536

2536

用 TCL 定制 Vivado 設計實現流程

今天推出Xilinx已發(fā)布的《Vivado使用誤區(qū)與進階》系列:用TCL定制Vivado設計實現流程。

上一篇《Tcl 在 Vivado 中的應用》介紹了 Tcl 的基本語法以及如何利 用 Tcl

2023-06-28 19:34:58

如何讀懂FPGA開發(fā)過程中的Vivado時序報告?

FPGA開發(fā)過程中,vivado和quartus等開發(fā)軟件都會提供時序報告,以方便開發(fā)者判斷自己的工程時序是否滿足時序要求。

2023-06-26 15:29:05 530

530

530

530

如何在Vivado中添加時序約束呢?

今天介紹一下,如何在Vivado中添加時序約束,Vivado添加約束的方法有3種:xdc文件、時序約束向導(Constraints Wizard)、時序約束編輯器(Edit Timing Constraints )

2023-06-26 15:21:11 1834

1834

1834

1834

如何使用Python腳本調試賽靈思PCIe設計?

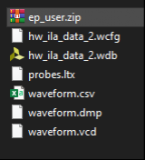

現在,您不僅可以使用 Python 腳本執(zhí)行調試分析,更重要的是,借由 Vivado ILA 所生成的 ILA 文件可以進一步簡化此操作。通過將 *.ila 擴展名重命名為 *.zip 然后將生成的文件解壓,即可將其轉換為 CSV 文件。

2023-06-26 09:20:46 625

625

625

625

如何讀懂Vivado時序報告

FPGA開發(fā)過程中,vivado和quartus等開發(fā)軟件都會提供時序報告,以方便開發(fā)者判斷自己的工程時序是否滿足時序要求。

2023-06-23 17:44:00 531

531

531

531

為EBAZ4205創(chuàng)建Xilinx Vivado板文件

電子發(fā)燒友網站提供《為EBAZ4205創(chuàng)建Xilinx Vivado板文件.zip》資料免費下載

2023-06-16 11:41:02 1

1

1

1第二周開始啦!分享面包板使用心得拿豪禮!

相信每個進行過電子電路設計的人, 都需要不同的工具輔助, 才能更高效地完成項目。 面包板是用于電子電路原型搭設的理想工具。 每個DIY愛好者、電子工程師、學生… 在完成項目的過程中應該都曾使用過它。 (無焊面包板 DKS-BBOARD6.5 ) 面包板的歷史: 面包板,也被稱為原型板或無焊面包板,是電子愛好者和專業(yè)人士的重要工具。它是一種用于原型制作電子電路的設備,無需焊接。 最初,對于從事電子行業(yè)的工程師來說,他們并沒有使用我們稱之為

2023-06-08 18:15:03 281

281

281

281

無線通信中的優(yōu)化問題+matlab中cvx的使用心得

學習期間主要做的是無線通信領域的資源分配問題,特別針對的是類似香農信道容量的 log形式的優(yōu)化問題的仿真,有

射頻通信的,也有無線光通信的。在使用cvx求解的過程中也有一點兒心得體會,在這里

2023-05-30 14:21:20 2

2

2

2Xilinx FPGA遠程調試方法(二)

上篇主要是分享了Vivado編譯軟件遠程調試的方法。杰克使用Vivado軟件進行遠程連接,主要是用于固化程序以及FPGA(PL端)的異常排查。而本篇主要內容是對使用Vitis軟件遠程調試的方法進行總結和分享。

2023-05-25 14:36:58 1685

1685

1685

1685

Vivado Design Suite 用戶指南介紹

DFX 是由多個部分組成的綜合性解決方案。這些要素包括:AMD 芯片能進行動態(tài)重配置,Vivado 軟件流程支持編譯設計(從 RTL 到比特流),以及各種補充性功能特性(如 IP)。

2023-05-18 09:47:24 480

480

480

480

Vivado綜合參數設置

如果你正在使用Vivado開發(fā)套件進行設計,你會發(fā)現綜合設置中提供了許多綜合選項。這些選項對綜合結果有著潛在的影響,而且能夠提升設計效率。為了更好地利用這些資源,需要仔細研究每一個選項的功能。本文將要介紹一下Vivado的綜合參數設置。

2023-05-16 16:45:50 1856

1856

1856

1856

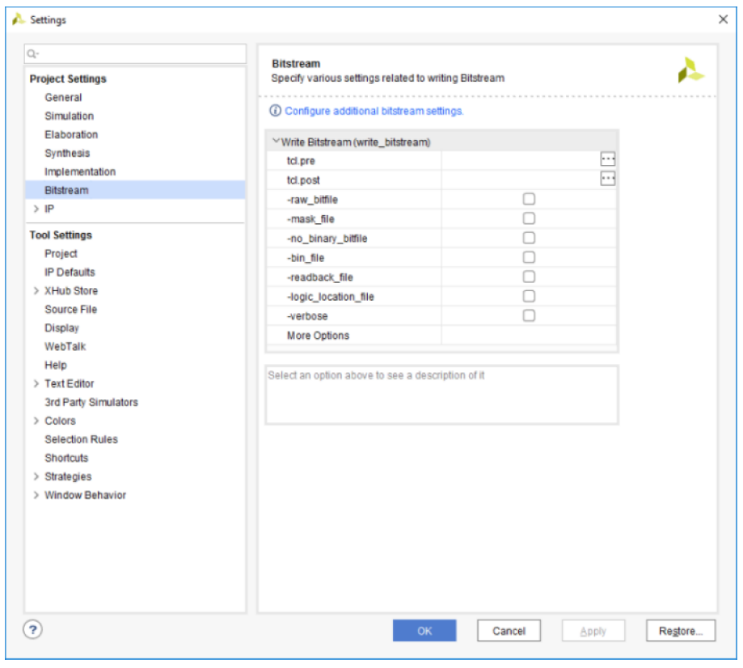

Vivado布線和生成bit參數設置

本文主要介紹Vivado布線參數設置,基本設置方式和vivado綜合參數設置基本一致,將詳細說明如何設置布線參數以優(yōu)化FPGA設計的性能,以及如何設置Vivado壓縮BIT文件。

2023-05-16 16:40:45 2955

2955

2955

2955

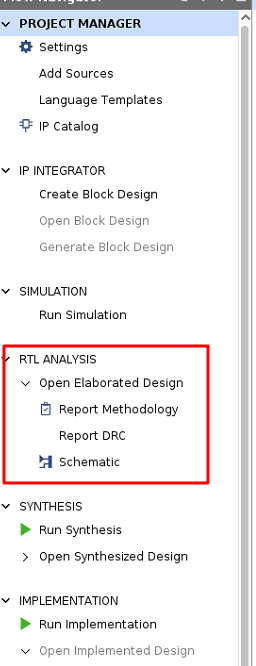

簡述Vivado中的Elaborate的作用

在Vivado的界面中,有個RTL ANALYSIS->Open Elaborated Design的選項,可能很多工程師都沒有使用過。因為大家基本都是從Run Synthesis開始的。

2023-05-05 16:00:18 803

803

803

803

在Vivado中實現ECO功能

關于 Tcl 在 Vivado中的應用文章從 Tcl 的基本語法和在 Vivado 中的 應用展開,繼上篇《用 Tcl 定制 Vivado 設計實現流程》介紹了如何擴展甚 至是定制 FPGA

2023-05-05 15:34:52 1612

1612

1612

1612

Vivado生成IP核

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因為工程中很多IP核不能用所以在重新生成過程中發(fā)現了這個問題,還請大神告知是怎么回事?

2023-04-24 23:42:21

PLC報警使用心得

隨著科學技術的不斷發(fā)展,對生產的把控越來越精細,可視化程度越來越高。在項目中使用HMI或上位機來獲取設備的運行狀況已經越來越普遍。在西門子TIAProtal中,支持了HMI報

警、Program_Alarm和ProDiag 3種方式來獲得信息。

第一種HMI報警是在觸摸屏或者上位機(WinCC Advcend/Professional)上組態(tài)。基本步驟是先創(chuàng)建報警變量再組態(tài)報警文本,由HMI定時輪詢變量,通過對該變量值的變化監(jiān)控而觸發(fā)報警。

這種方式的報警消息配置簡單,但效率比較低,工作量

2023-04-18 09:59:17 0

0

0

0Vivado邏輯分析儀使用教程

,確認無誤后直接點擊finish即可,如下圖所示:在“Debug”子窗口中的“Debug Cores”選項卡中,可以看到Vivado已經添加了ILA IP核,并且“Unassigned Debug

2023-04-17 16:33:55

Tcl在Vivado中的應用

Xilinx的新一代設計套件Vivado相比上一代產品 ISE,在運行速度、算法優(yōu)化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言 XDC 以及腳本語言 Tcl 的引入則成為

2023-04-15 09:43:09 956

956

956

956Vivado 開發(fā)軟件下板驗證教程

及打算進階提升的職業(yè)開發(fā)者都可以有系統(tǒng)性學習的機會。系統(tǒng)性的掌握技術開發(fā)以及相關要求,對個人就業(yè)以及職業(yè)發(fā)展都有著潛在的幫助,希望對大家有所幫助。本次帶來Vivado系列,使用Vivado開發(fā)軟件下板

2023-04-14 20:18:05

Xilinx FPGA Vivado 開發(fā)流程

及打算進階提升的職業(yè)開發(fā)者都可以有系統(tǒng)性學習的機會。系統(tǒng)性的掌握技術開發(fā)以及相關要求,對個人就業(yè)以及職業(yè)發(fā)展都有著潛在的幫助,希望對大家有所幫助。本次帶來Vivado系列,Vivado開發(fā)軟件

2023-04-13 15:18:52

Vivado中常用TCL命令匯總

Vivado是Xilinx推出的可編程邏輯設備(FPGA)軟件開發(fā)工具套件,提供了許多TCL命令來簡化流程和自動化開發(fā)。本文將介紹在Vivado中常用的TCL命令,并對其進行詳細說明,并提供相應的操作示例。

2023-04-13 10:20:23 1544

1544

1544

1544Vivado 2019.2 安裝教程

需求設計出一款比較適合自家芯片的綜合器。本文主要介紹 Xilinx FPGA,下面介紹 Xilinx FPGA 的綜合工具 Vivado 軟件。接下來為大家介紹 Vivado2019.2 的安裝教程。1

2023-04-12 22:24:17

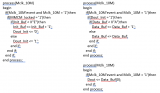

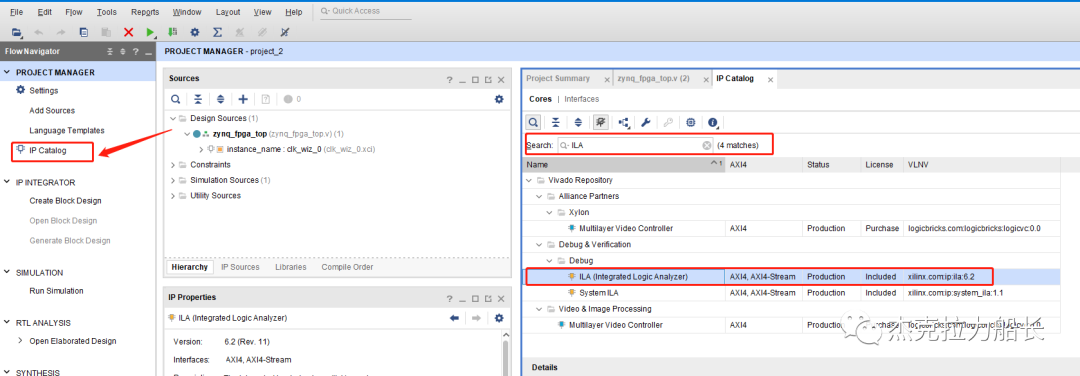

Vivado在線調試方法-Vivado內嵌邏輯分析儀器的使用

1,方法1-ILA IP核I、點擊“IP Catalog”,在搜索框中搜索ila,雙擊ILA的IP。設置模塊的名稱,采樣信號的數量,采樣深度。設置采樣信號的寬度,需要采集led和count信號,位寬

2023-04-06 21:48:03

Xilinx下載器

下載方案:HS2 二代高速下載方案,下載速度:最大 30Mhz通信方式:USB,下載接口:JTAG 14P 標準接口,支持開發(fā)環(huán)境:ISE、Vivado,工作電壓:5V(USB 供電),工作電流:56mA@5V,工作溫度:-40℃~+85℃

2023-03-28 13:06:17

Xilinx FPGA獨立的下載和調試工具LabTools下載、安裝、使用教程

Xilinx LabTools工具是Xilinx FPGA單獨的編程和調試工具,是從ISE或Vivado中獨立出來的實驗室工具,只能用來下載FPGA程序和進行ILA調試,支持所有的FPGA系列,無需

2023-03-28 10:46:56 4751

4751

4751

4751Xilinx Platform Cable USB

支持所有Xilinx器件下載 包括FPGA CPLD ISP Configuration PROM 下載接口電壓:5V 3.3V 2.5V 1.8V 1.5V

2023-03-24 15:06:53

電子發(fā)燒友App

電子發(fā)燒友App

評論