?????? Cadence設計系統公司,日前宣布Giantec Semiconductor Corp.已采用Cadence Virtuoso統一定制模擬(IC6.1)以及Encounter統一數字流程生產其混合信號芯片。Giantec最近采用Cadence軟件設計并成功流片了一款用于低功耗微控制器的存儲器產品,這款低功耗微控制器應用于智能卡、智能電表和消費電子產品。使用Cadence Virtuoso統一定制/模擬流程開發其混合信號設計,Giantec實現了30%的效率提升。

“當今混合信號芯片的復雜性需要一種統一的方法進行設計實現與驗證,Cadence與客戶及合作伙伴密切合作,提供端到端的流程進行硅實現。”Cadence解決方案營銷部主管Qi Wang說,“我們發現越來越多的證據表明這種方法對于復雜混合信號設計的成功至關重要,比如來自Giantec的高性能存儲器產品。”

Giantec選擇Cadence統一Virtuoso與Encounter流程用于這種高性能設計,突顯了對于上市時間緊迫及功耗/性能目標高的復雜芯片設計,使用全局化綜合EDA流程有著獨特的技術與商業優勢。

“Cadence研發部門與我們緊密合作,解決了我們的特殊需要,而且通過使用Cadence Virtuoso技術,能夠實現30%的效率提升。”Giantec設計部副總經理Leo Li說,“使用Cadence的技術,為我們的混合信號設計帶來了更完整的解決方案,效率能夠顯著提高。”

此外,Giantec已采用通過產品驗證基于SKILL的工藝設計工具包(PDK)作為標準。

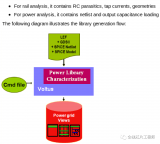

Cadence的混合信號設計方法利用一種統一的方法學,模擬與數字團隊在早期設計規劃、前端設計、功能驗證、物理實現與封裝等方面承擔著共同的責任。這種由上至下的方法可以提高定制/模擬與數字工程團隊的共同效率,有助于管理層實現積極的產品上市時間目標,并提高盈利性。

電子發燒友App

電子發燒友App

評論