我國靶場測量、工業控制、電力系統測量與保護、計算、通信、氣象等測試設備均采用國際標準IRIG-B格式的時間碼(簡稱B碼)作為時間同步標準。B碼是一種串行的時間格式.分為直流碼(DC碼)和交流碼(AC碼)兩種,其格式和碼元定時在文獻中有詳細描述。本文介紹一種基于FPGA并執行IRIG-B標準的AC/DC編碼技術,與基于MCU或者DSP和數字邏輯電路實現的編碼方法相比,該技術可以大大降低系統的設計難度,降低成本,提高B碼的精確性和系統靈活性。

在此,組合GPS引擎和FPGA,得到B碼的編碼輸出,直接采用GPS引擎的100 pps信號觸發輸出B碼的每個碼元,利用從100 pps中恢復的1 pps信號提供B碼的時間參考點。DC編碼和AC數字調制均由純硬件邏輯通過查找表實現,它能使每個碼元的上升沿都非常精準,都可以作為百分秒的時間參考點。而計時鏈的預進位功能則保證了絕對時間的精確,不僅可以滿足實時系統對時間同步,還可以實現多節點的數據采集嚴格同步,為分析和度量異步發生的事件提供有力的支持。

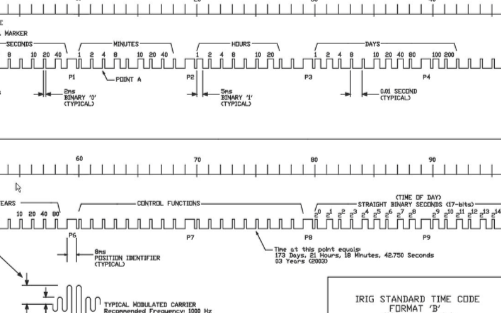

1 IRIG-B編碼格式

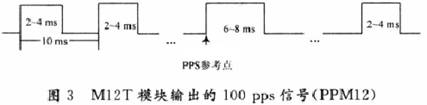

IRIG標準規定的B格式碼如圖1所示,每秒鐘發1次,每次100個碼元,包含1個同步參考點(P,脈沖的上升沿)和10個索引標記。碼元寬度為10 ms,用高電平寬度為8 ms的脈沖表示索引標記,用寬度為5 ms的脈沖表示邏輯1,用寬度為2 ms的脈沖表示邏輯0。

如圖1所示,交流碼的載波是1 kHz正弦信號,幅度變化峰-峰值范圍為0.5~1 0 V。調制比為U1/U0=1/6~1/2,即邏輯1是5個幅度為U1的1 kHz正弦信號。邏輯0是2個幅度為己U1的1 kHz正弦信號,索引標記是8個幅度為U1的1 kHz正弦信號,其他時間是幅度為U0的1 kHz正弦信號。

2 系統方案

2.1 系統原理框圖

設計授時系統需要一個精準時基。在此利用精密授時型GPS引擎M12T作為系統時基,利用AlteraFPGA檢測M12T輸出的百分秒(100 pps)同步信號和經串口輸出的絕對時間信號,編碼后輸出到DC/AC接口模塊,再輸出到物理鏈路,系統結構圖如圖2所示。

上述系統首先實現了B碼直流編碼,而后在直流碼的基礎上實現交流調制,以得到交流碼,同時提供恢復每秒脈沖數輸出和隔離RS 232串行口輸出且符合Motorola格式的時間碼,以及數碼管的時間顯示。時間顯示部分用FPGA實現比較簡單,下文不再詳述。

2.2 GPS授時模塊M12T

M12接收器是Motorola公司優秀ONCORE家族中的新成員,廣泛用于各類定位、導航、授時設備中,擁有全GPS行業內最快的初次定位時間和重捕獲衛星的時間。M12T是針對GPS授時推出的定時精度更高的增強型產品。M12T具有12個并行通道,可同時跟蹤12顆衛星,重捕獲時間小于1.O s。當擁有當前天歷、位置、時間和星歷數據時。首次定位時間TTFF<15 s。在位置保持狀態時,定時精度(1 pps或100 pps)小于12 ns。

2.3 FPGA和DAC

FPGA采用Altera CycloneⅡEPC2C5T144,該芯片有4 608個LE,26個M4K.兩個模擬鎖相環。DAC采用單通道、單電源、自帶基準的MAX5712。MAX5712是微型引腳,12 b解析度,片上精密輸出放大器提供滿擺幅輸出。MAX5712用兼容SPITM/QSPITM/MICROWIRETM和DSt標準接口的3線串行接口。所有輸入都兼容于CMOS邏輯,并經過施密特觸發器緩沖,允許直接接光電耦合器。MAX5712含有上電復位(POR)電路,確保上電時DAC處于零電壓輸出狀態。

3 時鐘模塊實現

3.1 基準時刻和索引脈沖的提取

要保證B碼每個碼元的上升沿時刻準確,需要100 pps的精確時基和pps的參考點。一般的做法是用pps作為基準,每個碼元的起點由前兩個秒脈沖的間隔等分得到。這種方法使用上一時刻來預測下一秒,每秒脈沖有抖動時會導致最后一個碼元寬度不足或超過10 ms,這將無法利用B碼來實現時間同步和數據等間隔同步的采集。本文直接使用M12T產生的100 pps信號作為每個碼元的起始時刻,然后再從100 pps信號中恢復出1 pps。由于B碼參考標記Pr=1 pps的上升沿,所以這種方法既保證Pr的準確性,又保證各個碼元和索引標記時刻的準確性。在有等間隔同步數據采樣要求的場合,可使用每個B碼碼元的上升沿校準本地時基,確保采樣同步和時間同步。

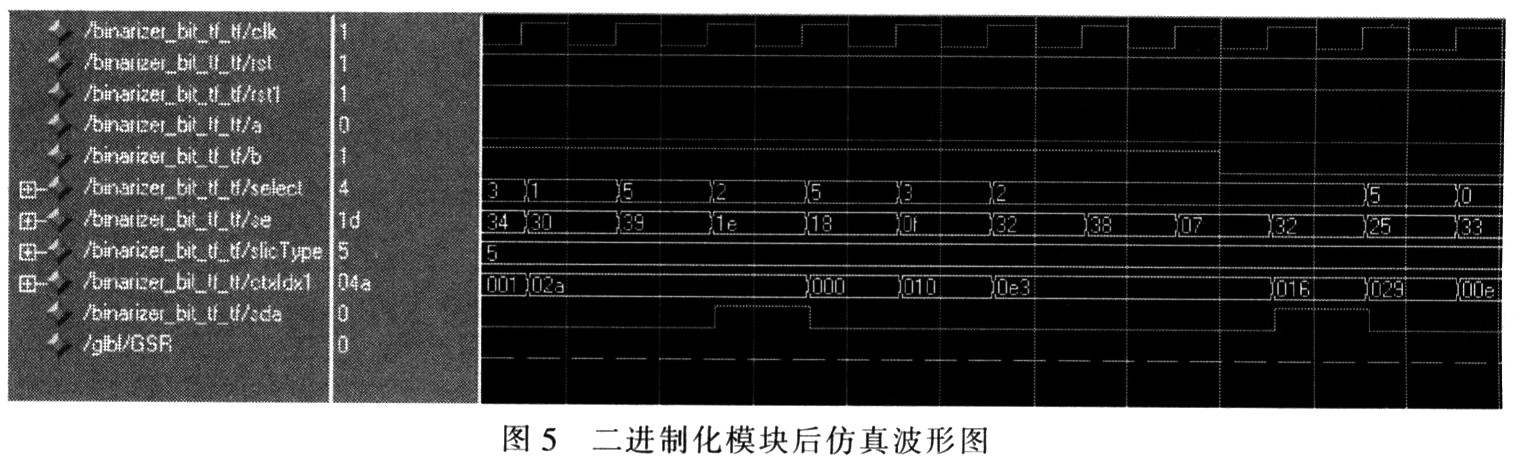

M12T輸出的100 pps信號(以下稱PPMl2)如圖3所示,每個脈沖的上升沿時刻準確,周期10 ms,在pps的參考點,脈沖寬度為6~8 ms,其他時刻2~4 ms,脈沖寬度不是關注的重點。

B碼的每個碼元恰好與上述100 pps信號對應。首先在FPGA中構建一個模100的碼元計數器MMH和一個高電平脈沖寬度檢測器,通過下面的方法和步驟可以恢復pps。

(1)在PPMl2信號的上升沿復位寬度檢測器,高電平計時,在下降沿停止并輸出Tb;

(2)在PPM12下降沿檢查Tb,當6 ms

if MMH=99 then MMH=O

else MMH=MMH+1

(3)在PPMl2信號的上升沿檢查MMH,如果MMH=0,則當前脈沖的上升沿是參考點Pr,觸發輸出8 ms高電平脈沖作為pps信號,重復步驟(1)~(3),在PPM12信號上升沿檢查MMH;如果MMH的個位為9或者MMH=0,則當前脈沖標記為索引脈沖,即輸出8 ms高電平。

3.2 絕對時間獲取

通過在FPGA上構建一個UART與M12T互連。為了簡化FPGA對M12T的配置和輸出時間的獲取,將UART分成兩部分設計,即發送模塊txmit和接收模塊rcvr。發送模塊用一個M4K設計一個512×8 FIFO,在系統復位后的若干個時鐘,利用一個狀態機將M12T的配置數據寫入FIFO;然后通過txmit模塊配置M12T,配置結束后,UART模塊將M12T的時間碼轉發到外部RS 232接口,同時可以轉發外部接口的配置數據到M12T。接收模塊采用寄存器模式,只接收M12T發來的絕對時間信息,這樣后面的編碼模塊可以直接使用這些時間信息。做法如下:設計一個接收計數器rx_ count,每接收一個字節計數器自加,并根據rx_count決定是否保存時間碼。由于M12T每秒中發送一幀,故在檢測到pps時復位該計數器。

M12T在每個1 pps的上升沿過后送出當前時間,而FPGA通過UART接收到時間時,B碼當前幀已經啟動,據此形成的B碼要等下一個pps參考點之后才可以發送,所以對接收的時間要進行預進位處理。

本文在FPGA預處理部分設計了一個RTC計時鏈,在每個1 pps的上升沿.計時鏈向上進位,編碼模塊從RTC計時鏈取絕對時間。從UART接收到新的時間后,如果該時間與計時鏈的值有差異,則將通過計時鏈的同步置數接口修正計時鏈的值。同時計時鏈負責把M12T的二進制時間轉換成壓縮的BCD碼,還要根據當前接收到的年月日,計算當天是全年中的第幾天,即IRIG-B碼中的Day字段,而且在預加1 S和轉換時間格式時,要注意閏年和月大和月小對Day字段的影響。

4 IRIG-B編碼模塊實現

4.1 IRIG-B DC編碼模塊

分析B碼可以發現,秒的最低位出現在MMH=1處,分的最低位出現在MMH=10處,小時的最低位出現在MMH=20處,依次類推。按照圖1,容易得出時間寄存器輸出時刻和碼元計數器MMH之間的關系。由于碼元周期固定為10 ms,可以這樣實現編碼,定義一個模10的計數器MML和邏輯向量CMP(9 down to0)來表征一個碼元在10 ms的狀態。MML每ms加1,同時根據MML的值,選擇CMP的一位更新輸出狀態,步驟如下:

(1)構建模10計數器MML,以及一個1 ms定時器;

(2)在PPM12信號的上升沿復位MML和1 ms定時器;

(3)1 ms定時器溢出時,MML加1;

(4)根據MML和CMP輸出編碼信號IRIG_B_OUT,即IRIG_B_OUT=CMP(MML);

(5)在PPM12的上升沿根據第3.1節所得碼元計數器MMH重新加載CMP

算法VHDL描述如下:

在上述VHDL編碼的實現中,MSCLK為1 ms計數脈沖.同步于PPM12信號的上升沿。CMP的輸出值由函數IRIG_B根據輸入參數決定,若為0,則輸出“0000000011”,對應2 ms;若為1則輸出“0000011111”,對應5ms。在索引脈沖和參考點Pr處,CMP取值“0011111111”,對應8 ms。而最終的編碼輸出IRIG_B_0UT在每個1 ms脈沖的上升沿,根據CMP(MML)的值決定為高或為低。

4.2 IRIG-B AC編碼模塊

4.2.1 數字調制原理

按照奈奎斯特抽樣定理,只要抽樣頻率高于2倍信號的最高頻率,則整個連續信號就能完全用它的抽樣值來代表。使用抽樣值構成的序列經DAC和低通濾波后即可恢復原來的連續信號。

若對頻率為f的正弦波抽樣N次(N>2f),并在T=1/f內通過DAC等間隔輸出N次抽樣值,則低通濾波后可恢復原始正弦信號。各個采樣點值為:

4.2.2 正弦查找表

這里給出利用查找表實現交流數字調制的方法。在獲得IRIG-B的直流編碼后,將該信號導入到數字調制模塊,即可獲得交流編碼。對正弦信號進行100次等間隔抽樣,對式(2)使用實際的增益和直流偏移,可得式(3)。據此獲得查找表。

式中:N=100為采樣率;k=O,1,2,…,N-1;Ck對應第k次抽樣獲得的值;A0為保證輸出信號為單極性而設置的初始直流偏移;Ac為考慮調制比和DAC滿幅度碼值的系數。

由于交流信號頻率為1 kHz,周期為T=1 ms,若在1 ms內將上述抽樣值等間隔輸出到DAC,即可獲得1 kHz的調制信號。

本文使用MAX5712和單電源rail-rail運放AD8601構成濾波器。在MAX5712滿幅輸出時,C=4 095(12 bit DAC),選擇調制比為1∶5。綜合考慮,在最大輸出時,不能使DAC輸出到達運放的上軌,最低輸出時,DAC輸出應高于運放的下軌,所以選取A0=C/2+200=2 248。對應邏輯0,Ac=461;對應邏輯1,Ac=1 844。根據上述原則計算出的正弦查找表如表1所示。

實際使用時,應根據使用DAC的解析度、運放的動態范圍以及采樣率及調制比確定上式中的參數。

4.2.3 DAC接口

實際使用時應根據DAC的不同,在FPGA中構建不同的數字接口。MAX5712需要在FPGA實現一個SPI接口,結構如圖4所示。接口控制部分提供一個16 b寫端口,可以接收數據。在寫使能wren為高時,接口上的數據寫入內部并行保持寄存器。在LDAC脈沖的上升沿,并行寄存器THR的內容寫入移位寄存器,同時啟動時鐘邏輯。在輸出時鐘作用下,數據從Dout輸出到DAC,在SPI_CS的后沿,DAC啟動轉換輸出與當前編碼相匹配的模擬量。

4.2.4 交流調制方法

把按照第4.2.1節方法生成的正弦查找表生成Altera mif文件,再例化一個M4K ROM,使用上述文件作為ROM的初始化文件。建立一個周期為10μs的定時器和一個地址計數器。地址計數器和定時器在B碼直流信號的變化沿復位,定時器溢出后啟動地址計數器。或者把邏輯0對應的查找表放在ROM的上半部,如果把邏輯1對應的查找表放在ROM的下半部,且輸入的直流B碼信號作為地址的高位,則此時刻對應的ROM輸出即為DAC的調制輸出,ROM查找表VHDL的代碼實現如下:

其中:B為來自編碼器中IRIG-B的直流編碼;AQC為地址計數器;ddata為輸出到DAC的數字調制輸出。由于查找表是按照對正弦信號做100次等間隔采樣形成的,交流載波為1 kHz。所以AQC每隔10μs自加1,順序輸出100個編碼值,在B碼的每個變化邊沿復位。

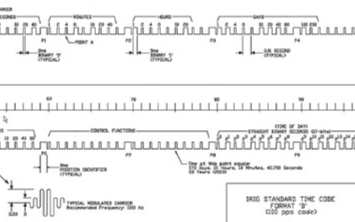

按上述方法設計的數字調制模塊,用示波器測得輸出波形如圖5所示。

圖5中,通道1(從上至下第一個信號)為M12T輸出的100pps信號PPM12;通道2(從上至下第三個信號)為IRIG-B的直流編碼輸出信號;通道3(從上至下第二個脈沖)為從PPM12信號中恢復的每秒脈沖數信號;通道4(最下面的波形)為IRIG-B編碼的交流輸出波形。圖5中示波器的觸發點即為B碼參考點Pr。

4.3 IRIG-B編碼輸出

4.3.1 直流碼輸出

為了保證輸出信號的邊沿和抗干擾,將第4.1節得到的TTL電平B碼信號和秒脈沖經高速光耦隔離,輸出電路如圖6所示。

圖6中,輸入信號IRIG-B為第4.1節所述FPGA編碼模塊輸出的直流編碼信號;pps為FPGA從M12T的100 pps信號中恢復的秒脈沖信號;D350和D351實現了TTL/RS485的電平轉換。

4.3.2 模擬調制電壓輸出

IRIG-B編碼的交流碼輸出電路如圖6所示。將第4.2.3節所述數字調制信號通過DAC接口輸出到MAX5712上進行D/A轉換,經過AD8601濾除高次諧波后,再用電容耦合到由晶體管Q301構成的電壓放大器中,然后經600∶600的隔離變壓器輸出。

5 結語

利用FPGA和M12T授時型GPS內核構成的IRIG-B編碼模塊采用M12T的100 pps信號觸發IRIG-B編碼器,使得編碼輸出的每個碼元上升沿均與GPS模塊嚴格一致,每個碼元間隔嚴格相等,而且每個碼元的上升沿均可作為同步參考點。利用FPGA的并發處理能力,使得系統實時性好。本文介紹的基于查找表的B碼編碼方法和通過查找表的數字調制方法具有占用資源小,設計簡單,調制輸出高次諧波小,信號邊沿穩定等特點。

經過軟件仿真和系統測試。本文實現的B碼編碼器中DC碼參考點Pr和M12T GPS模塊的pps參考點的時間誤差小于20 ns。與絕對時間參考點之間的誤差小于40 ns,AC碼與DC碼之間的延遲為100 ns。利用上述方法實現的模塊已經成功地應用在我公司的通信管理機和同步時間服務器中,現場運行結果穩定、準確、可靠。

電子發燒友App

電子發燒友App

評論