關(guān)鍵詞: 單片機(jī) 擴(kuò)展 方法 串行口摘要:1 引言在研究采場(chǎng)瓦斯積聚模擬試驗(yàn)臺(tái)的過(guò)程中,筆者設(shè)計(jì)了主從式多機(jī)采控系統(tǒng)結(jié)構(gòu)。主從式多機(jī)控制系統(tǒng)是實(shí)時(shí)控制系統(tǒng)中較為普遍的結(jié)構(gòu)形式,它具有可靠性高,結(jié)構(gòu)

2015-09-02 14:47:12

51單片機(jī)串行口中斷的使用初始化中斷服務(wù)程序主程序初始化 void SCON_init(){SCON = 0x50; //0101 0000TMOD = 0x20; //0010 0000TH1

2021-11-19 07:49:42

的單片機(jī)串行口通信教程,第一次發(fā)帖,不到位的地方,請(qǐng)多多見(jiàn)諒。1.下載虛擬串口軟件(Virtual Serial Port Driver),讓proteus仿真時(shí)串口能與串口助手虛擬連接;2.虛擬串口

2018-10-26 18:46:12

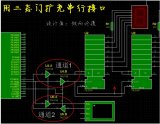

兩片單片機(jī)利用串行口進(jìn)行串行通信:串行通信的波特率可從鍵盤(pán)進(jìn)行設(shè)定,可選的波特率為1200、2400、4800和9600bit/s這個(gè)是原理圖只缺程序,求各位大神寫(xiě)下程序,如果成功

2015-06-07 22:56:41

本帖最后由 diangongshi 于 2011-12-15 18:13 編輯

工程師經(jīng)常碰到需要多個(gè)串口通信的時(shí)候,而低端單片機(jī)大多只有一個(gè)串行口,甚至沒(méi)有串口。這時(shí)候無(wú)論是選擇高端芯片

2011-12-15 18:11:56

51單片機(jī)的串行接口介紹串行口結(jié)構(gòu)設(shè)置工作方式(串行口控制寄存器SCON)設(shè)置波特率 51單片機(jī)內(nèi)部集成1~2個(gè)可編程通用異步串行通信接口(即UART),采用全雙工制式。該通信接口有四種工作方式

2021-11-18 07:37:22

本帖最后由 luna 于 2011-3-3 11:28 編輯

在以單片機(jī)為核心的多級(jí)分布式系統(tǒng)中,常常需要擴(kuò)展單片機(jī)的串行通信口,本文分別介紹了基于SP2538專用串行擴(kuò)展芯片及INTE18251的兩種串行口擴(kuò)展方法,并給出了實(shí)際的硬件電路原理及相應(yīng)的通信程序段。

2011-03-02 12:13:46

實(shí)驗(yàn)原理51 單片機(jī)的串行口是一個(gè)可編程的全雙工的通信接口,具有 UART(通用異步收發(fā)器)的全部功能,能同時(shí)進(jìn)行數(shù)據(jù)的發(fā)送和接收,也可以作為同步移位寄存器使用。51 單片機(jī)的串行口主要有兩個(gè)獨(dú)立

2021-07-16 07:06:02

51單片機(jī)定時(shí)計(jì)數(shù)器溢出率計(jì)算和串口的波特率之間的關(guān)系51單片機(jī)的四種串行口工作模式設(shè)置

2021-03-01 06:46:30

單片機(jī)雙機(jī)通信一、實(shí)驗(yàn)?zāi)康亩?shí)驗(yàn)內(nèi)容三、實(shí)驗(yàn)步驟四、C代碼如下五、實(shí)驗(yàn)結(jié)果六、實(shí)驗(yàn)體會(huì)一、實(shí)驗(yàn)?zāi)康恼莆?9C51單片機(jī)異步串行口的通信原理和編程掌握串行口工作方式1的使用及其波特率的計(jì)算二、實(shí)驗(yàn)

2021-11-09 07:32:14

波特率波特率計(jì)算三、51單片機(jī)串行口結(jié)構(gòu)概況1、控制寄存器SCON表格1:位序號(hào)與位格式表格2:串口工作方式表格3:其他位功能2、時(shí)序圖時(shí)序圖工作步驟表格3、例程:串口調(diào)試助手通信4、例程:串口實(shí)現(xiàn)printf...

2021-11-22 06:11:59

如何用簡(jiǎn)單的C語(yǔ)言編串行口

2012-12-22 16:22:48

目錄前言一、串行口結(jié)構(gòu)與相關(guān)寄存器1、串行口結(jié)構(gòu)2、相關(guān)SFR二、串行口的工作方式三、串行口的初始化前言串行口知識(shí)簡(jiǎn)單整理一、串行口結(jié)構(gòu)與相關(guān)寄存器1、串行口結(jié)構(gòu)(1)8051系列單片機(jī)片上有

2022-01-19 07:59:14

MCS-51內(nèi)部除含有4個(gè)并行I/O接口外,還有一個(gè)串行通信I/O口,通過(guò)該串行口可以實(shí)現(xiàn)與其他計(jì)算機(jī)系統(tǒng)的串行通信。本章通過(guò)實(shí)訓(xùn)完成一個(gè)串行通信實(shí)例,在介紹關(guān)于串行通信的基礎(chǔ)知識(shí)后,詳細(xì)論述MCS-51的串行口及其通信應(yīng)用。

2009-09-30 11:07:50

實(shí)驗(yàn)?zāi)康暮腿蝿?wù)目的:利用“模塊化單片機(jī)教學(xué)實(shí)驗(yàn)平臺(tái)”,加深對(duì)單片機(jī)的串行口的理解。任務(wù):利用單片機(jī)的串行口完成程序設(shè)計(jì)。實(shí)驗(yàn)內(nèi)容使用AT89S52單片機(jī)的串行口通過(guò)RS232通信接口與PC機(jī)進(jìn)行通信

2021-07-19 06:52:04

單片機(jī)串行口是發(fā)送或接收完一幀數(shù)據(jù)才進(jìn)入中斷的,一幀數(shù)據(jù)一般設(shè)定為一個(gè)字節(jié)(8位),此時(shí)串口的DR寄存器中只有這一幀的數(shù)據(jù),記住只有這一幀的數(shù)據(jù)!!!

2021-08-13 07:32:34

單片機(jī)串行口與PC機(jī)通訊資料

2012-08-20 10:58:58

單片機(jī)串行口結(jié)構(gòu)是怎樣構(gòu)成的?單片機(jī)串行口是如何進(jìn)行工作的?有哪些應(yīng)用呢?

2022-01-26 07:22:14

、關(guān)于同步通信和異步通信六、關(guān)于同步通信和異步通信的比七、幾種常見(jiàn)電平信號(hào)的區(qū)別八、單片機(jī)串行口介紹九、關(guān)于串口流控的介紹十、關(guān)于單片機(jī)串行口的引腳十一、關(guān)于單片機(jī)串行口的應(yīng)用十二、單片機(jī)串行口的應(yīng)用總結(jié)前言本次講解STC8A8K64S4A12系列單片機(jī)串行口知識(shí)點(diǎn)。一、關(guān)于通訊和通信的區(qū)別目前,

2021-11-26 06:28:44

串行口是單片機(jī)與外界進(jìn)行信息交換的工具。■ 8051單片機(jī)的通信方式有兩種:并行通信:數(shù)據(jù)的各位同時(shí)發(fā)送或接收。串行通信:數(shù)據(jù)一位一位次序發(fā)送或接收。參看下圖:串行通信的方式包括異步通信和同步通信

2021-12-08 07:20:10

1.串行口方式0應(yīng)用編程 8051單片機(jī)串行口方式0為移位寄存器方式,外接一個(gè)串入并出的移位寄存器,就能擴(kuò)展一個(gè)并行口。例:用8051單片機(jī)串行口外接CD4094擴(kuò)展8位并行輸出口,如圖所示,8位

2013-01-21 14:21:33

單片機(jī)串行口通信程序設(shè)計(jì)例子

2016-06-05 21:37:36

單片機(jī)uart串口通信程序,51單片機(jī)雙機(jī)通訊 UART異步通訊 帶詳細(xì)注釋版一、總體設(shè)計(jì)1.設(shè)計(jì)要求:兩片單片機(jī)之間進(jìn)行串行通信,發(fā)送端將0~f循環(huán)發(fā)送到接收端,并在接收端顯示。2.設(shè)計(jì)方案:本次

2021-07-14 07:03:26

介紹:串行口是單片機(jī)與外界進(jìn)行信息交換的工具。8051單片機(jī)的通信方式有兩種:并行通信:數(shù)據(jù)的各位同時(shí)發(fā)送或接收。串行通信:數(shù)據(jù)一位一位次序發(fā)送或接收。參看下圖:串行通信的方式:異步通信:它用一個(gè)

2018-06-21 09:19:48

1.串行口方式0應(yīng)用編程 8051單片機(jī)串行口方式0為移位寄存器方式,外接一個(gè)串入并出的移位寄存器,就能擴(kuò)展一個(gè)并行口。例:用8051單片機(jī)串行口外接CD4094擴(kuò)展8位并行輸出口,如圖所示,8位

2018-06-21 09:31:21

單片機(jī)的串行口及應(yīng)用通信方式:?1.并行通信:數(shù)據(jù)的各位同時(shí)進(jìn)行傳送。速度快、效率高、成本高?2.串行通信:數(shù)據(jù)一位一位地按順序進(jìn)行傳送。減少傳輸線、降低通信成本按照數(shù)據(jù)傳送方向: 單工、半雙工

2021-07-20 06:44:40

單片機(jī)系統(tǒng)多串行口設(shè)計(jì)技術(shù)研究

2012-08-07 00:10:30

多機(jī)通信一、實(shí)驗(yàn)?zāi)康亩?shí)驗(yàn)內(nèi)容三、實(shí)驗(yàn)步驟四、C代碼如下五、實(shí)驗(yàn)結(jié)果六、實(shí)驗(yàn)體會(huì)一、實(shí)驗(yàn)?zāi)康?1) 掌握串行口工作方式的程序設(shè)計(jì),掌握單片機(jī)通訊的編制(2)了解實(shí)現(xiàn)串行通訊的硬環(huán)境,數(shù)據(jù)格式的協(xié)議

2021-12-08 07:43:43

AT89C51串行口工作方式是什么?AT89C51單片機(jī)在無(wú)線數(shù)據(jù)傳輸中的應(yīng)用是什么?

2021-06-07 06:21:32

0a 架構(gòu):單片機(jī)->CC2541(用戶板子)->天線天線->CC2540USBdongle->計(jì)算機(jī)(串行口調(diào)試助手軟件) 故障:單片機(jī)發(fā)出:‘123’字符串,計(jì)算機(jī)

2020-03-17 10:20:55

《單片機(jī)》實(shí)驗(yàn)——實(shí)驗(yàn)6 MCS-51內(nèi)部串行口實(shí)驗(yàn)一、實(shí)驗(yàn)?zāi)康亩⒅R(shí)要點(diǎn)三、實(shí)驗(yàn)內(nèi)容一、實(shí)驗(yàn)?zāi)康?.理解串行通信的特點(diǎn)及分類2.掌握單片機(jī)內(nèi)部串口的3種工作方式的特點(diǎn)及應(yīng)用3.掌握雙機(jī)通信的編程

2021-12-01 06:12:42

串行的使用概述STC15W4K32S4系列單片機(jī)有4個(gè)串行口功能快捷鍵撤銷:Ctrl/Command + Z重做:Ctrl/Command + Y加粗:Ctrl/Command + B斜體:Ctrl

2021-07-20 06:51:40

前言人類生存于世,少不了溝通。溝通使人類互相認(rèn)知,傳遞信息,提升生活品質(zhì)。但然單片機(jī)也需要,不然單單一個(gè)機(jī)器,無(wú)法構(gòu)成一個(gè)系統(tǒng),發(fā)揮更大的力量。只有單片機(jī)與外圍設(shè)備傳遞信息,互相反饋才會(huì)有一個(gè)完美

2021-12-09 08:14:19

【單片機(jī)】單片機(jī)期末復(fù)習(xí)知識(shí)點(diǎn)提綱3一、定時(shí)器1.1理論例子1.2實(shí)際例子二、雙機(jī)通信串行口2.1實(shí)際例子三、中斷3.1實(shí)際例子一、定時(shí)器51有定時(shí)/計(jì)數(shù)器T0和定時(shí)/計(jì)數(shù)器T1,T0有4種工作方式

2022-01-10 06:10:46

基于51單片機(jī)的時(shí)鐘-跑表設(shè)計(jì)方案(程序+仿真)

2018-11-29 12:07:49

一、目標(biāo)單片機(jī)甲機(jī)P1端口外接8位撥碼開(kāi)關(guān);乙機(jī)P0外接8只LED。要求使用單片機(jī)串行口通信,在查詢狀態(tài)下使單片機(jī)乙機(jī)的8只LED能夠顯示甲機(jī)8位撥碼開(kāi)關(guān)的狀態(tài)。二、布線三、實(shí)現(xiàn)四、結(jié)語(yǔ)...

2022-01-20 07:55:36

51單片機(jī)串行通信原理計(jì)算機(jī)通信串行通信異步通信同步通信數(shù)據(jù)傳送速率傳輸方向單片機(jī)串行口串行口特殊功能寄存器串行口控制寄存器SCON電源控制寄存器PCON計(jì)算機(jī)通信計(jì)算機(jī)通信:計(jì)算機(jī)與外部設(shè)備或

2021-11-17 07:58:43

意圖:在上位機(jī)上用串口調(diào)試助手發(fā)送一個(gè)字符X,單片機(jī)收到后返回給上位機(jī)“I get X”,串行口波特率9600bps實(shí)際得到 XI get X 求問(wèn)為什么多了X代碼如下串口調(diào)試助手界面見(jiàn)附圖

2017-08-07 15:02:30

本次課程設(shè)計(jì)要求設(shè)計(jì)一基于單片機(jī)控制的串行口調(diào)時(shí)時(shí)鐘設(shè)計(jì)計(jì),該數(shù)字鐘能同時(shí)顯小時(shí),分鐘和秒。并能對(duì)時(shí)鐘進(jìn)行設(shè)置。時(shí)鐘開(kāi)始顯示為00時(shí)00分,也就是數(shù)碼管(或用液晶塊)顯示00.00。秒信號(hào)用時(shí)的個(gè)位

2018-01-08 10:52:16

大學(xué)生作業(yè),數(shù)據(jù)通訊沒(méi)有學(xué)好啊。求各位大神幫助,在線等,挺急的編程實(shí)現(xiàn)用單片機(jī)串行口自收發(fā)數(shù)據(jù)功能。具體要求如下:(1)定義兩個(gè)數(shù)據(jù)緩沖區(qū)(數(shù)據(jù))長(zhǎng)度為10字節(jié),一個(gè)發(fā)送數(shù)據(jù)緩沖區(qū)(帶初始值),一個(gè)

2015-06-26 12:56:36

怎樣處理單片機(jī)與鎖存器的關(guān)系? 為何要用串行口擴(kuò)展 I/O?

2017-03-13 23:43:07

單片機(jī)的設(shè)計(jì)方案和單片機(jī)提供商之間的關(guān)系

2021-03-10 07:20:31

一種基于FPGA的RS232異步串行口IP核設(shè)計(jì)方案。

2021-05-07 06:13:18

郭天祥51單片機(jī)中串行口打印在調(diào)試程序中的運(yùn)用ad_vo = (float)ad_val****什么意思,謝謝

2016-05-09 20:21:15

傳統(tǒng)方法設(shè)計(jì)單片機(jī)串行口波特率時(shí),往往要使用特殊頻率的晶振。本文在分析MCS-51單片機(jī)串行口工作原理的基礎(chǔ)上,提出基于 12 MHz晶振的單片機(jī)系統(tǒng),通過(guò)編程實(shí)現(xiàn)所需波特率的

2009-04-08 09:43:19 19

19 在以單片機(jī)為核心的多級(jí)分布式系統(tǒng)中,常常需要擴(kuò)展單片機(jī)的串行通信口,本文分別介紹了基于SP2538 專用串行口擴(kuò)展芯片及Intel8251 的兩種串行口擴(kuò)展方法,并給出了實(shí)際的硬件電

2009-06-15 09:53:11 33

33 單片機(jī)串行口應(yīng)用舉例: 在計(jì)算機(jī)分布式測(cè)控系統(tǒng)中,經(jīng)常要利用串行通信方式進(jìn)行數(shù)據(jù)傳輸。80C51單片機(jī)的串行口為計(jì)算機(jī)間的通信提供了極為便利的條

2009-12-03 22:54:50 105

105 單片機(jī)串行口

單片機(jī)是一種集成在電路芯片,是采用超大規(guī)模集成電路技術(shù)把具有數(shù)據(jù)處理能力的中央處理器CPU隨機(jī)存儲(chǔ)器RAM、只讀存儲(chǔ)器ROM、多種I/O口和中斷

2010-03-30 15:00:56 32

32 摘要:本文介紹一種用純軟件來(lái)擴(kuò)展89C51單片機(jī)串行口的方法,詳細(xì)說(shuō)明了通過(guò)掃描發(fā)送、中斷接收實(shí)現(xiàn)模擬串行通信的編程技巧。關(guān)鍵詞:串行口;通信;89C51;單片機(jī);擴(kuò)展

2010-07-15 12:25:00 33

33 單片機(jī)教程二十:單片機(jī)串行口介紹

介紹:串行口是單片機(jī)與外界進(jìn)行信息交換的工具。 8051單片機(jī)的通信方式有兩種:并行通

2009-05-15 23:16:14 1509

1509

單片機(jī)教程二十一:單片機(jī)串行口通信程序設(shè)計(jì)

1.串行口方式0應(yīng)用編程 8051單片機(jī)串行口方式0為移位寄存器方式,外接一個(gè)串入并出的移位寄存器

2009-05-15 23:17:04 952

952 PIC單片機(jī)軟件異步串行口實(shí)現(xiàn)方法

在用單片機(jī)開(kāi)發(fā)各種嵌入式應(yīng)用系統(tǒng)時(shí),異步串行通信是經(jīng)常要用到的一種通信

2009-09-17 14:56:19 1397

1397

單片機(jī)入門(mén)教程第22課-串行口應(yīng)用編程實(shí)例

1. 串口方式0應(yīng)用編程 8051單片機(jī)串行口方式0為移位寄存器方式,外接一個(gè)串入并出的移位寄存器,

2010-01-07 15:40:13 1223

1223

單片機(jī)的串行口是最常用的端口, 對(duì)于存在兩個(gè)或多個(gè)串行口的單片機(jī)來(lái)說(shuō), 充分利用串行口進(jìn)行通信是非常重要的。故以常見(jiàn)的8051系列單片機(jī)為基礎(chǔ), 介紹了通過(guò)串行口實(shí)現(xiàn)與PC機(jī)的并

2011-12-09 15:19:08 103

103 單片機(jī)系統(tǒng)多串行口:在以單片機(jī)為核心的測(cè)控系統(tǒng)中.微控制器往往需要兩個(gè)或兩個(gè)以上的串行口與其他主機(jī)或外設(shè)進(jìn)行通訊.

2011-12-09 15:22:53 55

55 5 1 系列單片機(jī)中模擬串行口的C 語(yǔ)言實(shí)現(xiàn).pdf

2015-10-29 11:34:19 4

4 基于單片機(jī)的綜合應(yīng)用程序串行口試驗(yàn)【C語(yǔ)言】

2016-01-06 14:22:52 5

5 單片機(jī)串行口與PC機(jī)通訊資料,很好的設(shè)計(jì)資料,快來(lái)下載學(xué)習(xí)吧。

2016-05-09 17:35:17 26

26 單片機(jī)串行口通信程序設(shè)計(jì)

2017-09-04 10:13:38 10

10 基于51單片機(jī)匯編語(yǔ)言教程:22課單片機(jī)串行口通信程序設(shè)計(jì)

2017-09-04 11:00:04 25

25 基于單片機(jī)串行口的并行通信技術(shù)

2017-09-05 08:43:03 4

4 1.串行口方式0應(yīng)用編程 8051單片機(jī)串行口方式0為移位寄存器方式,外接一個(gè)串入并出的移位寄存器,就能擴(kuò)展一個(gè)并行口。 單片機(jī)串行口通信程序設(shè)計(jì)硬件連接圖 例:用8051單片機(jī)串行口

2017-11-22 12:07:44 317

317

8051單片機(jī)串行口方式0為移位寄存器方式,外接一個(gè)串入并出的移位寄存器,就能擴(kuò)展一個(gè)并行口...

2018-03-15 09:57:36 8485

8485

串行口方式0應(yīng)用編程 8051單片機(jī)串行口方式0為移位寄存器方式,外接一個(gè)串入并出的移位寄存器,就能擴(kuò)展

2018-03-16 16:29:49 8405

8405

基本同步串行口模塊 (BSSP) 是用于同其它外設(shè)模塊或單片機(jī)進(jìn)行通信的串行接口。這些外設(shè)模 塊可以是串行 EEPROM、移位寄存器、顯示驅(qū)動(dòng)器或 A/D 轉(zhuǎn)換器等。本文主要介紹了PICmicro中檔單片機(jī)系列之基本同步串行口(BSSP)。

2018-06-25 05:20:00 6

6 本文檔的主要內(nèi)容詳細(xì)介紹的是51單片機(jī)教程之80C51單片機(jī)的串行口介紹及如何進(jìn)行串行總線的擴(kuò)展。主要內(nèi)容包括了:1 串行通信基本知識(shí),2 80C51單片機(jī)的串行口,3 80C51單片機(jī)的串行口應(yīng)用,4 單片機(jī)的串行總線擴(kuò)展

2018-12-05 11:53:53 27

27 本文檔的主要內(nèi)容詳細(xì)介紹的是51單片機(jī)教程之51單片機(jī)的串行口應(yīng)用舉例資料說(shuō)明主要內(nèi)容包括了:1 計(jì)算機(jī)串行通信基礎(chǔ),2 80C51的串行口,3 單片機(jī)串行口應(yīng)用舉例

2018-12-12 17:27:25 17

17 使用簡(jiǎn)單的三態(tài)門(mén),即可為單片機(jī)擴(kuò)充串行口,僅僅占用單片機(jī)的一、二個(gè)引腳作為控制引線而已。

2019-02-02 17:31:00 8590

8590

串行口是單片機(jī)與外界進(jìn)行信息交換的工具,8051單片機(jī)的通信方式有兩種:并行通信:數(shù)據(jù)的各位同時(shí)發(fā)送或接收。 串行通信:數(shù)據(jù)一位一位次序發(fā)送或接收。

2019-08-14 17:32:00 1

1 本文檔的主要內(nèi)容詳細(xì)介紹的是單片機(jī)教程之串行口與串行通信的詳細(xì)資料說(shuō)明包括了:1 串行通信概述,2 MCS-51的串行口結(jié)構(gòu),3 和串行通信有關(guān)的8個(gè)寄存器 ,4串行口四種工作方式,5 串行口的應(yīng)用編程,6 串行通信總線標(biāo)準(zhǔn)及接口

2019-07-17 17:28:33 15

15 本章介紹AT89S52單片機(jī)片內(nèi)串行口的工作原理,與串行口有關(guān)的特殊功能寄存器以及串行口的4種工作方式,串行口多機(jī)通信的工作原理,串行通信中的各種接口標(biāo)準(zhǔn),以及雙機(jī)串行通信的軟件編程設(shè)計(jì)。

2019-10-25 14:58:00 11

11 51單片機(jī)學(xué)習(xí) 串行口通信實(shí)驗(yàn)

2021-11-12 12:06:00 17

17 51單片機(jī)串行口中斷的使用初始化中斷服務(wù)程序主程序初始化 void SCON_init(){ SCON = 0x50; //0101 0000 TMOD = 0x20; //0010 0000

2021-11-12 13:06:02 6

6 實(shí)驗(yàn)?zāi)康暮腿蝿?wù)目的:利用“模塊化單片機(jī)教學(xué)實(shí)驗(yàn)平臺(tái)”,加深對(duì)單片機(jī)的串行口的理解。任務(wù):利用單片機(jī)的串行口完成程序設(shè)計(jì)。實(shí)驗(yàn)內(nèi)容使用AT89S52單片機(jī)的串行口通過(guò)RS232通信接口與PC機(jī)進(jìn)行通信

2021-11-17 09:36:02 10

10 五、關(guān)于同步通信和異步通信六、關(guān)于同步通信和異步通信的比七、幾種常見(jiàn)電平信號(hào)的區(qū)別八、單片機(jī)串行口介紹九、關(guān)于串口流控的介紹十、關(guān)于單片機(jī)串行口的引腳十一、關(guān)于單片機(jī)串行口的應(yīng)用十二、單片機(jī)串行口的應(yīng)用總結(jié)前

2021-11-18 11:51:01 103

103 51單片機(jī)串行口與波特率

2021-11-23 09:21:01 10

10 單片機(jī)串行口結(jié)構(gòu)??串行口結(jié)構(gòu)如上圖??發(fā)送時(shí),SBUF中寫(xiě)入數(shù)據(jù)后,串行口通過(guò)發(fā)送控制器,將SBUF中的數(shù)據(jù)逐個(gè)逐位地通過(guò)串行輸出口TXD引腳逐個(gè)發(fā)出,當(dāng)一個(gè)字節(jié)發(fā)送結(jié)束后,觸發(fā)TI中斷位,通知單片機(jī)

2021-12-01 16:06:05 13

13 電子發(fā)燒友網(wǎng)站提供《AT89S52單片機(jī)片內(nèi)串行口的工作原理.ppt》資料免費(fèi)下載

2023-12-15 09:07:12 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論