引言

近年來,隨著計算機、數字網絡和電視技術的飛速發展,人們對高質量電視圖像的需求不斷提高,我國廣播電視事業日新月異、迅猛發展。四年前開通的數字電視衛星廣播,目前已形成相當規模。數字攝錄、數字特技、非線性編輯系統、虛擬演播室、數字轉播車、網絡硬盤陣列以及機械手數字播放系統等設備,已陸續進入中央電視臺和各省市級電視臺。標準高清晰度數字電視SDTV/HDTV已列為國家重大科研產業工程項目,試驗播出已在中央廣播電視塔上進行。目前,我國數字電視節目制作和數字電視地面廣播已在緊鑼密鼓地推進,而“十一五”將是我國數字電視整體平移的準備期,是廣播電視系統從模擬向數字化過渡的重要階段。

本設計正是為應對這一趨勢,并為滿足市場對于多路ASI/SDI數字視頻信號光傳輸設備的巨大需求而設計的。它是通過時分復用技術實現在一根光纖中同時傳輸兩路ASI/SDI數字視頻信號的光傳輸設備,該項設計可為今后開發更多路更高速的異步數字信號光傳輸設備打好基礎。

系統實現方案

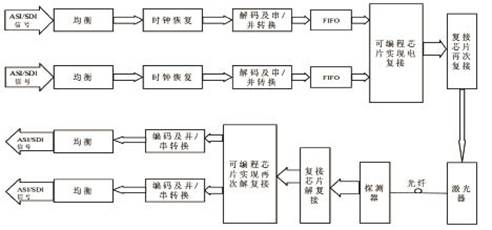

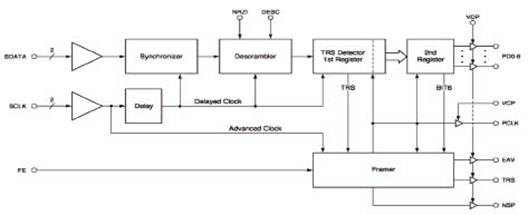

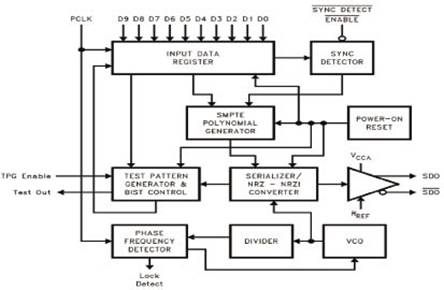

該ASI/SDI信號光傳輸設備的工作原理見圖1。

圖1 系統原理圖

由圖1可知,ASI/SDI串行信號通過均衡電路后得到整形,轉變成為一組差分信號;再經過時鐘恢復電路將信號中的時鐘提取出來,以便在接下來的解碼和同步信號時使用;再通過解碼電路后,串行的高速信號轉變成并行的低速信號,為接下來的電復接過程做好準備;最后通過FIFO電路的調整實現異步信號跟本地的電復接時鐘同步,進而實現本地的電復接;再通過光模塊電/光轉換后傳輸到收端,收端收到信號后經過一系列逆向變換電路后,恢復出原始的ASI/SDI串行信號,完成整個傳輸過程。

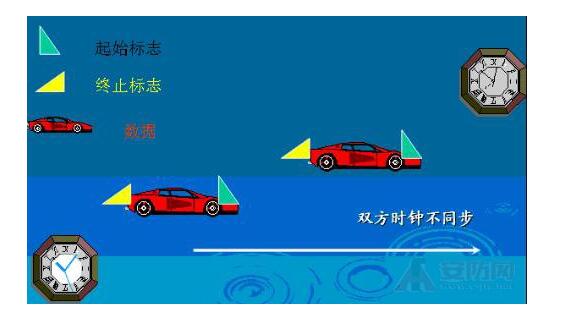

本設計中ASI/SDI信號的電復接技術是整個技術環節的關鍵。由于項目中需電復接的ASI/SDI信號速率很高,標準速率達到270Mbit/s,并且不是同源的信號復接,所以直接對該信號電復接很困難且不經濟,需要先恢復出各個信號的時鐘,把高速串行信號變換成低速并行信號,然后再通過FIFO芯片電路來調整各個信號的時鐘步伐,實現跟本地的時鐘同步,然后再通過可編程芯片進行兩路電信號復接,進而實現時分復用傳輸。只有經過這一系列的信號處理過程后,在接收端才可以實現順利的解復接過程,這也是該設計的主要技術攻關點。

另外,電復接的鎖定也是一個問題。信號路數越多,速率越高,越難鎖定,對PCB板的排版技術要求較高。通過對各個元器件的合理放置和科學的濾除雜波等各項處理,這個問題可以得到很好的解決。

硬件電路

在該設計中,主要使用的是美國國家半導體公司最新推出的功能強大且性能穩定的數字視頻芯片組。其中解碼及串/并轉換芯片選用CLC011;編碼及并/串轉換芯片選用CLC020;時鐘恢復芯片選用LMH0046;自適應電纜均衡芯片選用CLC014;CPLD芯片采用LATTICE公司的LC4256V;FIFO芯片采用IDT公司的IDT72V2105。

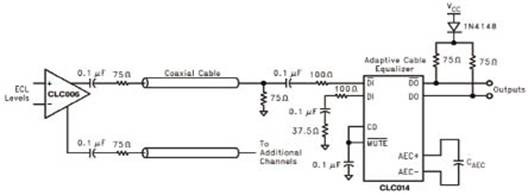

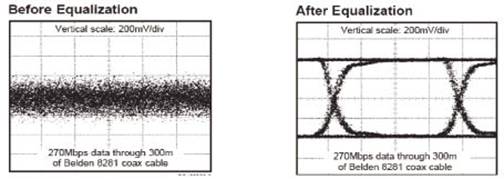

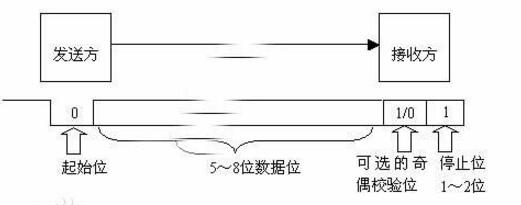

均衡部分電路處理過程如圖2所示。由圖2可知單端輸入的ASI/SDI串行信號通過均衡電路后得到整形,轉變成一組差分信號,為接下來的時鐘恢復過程作好了準備。通過均衡電路以后,信號質量大大提高,輸入輸出信號波形比較如圖3。

圖2 均衡部分電路處理過程

圖3 均衡電路波形比較

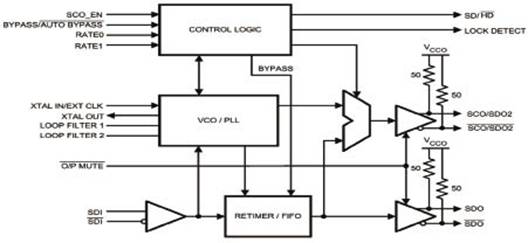

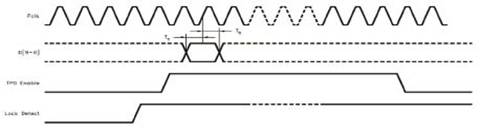

時鐘恢復部分電路處理過程由圖4所示。通過圖4可以看到,正確地設置好芯片的工作模式,由本地提供一個27M的時鐘供時鐘恢復芯片使用,將均衡后的高速差分信號輸入到芯片中,通過芯片處理后恢復出串行信號之中的時鐘信號,以便下面解碼部分電路使用。同時,該芯片也可支持高清信號的時鐘恢復功能。

圖4 時鐘恢復部分電路處理過程

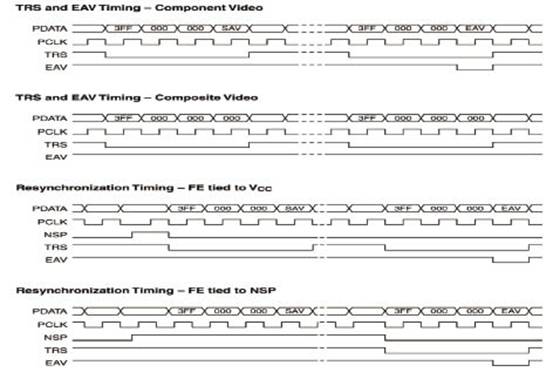

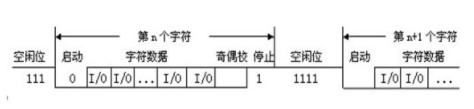

解碼部分電路處理過程由圖5所示。通過圖5可以看到,由時鐘恢復芯片恢復出來的串行時鐘和串行數據輸入到解碼芯片,通過串/并轉換后輸出10位并行數據和27M的并行時鐘,以備下面FIFO電路的時鐘調整使用。具體各個工作模式下信號的時序圖見圖6。

圖5 解碼部分電路處理過程

圖6 各模式信號時序圖

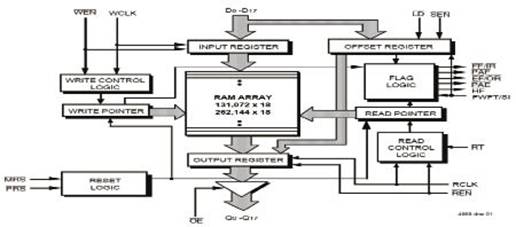

FIFO部分電路處理過程如圖7所示。其中讀時鐘使用編碼電路恢復出來的27M并行時鐘,寫時鐘使用本地的27M時鐘,通過調整實現經過FIFO的10位并行信號與本地時鐘同步,為接下來輸入到CPLD進行電復接做好準備。CPLD的電復接部分程序如下,其中2BP-S為復接程序,2BS-P為解復接程序。

圖7 FIFO部分電路處理過程

architecture SCHEMATIC of 2BP-S is

SIGNAL gnd : std_logic := '0';

SIGNAL vcc : std_logic := '1';

signal N_25 : std_logic;

signal N_12 : std_logic;

signal N_13 : std_logic;

signal N_15 : std_logic;

signal N_16 : std_logic;

signal N_17 : std_logic;

signal N_21 : std_logic;

signal N_22 : std_logic;

signal N_23 : std_logic;

signal N_24 : std_logic;

begin

I30 : G_D Port Map ( CLK=>N_25, D=>N_13, Q=>N_22 );

I29 : G_D Port Map ( CLK=>N_25, D=>N_16, Q=>N_23 );

I34 : G_OUTPUT Port Map ( I=>N_22, O=>Q0 );

I33 : G_OUTPUT Port Map ( I=>N_23, O=>Q1 );

I2 : G_INPUT Port Map ( I=>CLK, O=>N_25 );

I7 : G_INPUT Port Map ( I=>A, O=>N_12 );

I8 : G_INPUT Port Map ( I=>LD, O=>N_21 );

I6 : G_INPUT Port Map ( I=>B, O=>N_15 );

I12 : G_2OR Port Map ( A=>N_17, B=>N_24, Y=>N_16 );

I16 : G_2AND1 Port Map ( AN=>N_21, B=>N_22, Y=>N_24 );

I21 : G_2AND Port Map ( A=>N_21, B=>N_12, Y=>N_13 );

I20 : G_2AND Port Map ( A=>N_21, B=>N_15, Y=>N_17 );

end SCHEMATIC;

architecture SCHEMATIC of 2BS-P is

SIGNAL gnd : std_logic := '0';

SIGNAL vcc : std_logic := '1';

signal N_5 : std_logic;

signal N_1 : std_logic;

signal N_3 : std_logic;

signal N_4 : std_logic;

begin

I8 : G_OUTPUT Port Map ( I=>N_4, O=>Q0 );

I1 : G_OUTPUT Port Map ( I=>N_5, O=>Q1 );

I2 : G_INPUT Port Map ( I=>CLK, O=>N_3 );

I3 : G_INPUT Port Map ( I=>SIN, O=>N_1 );

I7 : G_D Port Map ( CLK=>N_3, D=>N_4, Q=>N_5 );

I4 : G_D Port Map ( CLK=>N_3, D=>N_1, Q=>N_4 );

end SCHEMATIC;

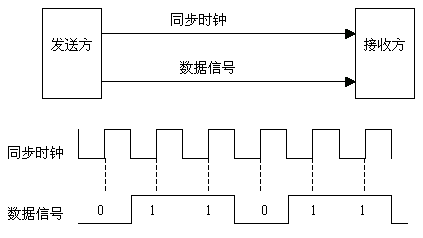

編碼部分電路處理過程如圖8所示。收端光模塊收到數據后,通過CPLD的解復接程序恢復出并行數據和同步時鐘,再通過編碼芯片電路恢復出原始的高速串行信號,經過電纜驅動芯片驅動后最終由傳輸設備輸出,完成整個傳輸過程。其中,編碼電路部分的信號時序如圖9所示。

圖8 編碼部分電路處理過程

圖9 編碼電路信號時序圖

結束語

基于CPLD的異步ASI/SDI信號電復接光傳輸設備的設計使用了最新的ASI/SDI信號電復接/分接技術,可以實現兩路信號的時分復用傳輸,替代了以往以波分復用技術為基礎的多路異步信號傳輸模式,大大節省了生產成本,使產品的市場競爭力進一步提高。

電子發燒友App

電子發燒友App

評論