老師給的一道題目:要求 1實(shí)現(xiàn)2psk 的調(diào)制與解調(diào)仿真2 使用相干檢測;3 加入加性高斯白噪聲;4傳輸距離 20KM;5 接收端 信噪比 S/N=2dB 請(qǐng)各位大俠告訴我,我應(yīng)該

2012-10-04 14:36:17

老師給的一道題目:要求 1實(shí)現(xiàn)2psk 的調(diào)制與解調(diào)仿真2 使用相干檢測;3 加入加性高斯白噪聲;4傳輸距離 20KM;5 接收端 信噪比 S/N=2dB 請(qǐng)各位大俠告訴我,我應(yīng)該

2012-10-04 14:39:21

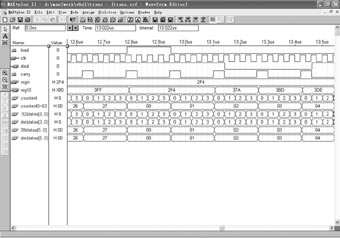

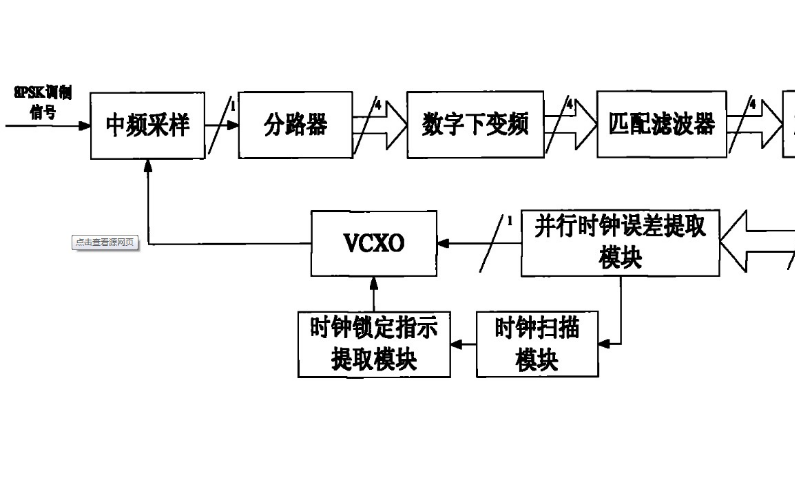

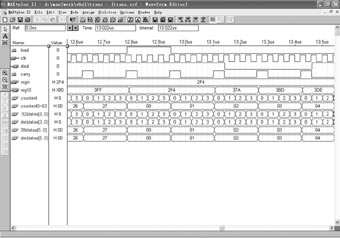

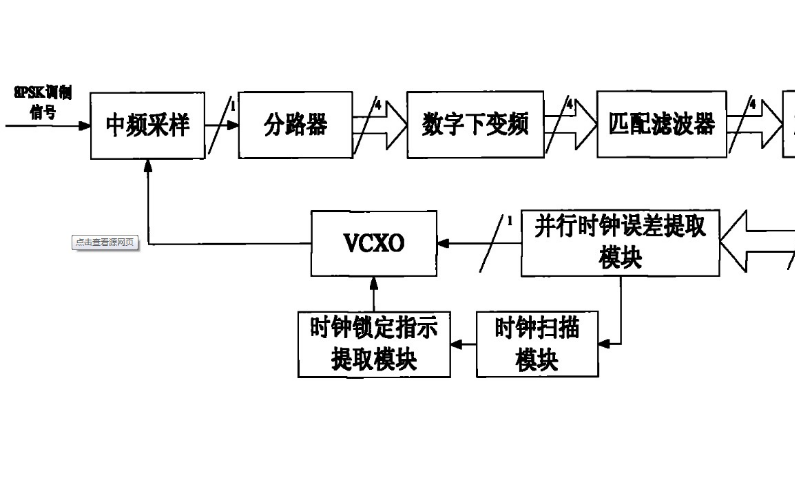

Altera公司的QuartusⅡ環(huán)境下,用VHDL語言實(shí)現(xiàn)了8PSK全數(shù)字解調(diào)系統(tǒng)設(shè)計(jì)。最后在PCB板上利用Stratix Ⅱ芯片實(shí)現(xiàn),并結(jié)合8PSK調(diào)制器進(jìn)行功能驗(yàn)證,得到滿意的結(jié)果。【關(guān)鍵詞】:PSK

2010-04-23 11:16:42

PSK-5D-5

2023-03-29 22:39:07

PSK-5D-9-T

2023-03-28 14:47:40

PSK-60-12

2023-03-29 21:46:10

PSK的相干解調(diào)怎么恢復(fù)載波?

2024-01-03 14:57:27

調(diào)制波指標(biāo)測試數(shù)據(jù)頻率最大頻偏失真度穩(wěn)定性100KHz5/10KHz小左右晃動(dòng)1MHz5/10KHz小好10MHz5/10KHz小好 實(shí)現(xiàn)了5/10KHz調(diào)頻信號(hào)的發(fā)生。(4) PSK/ASK指標(biāo)

2011-03-15 16:18:00

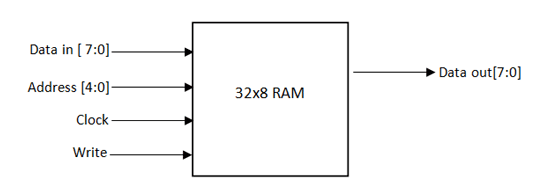

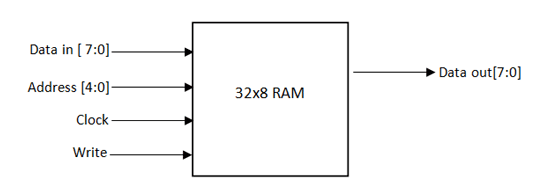

親愛的用戶,我想在VHDL中實(shí)現(xiàn)二維數(shù)組(內(nèi)存),并希望通過各種組件訪問(讀取)它,其中一個(gè)組件(用于讀取和寫入)都在verilog中。任何人都可以建議我聲明一個(gè)模塊及其與各種組件的鏈接。有害生物

2019-01-23 08:25:21

quartus中實(shí)現(xiàn)倍頻,vhdl語言的,請(qǐng)教各位高手、、、、、、、

2014-05-05 15:09:06

請(qǐng)教大家怎么用VHDL語言實(shí)現(xiàn)減法運(yùn)算?在FPGA設(shè)計(jì)時(shí)又該怎么操作呢?

2012-05-17 20:07:12

您好!最近在用ad9910做一個(gè)psk調(diào)制的項(xiàng)目(bpsk),主控制器采用的是msp430,現(xiàn)在能夠實(shí)現(xiàn)不同頻率的輸出,在做psk調(diào)制的時(shí)候,我采用的是在profile0寄存器和profile1

2018-11-27 09:12:55

EDA技術(shù)實(shí)用教程第4版VHDL課件

2013-06-21 18:04:03

支持大規(guī)模設(shè)計(jì)的分解和已有設(shè)計(jì)的再利用功能。4.門級(jí)網(wǎng)表對(duì)于用 VHDL 完成的一個(gè)確定的設(shè)計(jì),可以利用 EDA 工具進(jìn)行邏輯綜合和優(yōu)化,并自動(dòng)把VHDL 描述設(shè)計(jì)轉(zhuǎn)變成門級(jí)網(wǎng)表。5.獨(dú)立性VHDL 對(duì)設(shè)計(jì)的描述具有相對(duì)獨(dú)立性,設(shè)計(jì)者可以不懂硬件的結(jié)構(gòu),也不必對(duì)最終設(shè)計(jì)實(shí)現(xiàn)的目標(biāo)器件有很深入地了解。

2018-09-07 09:04:45

附件中有3個(gè)matlab的.m文件,是實(shí)現(xiàn)2psk信號(hào)的調(diào)制解調(diào)及其誤碼率的仿真。一個(gè)主文件,2個(gè)子文件。現(xiàn)在要求更改點(diǎn)東西實(shí)現(xiàn)4psk信號(hào)的調(diào)制解調(diào)及其仿真。。。。求高手。。。

2012-06-10 15:20:52

,各位大神,有人有用Verilog或者VHDL實(shí)現(xiàn)的RSA算法源代碼么?小弟急用,謝謝啦!拜謝!

2016-05-16 11:08:31

三人表決器的VHDL設(shè)計(jì)實(shí)現(xiàn)求代碼

2018-11-10 13:50:50

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載4:Verilog與VHDL特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD Verilog

2017-09-26 21:07:34

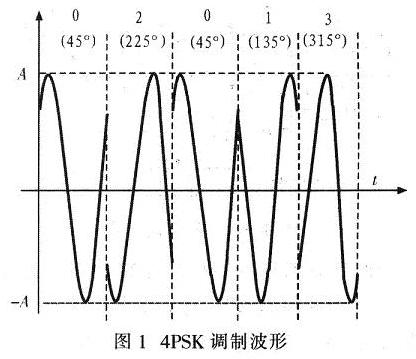

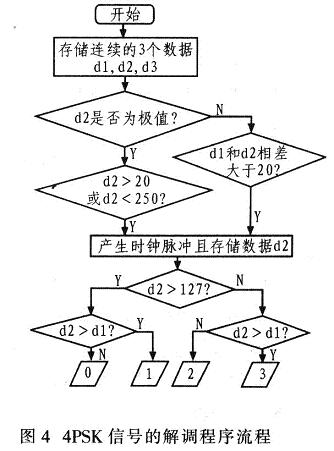

導(dǎo)讀:采用LabVIEW軟件對(duì)應(yīng)用于無線信道中的4PSK的數(shù)字通信方式和主要通信過程的實(shí)際情況進(jìn)行計(jì)算機(jī)模擬仿真。主要通信過程為抽樣、量化、編碼、調(diào)制解調(diào)、糾錯(cuò)編碼等,并給出了幾種調(diào)制解調(diào)的主要特性

2015-01-14 11:02:49

基于labview的4ASK 4FSK 4PSK 調(diào)制與解調(diào)程序 求好人發(fā)個(gè)

2014-04-02 19:54:13

就可以將它用作ADC的輸入時(shí)鐘。任何人都可以建議如何實(shí)現(xiàn)這個(gè)以及如何為此編寫vhdl代碼。示例代碼..謝謝

2020-06-18 12:18:31

親 ,我需要在VHDL / Verilog中實(shí)現(xiàn)流量生成器,它是如何實(shí)現(xiàn)的,請(qǐng)?jiān)诖艘龑?dǎo)我。謝謝以上來自于谷歌翻譯以下為原文Dear , I need to implement the traffic

2019-03-25 13:51:45

在multisim中仿真實(shí)現(xiàn)FM-GFSK和PM-D8PSK調(diào)制解調(diào)的電路。

2017-04-06 15:08:31

如何在ALTERA公司的Quartus II環(huán)境下用VHDL、Verilog HDL實(shí)現(xiàn)設(shè)計(jì)輸入,采用同步時(shí)鐘,成功編譯、綜合、適配和仿真,并下載到Stratix系列FPGA芯片EP1S25F780C5中。

2021-04-15 06:19:38

幀同步是什么工作原理?如何用VHDL語言實(shí)現(xiàn)幀同步的設(shè)計(jì)?

2021-04-08 06:33:59

你好,我目前在嘗試實(shí)現(xiàn)一個(gè)乘以兩個(gè)4位值的計(jì)算器時(shí)遇到了麻煩。計(jì)算很簡單,但我需要做的是輸出4個(gè)7段顯示的答案。當(dāng)兩個(gè)4位值相乘時(shí),大約有255個(gè)可能的答案,如何編寫VHDL代碼而不必編寫每個(gè)可能

2019-02-28 07:05:07

嗨, 我對(duì)此很新,所以我的知識(shí)有限。我正在學(xué)習(xí)電子學(xué),并且一直在使用spartan 3E入門板進(jìn)行簡單的VHDL項(xiàng)目。我們已經(jīng)教會(huì)通過以下列方式聲明每個(gè)模塊來映射引腳和內(nèi)部信號(hào)來實(shí)現(xiàn)頂層模塊

2019-11-08 14:07:23

直接數(shù)字頻率合成器DDS具有哪些特點(diǎn)?DDS基本原理及工作過程解析采用VHDL硬件實(shí)現(xiàn)DDS的優(yōu)化設(shè)計(jì)與實(shí)現(xiàn)

2021-04-12 06:28:28

應(yīng)用VHDL語言的FFT算法實(shí)現(xiàn)

2012-08-20 20:17:57

大家好,我正在嘗試使用VHDL實(shí)現(xiàn)雙曲線tan tan函數(shù),但問題是我不知道tanh函數(shù)怎么可以實(shí)現(xiàn)digital所以請(qǐng)如果任何身體可以告訴我這個(gè)想法,以便我可以在VHDL中實(shí)現(xiàn)它會(huì)很好的。非常感謝

2019-02-14 10:20:11

我試圖在vhdl中實(shí)現(xiàn)Bit-Spit aho corasick算法,任何人都可以幫助我從哪里開始。我還有另一個(gè)問題,我可以使用RAM實(shí)現(xiàn)狀態(tài)機(jī)謝謝TBONE以上來自于谷歌翻譯以下為原文I am

2019-01-23 10:43:55

如何用VHDL 實(shí)現(xiàn)積分器和PI 控制啊,老師要求的作業(yè),剛開始接觸VHDL,還不太會(huì),很捉急啊

2013-11-27 21:12:40

剛接觸FPGA 想用FPGA實(shí)現(xiàn)422通訊 求大牛給一個(gè)實(shí)現(xiàn)UART的VHDL的程序

2013-12-05 20:40:39

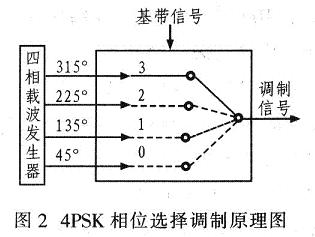

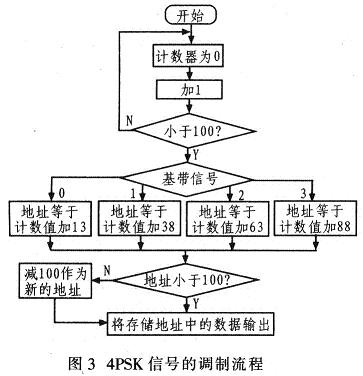

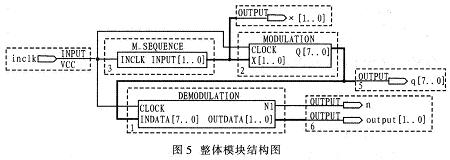

4PSK調(diào)制解調(diào)原理是什么基于VHDL的4PSK信號(hào)的調(diào)制和解調(diào)設(shè)計(jì)方案

2021-04-30 06:16:53

求助!vhdl 實(shí)現(xiàn)spwm程序!709030305@qq.com非常感謝

2012-10-31 10:36:02

求用matlab實(shí)現(xiàn)8PSK調(diào)制的源代碼

2014-03-24 12:31:17

用vhdl實(shí)現(xiàn)的51單片機(jī)內(nèi)核 帶源碼 core51_VHDL.rar

2018-07-03 05:53:42

移相鍵控(PSK)實(shí)驗(yàn) 一、實(shí)驗(yàn)?zāi)康?amp;nbsp; 1、了解M序列的性能,掌握其實(shí)現(xiàn)方法及其作用; &

2009-10-11 08:59:18

移相鍵控(PSK)實(shí)驗(yàn) 一、實(shí)驗(yàn)?zāi)康?amp;nbsp; 1、了解M序列的性能,掌握其實(shí)現(xiàn)方法及其作用; &

2008-10-21 12:38:45

用單片機(jī)開發(fā)版實(shí)現(xiàn) 移相鍵控(PSK/DPSK)調(diào)制與解調(diào)實(shí)驗(yàn),有哪位通信大神會(huì)寫這個(gè)程序?在線等~~急!!!!

2016-01-05 22:25:28

最近正在拿ADF4159開發(fā)板做PSK調(diào)制,調(diào)制周期設(shè)為10kHz,載頻870MHz。但是用示波器將數(shù)據(jù)存下來,分析后感覺沒有被調(diào)相信號(hào),不知道為什么?[size=13.3333px]ADF4159的最高調(diào)制周期為多少?參數(shù)到底應(yīng)該怎么設(shè)置?

2018-09-03 11:49:40

用VHDL語言實(shí)現(xiàn)樂曲演奏電路本程序是用VHDL對(duì)《梁祝協(xié)奏曲》中《化蝶》部分的樂曲電路實(shí)現(xiàn)。

2011-08-18 10:31:53

VHDL語言及其應(yīng)用的主要內(nèi)容:第一章 硬件模型概述第二章 基本的VHDL編程語言第三章 VHDL模型的組織第四章 VHDL綜合工具第五章 VHDL應(yīng)用樣例附錄A VHDL

2009-07-20 12:06:15 0

0

介紹了用VHDL 語言在硬件芯片上實(shí)現(xiàn)浮點(diǎn)加/ 減法、浮點(diǎn)乘法運(yùn)算的方法,并以Altera

公司的FLEX10K系列產(chǎn)品為硬件平臺(tái),以Maxplus II 為軟件工具,實(shí)現(xiàn)了6 點(diǎn)實(shí)序列浮點(diǎn)加/ 減法

2009-07-28 14:06:13 85

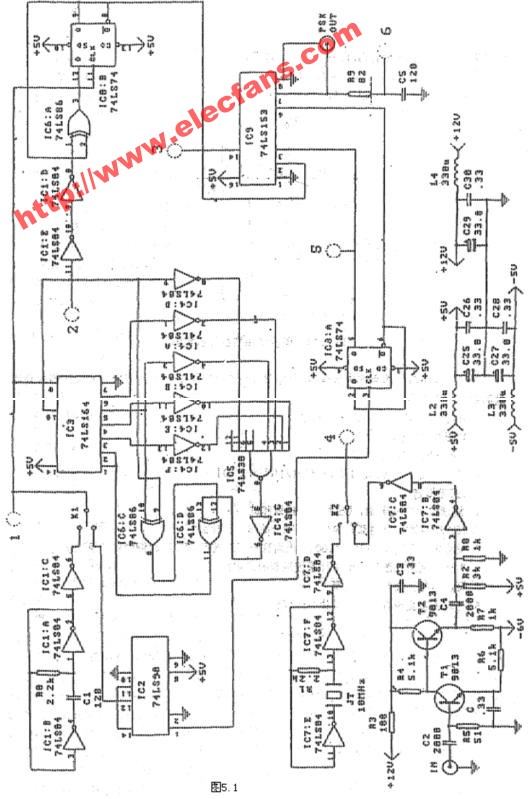

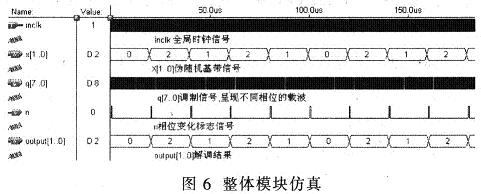

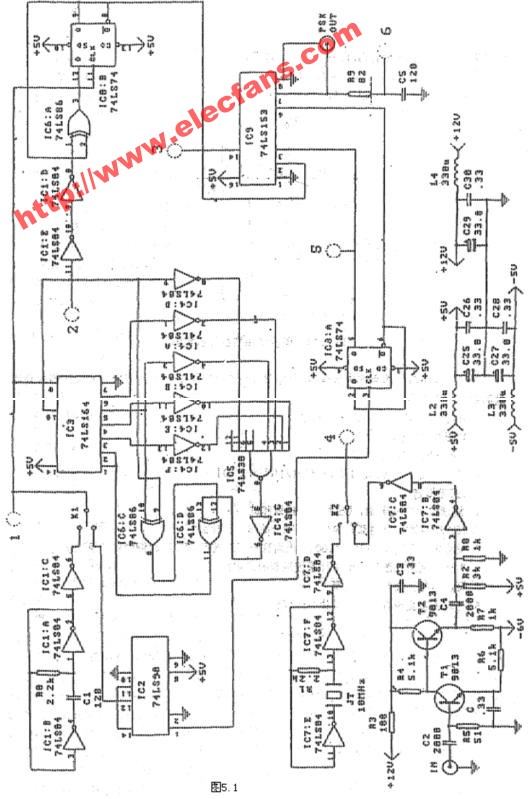

85 本論文主要討論和仿真了基于CPLD的PSK系統(tǒng)單元設(shè)計(jì),在闡述調(diào)制解調(diào)系統(tǒng)的基本原理與設(shè)計(jì)方法的同時(shí),又詳細(xì)地介紹了系統(tǒng)的總體電路框圖及各個(gè)模塊的具體軟硬件實(shí)現(xiàn)。作者以V

2009-07-30 11:42:31 17

17 本文致力于基于神經(jīng)網(wǎng)絡(luò)的通信信號(hào)調(diào)制類型識(shí)別器設(shè)計(jì)研究。論文提出了一種改進(jìn)的BP神經(jīng)網(wǎng)絡(luò)分類器,它采用7個(gè)特征參數(shù),可以對(duì)CW、2FSK、4FSK、8FSK、2PSK、4PSK、8PSK、8QAM、16QA

2009-08-29 10:22:10 10

10 VHDL語言描述數(shù)字系統(tǒng):本章介紹用 VHDL 描述硬件電路的一些基本手段和基本方法。 VHDL 語言是美國國防部在 20 世紀(jì) 80 年代初為實(shí)現(xiàn)其高速集成電路計(jì)劃(VHSIC)而提出的

2009-09-01 09:02:40 37

37 VHDL 語言程序的元素:本章主要內(nèi)容:VHDL語言的對(duì)象VHDL語言的數(shù)據(jù)類型VHDL語言的運(yùn)算符VHDL語言的標(biāo)識(shí)符VHDL語言的詞法單元

2009-09-28 14:32:21 41

41 VHDL基礎(chǔ)教程:VHDL語言及其應(yīng)用目錄:第1章 VHDL基本概念 1.1 數(shù)字系統(tǒng)建模 1.2 建模的域和級(jí) 1.3 建模語言 1.4 VHDL建模的概念 1.5 一個(gè)VHDL設(shè)計(jì)實(shí)例 1 6

2009-10-16 18:17:58 357

357 以VHDL實(shí)現(xiàn)的數(shù)字溫度表本專題主要是在于如何運(yùn)用硬體描述語言(VHDL) 仿真數(shù)字溫度表,以及它如何找出ADC0809 的數(shù)位轉(zhuǎn)換值與AD590 感測實(shí)際溫度值的對(duì)應(yīng)關(guān)系,并以Al tera MAX+ plusI

2009-11-22 17:52:56 82

82 數(shù)字電池EDA入門之VHDL程序實(shí)現(xiàn)集

2009-12-07 14:14:57 0

0 1. CPSK調(diào)制VHDL

2010-06-22 16:06:17 42

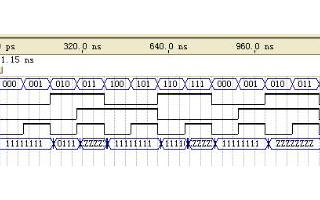

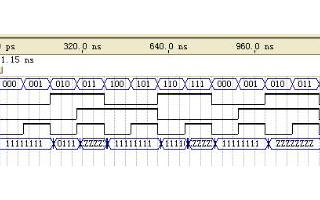

42 闡述了4PSK調(diào)制器的基本原理,給出調(diào)制系統(tǒng)設(shè)計(jì)框圖。在MAX+plusII環(huán)境下,利用VHDL語言實(shí)現(xiàn)了4PSK調(diào)制器設(shè)計(jì),并對(duì)系統(tǒng)的各模塊仿真。采用VHDL模塊化和自上而下的設(shè)計(jì)方法,提高了

2010-12-20 17:31:28 51

51 用VHDL語言實(shí)現(xiàn)3分頻電路

標(biāo)簽/分類:

眾所周知,分頻器是FPGA設(shè)計(jì)中使用頻率非常高的基本設(shè)計(jì)之一,盡管在目前大部分設(shè)計(jì)中,廣泛使用芯片廠家集成的鎖相

2007-08-21 15:28:16 5527

5527 vhdl是什么意思

VHDL 語言的英文全名是 Very High Speed Integrated Circuit Hardware Description Language ,即超高速集

2008-09-02 12:55:59 7732

7732 實(shí)驗(yàn)五(PSK)移相鍵控實(shí)驗(yàn)

一、實(shí)驗(yàn)?zāi)康模?

1、 了解M序列的性能,掌握其實(shí)現(xiàn)方法及其應(yīng)用;

2008-10-21 14:01:11 6920

6920

摘 要: 串行通信是實(shí)現(xiàn)遠(yuǎn)程測控的重要手段。采用VHDL語言在CPLD上實(shí)現(xiàn)了串行通信,完全可以脫離單片機(jī)使用。

關(guān)鍵詞:

2009-06-20 12:43:50 570

570

用VHDL設(shè)計(jì)專用串行通信芯片

一種專用串行同步通信芯片(該芯片內(nèi)部結(jié)構(gòu)和操作方式以INS8250為參考)的VHDL設(shè)計(jì)及CPLD實(shí)現(xiàn),著重介紹了用VHDL及CPLD設(shè)計(jì)專用通信芯片的

2009-10-12 19:07:48 1701

1701

數(shù)字電壓表的VHDL設(shè)計(jì)與實(shí)現(xiàn)

介紹數(shù)字電壓表的組成及工作原理,論述了基于VHDL語言和FPGA芯片的數(shù)字系統(tǒng)的設(shè)計(jì)思想和實(shí)現(xiàn)過程。 關(guān)鍵詞:數(shù)字電壓表;VHDL語

2009-10-12 19:14:32 1628

1628

什么是二相絕對(duì)移相調(diào)制(2PSK)

1.2PSK信號(hào)的調(diào)制方框圖

第一種方法:鍵控法

2010-03-18 14:14:27 2386

2386 VHDL設(shè)計(jì)中信號(hào)與變量問題的研究

在VHDL程序設(shè)計(jì)中,可以充分利用信號(hào)或變量的系統(tǒng)默認(rèn)值,來靈活實(shí)現(xiàn)設(shè)計(jì)目標(biāo)。本文從應(yīng)用的角度舉例說明了VHDL設(shè)計(jì)中信號(hào)與變量

2010-04-12 14:52:21 1184

1184

首先分析了8PSK 軟解調(diào)算法的復(fù)雜度以及MAX算法的基本原理,并在Altera 公司的Stratix II 系列FPGA芯片上實(shí)現(xiàn)了此軟解調(diào)硬件模塊

2011-04-08 11:22:15 6901

6901

文章在MAX+PLUS II 開發(fā)環(huán)境下采用VHDL 語言設(shè)計(jì)并實(shí)現(xiàn)了電表抄表器討論了系統(tǒng)的四個(gè)組成模塊的設(shè)計(jì)和VHDL 的實(shí)現(xiàn)每個(gè)模塊采用RTL 級(jí)描述整體的生成采用圖形輸入法通過波形仿真下載芯

2011-09-23 17:56:11 40

40 第1章 數(shù)字系統(tǒng)EDA設(shè)計(jì)概論 第2章 可編程邏輯器件設(shè)計(jì)方法 第3章 VHDL語言基礎(chǔ) 第4章 數(shù)字邏輯單元設(shè)計(jì) 第5章 數(shù)字系統(tǒng)高級(jí)設(shè)計(jì)技術(shù)(*) 第6章 基于HDL設(shè)計(jì)輸入 第7章 基于原理圖設(shè)計(jì)輸

2012-09-18 13:38:46 163

163 頻移鍵控 (FSK)和相移鍵控 (PSK) 調(diào)制方案廣泛用于數(shù)字通信、雷達(dá)、RFID以及多種其他應(yīng)用。

2012-11-02 11:02:49 5837

5837 基于LabVIEW的2psk通信系統(tǒng)的設(shè)計(jì)+論文

2016-01-15 16:22:00 27

27 DSP之 PSK調(diào)制與解調(diào)VHDL程序及仿真教程,很好的DSP自學(xué)資料,快來學(xué)習(xí)吧。

2016-04-15 17:42:41 15

15 8psk的設(shè)計(jì)和仿真。

2016-05-16 17:15:25 43

43 Xilinx FPGA工程例子源碼:FM收音機(jī)的解碼及控制器VHDL語言實(shí)現(xiàn)

2016-06-07 14:13:43 11

11 Xilinx FPGA工程例子源碼:VHDL實(shí)現(xiàn)對(duì)圖像的采集和壓縮

2016-06-07 14:54:57 6

6 vhdl入門

2016-12-16 16:30:02 23

23 基于VHDL的SDRAM控制器的實(shí)現(xiàn)

2017-01-22 13:43:27 12

12 本文主要介紹了開關(guān)控制數(shù)碼管的VHDL程序的設(shè)計(jì)與實(shí)現(xiàn)。VHDL是一種應(yīng)用廣泛的硬件描述語言,設(shè)計(jì)者可以通過它編寫代碼,通過模擬器仿真驗(yàn)證其功能,完成邏輯綜合與邏輯優(yōu)化,最后通過下載到相應(yīng)

2018-01-15 16:24:49 4850

4850

本文主要介紹了C到VHDL的編譯器設(shè)計(jì)與實(shí)現(xiàn),首先介紹了C與VHDL的語言特征,其次闡述了設(shè)計(jì)方案,最后介紹了轉(zhuǎn)換過程及測試分析,具體的跟隨小編一起來了解一下。

2018-05-17 11:06:58 4155

4155 本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL教程之使用VHDL進(jìn)行電子設(shè)計(jì)所需的所有資料包括了:VHDL設(shè)計(jì)基礎(chǔ)知識(shí),VHDL并行語句,VHDL程序?qū)嶓w,VHDL入門,VHDL語言要素,EDA設(shè)計(jì)流程及其工具,IA64 應(yīng)用程序寄存器,LCD液晶顯示漢字字符集表,OCMJ 系列液晶顯示器控制命令集表等

2018-09-25 08:00:00 0

0 本文檔的主要內(nèi)容詳細(xì)介紹的是VHDL教程之VHDL語言元素的詳細(xì)資料概述一內(nèi)容包括了:1. VHDL語言的客體2 VHDL語言的數(shù)據(jù)類型3 VHDL數(shù)據(jù)類型轉(zhuǎn)換4 VHDL詞法規(guī)則與標(biāo)識(shí)符

2018-11-05 08:00:00 0

0 8PSK調(diào)制方式是常用的高階調(diào)制方式,在衛(wèi)星通信中經(jīng)常使用。不過考慮到實(shí)際使用中會(huì)存在相位模糊度,因此大多將8PSK結(jié)合差分的方式出現(xiàn)。程序中涉及了鎖相環(huán)程序,為后續(xù)的鎖相環(huán)章節(jié)的講解做好準(zhǔn)備。需要重點(diǎn)理解環(huán)路噪聲帶寬的概念。

2019-06-30 11:48:45 8752

8752

利用MATLAB/Simulink軟件中的Communication Blockets(通信模塊)對(duì)PSK數(shù)字傳輸系統(tǒng)進(jìn)行動(dòng)態(tài)、可視化仿真,清晰地表現(xiàn)出PSK傳輸系統(tǒng)的系統(tǒng)組成及各項(xiàng)性能指標(biāo)。

2019-11-18 17:57:56 15

15 VHDL是一種用來描述數(shù)字邏輯系統(tǒng)的“編程語言”。它通過對(duì)硬件行為的直接描述來實(shí)現(xiàn)對(duì)硬件的物理實(shí)現(xiàn),代表了當(dāng)今硬件設(shè)計(jì)的發(fā)展方向。VHDL是為了滿足邏輯設(shè)計(jì)過程中的各種需求而設(shè)計(jì)的。

2020-04-23 15:51:03 2362

2362

本文檔的主要內(nèi)容詳細(xì)介紹的是使用Quartus和VHDL語言實(shí)現(xiàn)的LPC時(shí)序的工程文件免費(fèi)下載。

2020-09-18 16:49:00 20

20 本文檔的主要內(nèi)容詳細(xì)介紹的是使用VHDL實(shí)現(xiàn)簡易電子琴演奏器設(shè)計(jì)的工程文件免費(fèi)下載。

2020-11-02 17:53:48 26

26 本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA實(shí)現(xiàn)自動(dòng)售貨機(jī)的VHDL程序與仿真資料。

2020-12-21 17:10:00 23

23 本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA實(shí)現(xiàn)LED控制的VHDL程序與仿真資料免費(fèi)下載。

2021-01-18 17:32:46 12

12 本手冊(cè)討論VHDL和Synario可編程IColution。本手冊(cè)旨在補(bǔ)充可編程IC入門手冊(cè)中的材料本手冊(cè)中討論了以下主題HDL語言結(jié)構(gòu)如何編寫可合成的VHDL如何控制VHDL設(shè)計(jì)的實(shí)現(xiàn)VHDL數(shù)據(jù)

2021-01-21 16:02:13 32

32 傳統(tǒng)的8PSK頻偏估計(jì)方法通常需要上百個(gè)符號(hào)完成,其優(yōu)點(diǎn)在于能夠實(shí)現(xiàn)較大的載波頻偏補(bǔ)償,但是同步時(shí)間較長,不

2021-04-02 13:48:18 2747

2747

在本教程中,我們將探索如何使用 ModelSim 在 VHDL 中實(shí)現(xiàn) RAM。

2022-07-29 16:34:37 1922

1922

基帶信號(hào)生成模塊(pcm.v)產(chǎn)生碼率為390.625kbps的基帶數(shù)據(jù),送給CRD500擴(kuò)展口觀測的同時(shí),送給PSK調(diào)制模塊;

2023-03-28 09:23:08 3940

3940 電子發(fā)燒友網(wǎng)站提供《基于VHDL語言實(shí)現(xiàn)遠(yuǎn)程防盜報(bào)警設(shè)計(jì).pdf》資料免費(fèi)下載

2023-11-08 14:33:11 0

0 2023-11-08 08:32:03 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論