。數(shù)字和模擬設(shè)計(jì)人員可以利用 AD9250-FMC-250EBZ 套件簡化并快速完成高速 JESD204B ADC-FPGA平臺(tái)的原型開發(fā)。

2013-02-28 17:59:56 806

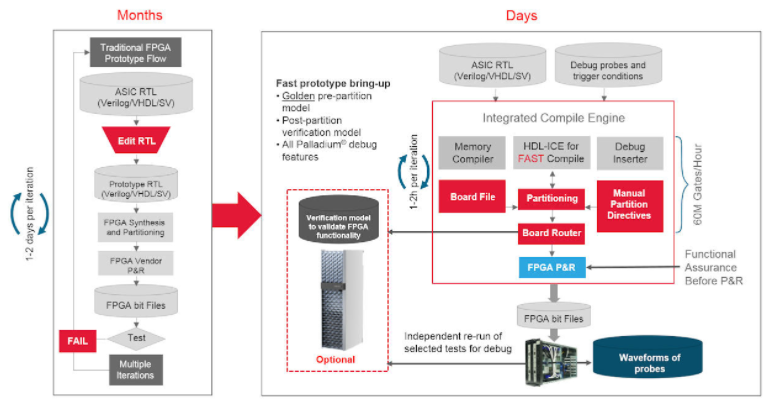

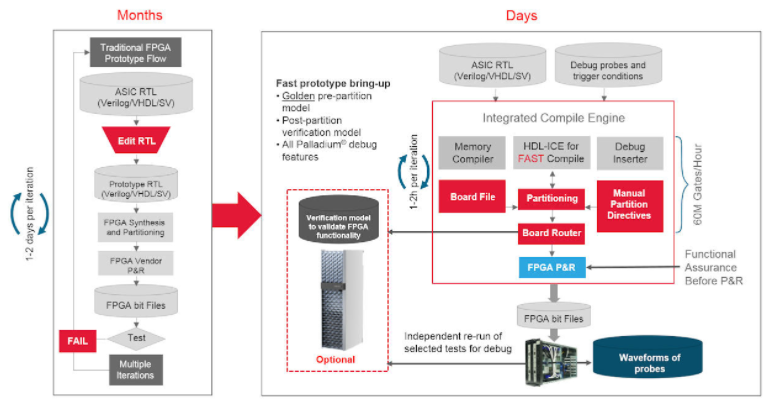

806 基于 FPGA 的 ASIC 原型可快速、準(zhǔn)確地實(shí)現(xiàn) SoC 系統(tǒng)建模和驗(yàn)證并加速軟件和固件的開發(fā)。Xilinx 推出Virtex?-7 2000T 器件,使基于 FPGA 的原型得到了進(jìn)一步發(fā)展

2013-03-14 14:33:00 1269

1269

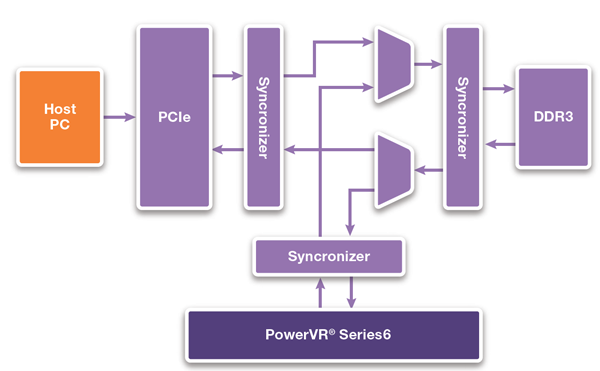

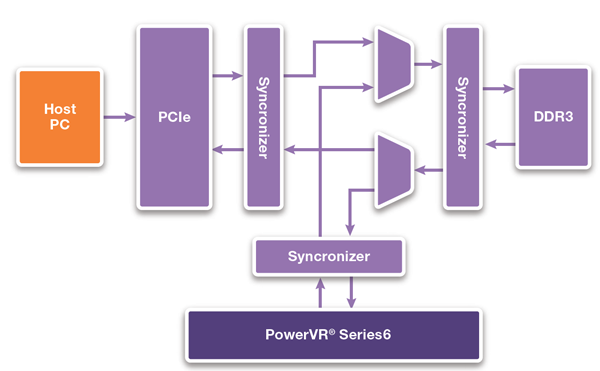

Synopsys所做的第一步是啟動(dòng)一個(gè)概念驗(yàn)證項(xiàng)目。這個(gè)項(xiàng)目為Imagination的PowerVR Series6 GPU展示了基于FPGA的原型設(shè)計(jì)。

2015-06-24 09:47:00 1619

1619

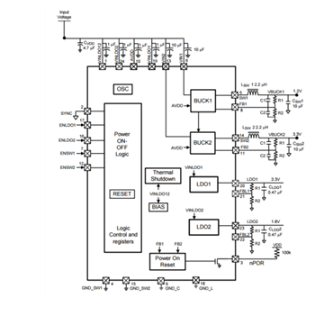

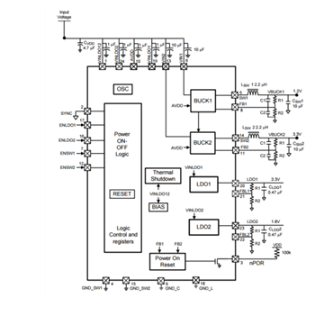

工業(yè)電子產(chǎn)品的發(fā)展趨勢是更小的電路板尺寸、更時(shí)尚的外形和更具成本效益。由于這些趨勢,電子系統(tǒng)設(shè)計(jì)人員必須降低印刷電路板(PCB)的尺寸和成本。使用現(xiàn)場可編程門陣列(FPGA)和片上系統(tǒng)(SoC

2020-07-16 17:32:05 744

744

什么是FPGA原型?? FPGA原型設(shè)計(jì)是一種成熟的技術(shù),用于通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗(yàn)證專門應(yīng)用的集成電路(ASIC),專用標(biāo)準(zhǔn)產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能

2022-07-19 16:27:29 1735

1735 FPGA原型在數(shù)字芯片設(shè)計(jì)中非常重要,因?yàn)橄啾扔梅抡嫫鳎蛘?b class="flag-6" style="color: red">加速器等來跑仿真,FPGA的運(yùn)行速度,更接近真實(shí)芯片,可以配合軟件開發(fā)者來進(jìn)行底層軟件的開發(fā)。這一流片前的軟硬件的協(xié)同開發(fā),是其最不可替代的地方。

2023-05-10 10:44:00 4791

4791

如今,FPGA 功能強(qiáng)大且管腳數(shù)目極大,可為工程師提供大量機(jī)會(huì)來提升特性和功能,同時(shí)還能降低產(chǎn)品成本。隨著復(fù)雜度增加,將這些器件集成到印刷電路板也成為了一項(xiàng)嚴(yán)峻的挑戰(zhàn)。數(shù)百個(gè)邏輯信號(hào)需映射到器件

2018-09-20 11:11:16

FPGA原型驗(yàn)證已是當(dāng)前原型驗(yàn)證的主流且成熟的芯片驗(yàn)證方法——它通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗(yàn)證ASIC的功能,并在芯片的基本功能驗(yàn)證通過后就可以開始驅(qū)動(dòng)的開發(fā),一直到芯片

2020-08-21 05:00:12

根據(jù)需求進(jìn)行重新配置,而ASIC一旦制造完成,其功能就無法更改。

開發(fā)周期和成本 :FPGA的開發(fā)周期相對(duì)較短,成本較低,適合原型驗(yàn)證和小批量生產(chǎn)。而ASIC的開發(fā)周期長,成本較高,但大批量生產(chǎn)時(shí)具有

2024-02-22 09:54:36

FPGA(現(xiàn)場可編程邏輯器件)產(chǎn)品近幾年的演進(jìn)趨勢越來越明顯:一方面,FPGA供應(yīng)商致力于采用當(dāng)前最先進(jìn)的工藝來提升產(chǎn)品的性能,降低產(chǎn)品的成本;另一方面,越來越多的通用IP(知識(shí)產(chǎn)權(quán))或客戶定制IP

2012-11-07 20:25:53

FPGA(現(xiàn)場可編程邏輯器件)產(chǎn)品近幾年的演進(jìn)趨勢越來越明顯:一方面,FPGA供應(yīng)商致力于采用當(dāng)前最先進(jìn)的工藝來提升產(chǎn)品的性能,降低產(chǎn)品的成本;另一方面,越來越多的通用IP(知識(shí)產(chǎn)權(quán))或客戶定制IP

2012-11-20 20:09:57

對(duì)于各種不同的數(shù)據(jù)中心工作負(fù)載,FPGA 可以顯著提高性能,最大程度減少附加功耗并降低總體擁有成本 (TCO)。

2019-08-13 08:03:44

設(shè)計(jì)使用的特定資源進(jìn)行篩選。最后,裸片在六周內(nèi)完成組裝、標(biāo)記和最終測試,以確保功能和性能。市場上沒有任何其它 FPGA成本降低解決方案,能夠在這么短的時(shí)間內(nèi)完成從原型設(shè)計(jì)到量產(chǎn)的轉(zhuǎn)化。采用賽靈思的專利測試

2012-08-11 18:17:16

領(lǐng)域發(fā)揮了越來越大的作用。在移動(dòng)互聯(lián)時(shí)代,為了增強(qiáng)圖片檢測的處理能力,降低圖片檢測成本,騰訊使用FPGA對(duì)CNN計(jì)算進(jìn)行加速。研發(fā)團(tuán)隊(duì)使用FPGA完成CNN算法的Alexnet模型,FPGA處理

2017-04-15 16:17:41

MAX3948直流耦合激光驅(qū)動(dòng)器和DS4830光電微控制器。 Maxim的40G芯片組為數(shù)據(jù)中心提供高性價(jià)比、高能效方案 數(shù)據(jù)中心和數(shù)據(jù)通信網(wǎng)絡(luò)在顯著提升數(shù)據(jù)密度的同時(shí),仍需維持原有的低功耗特性

2012-12-12 16:36:17

設(shè)計(jì)技巧為什么能夠節(jié)省功耗?降低FPGA功耗的設(shè)計(jì)技巧有哪些?

2021-04-30 06:04:19

ASIC設(shè)計(jì)-FPGA原型驗(yàn)證

2020-03-19 16:15:49

MPS2和MPS2+FPGA原型板是ARM Cortex-M評(píng)估和開發(fā)的開發(fā)平臺(tái)。

MPS2和MPS2+FPGA原型板提供以下功能:

Altera Cyclone FPGA和主板上電和配置MPS2

2023-08-18 07:25:28

得Morph-IC-II成為必須透過 USB下載新軟件以重新動(dòng)態(tài)配置硬件功能的理想應(yīng)用選擇。此外,除了提高應(yīng)用的靈活性,透過USB重新配置硬件也可降低BOM成本, FPGA只需為最復(fù)雜的分離功能而不是所有功能來設(shè)定大小。

2019-07-03 08:29:05

FPGA器件的存儲(chǔ)器。因此,HAPS-51系統(tǒng)提供了一種低成本、高性能的原型設(shè)計(jì)解決方案,能顯著縮短當(dāng)前極具挑戰(zhàn)性的SoC設(shè)計(jì)的開發(fā)時(shí)間。HAPS系統(tǒng)是Synplicity功能強(qiáng)大的Confirma

2018-11-20 15:49:49

加利福尼亞州,圣何塞— 2014年9月3日– S2C公司今日宣布TAI Player Pro 5.1版本正式發(fā)布。此次最新版本將幫助用戶加速FPGA原型開發(fā)、提高工程師的生產(chǎn)力,以及實(shí)現(xiàn)最高的原型

2019-07-02 06:23:44

市場上已有的解決方案,以降低開發(fā)成本。在當(dāng)今對(duì)成本和功耗都非常敏感的“綠色”環(huán)境下,對(duì)于高技術(shù)企業(yè),兩種挑戰(zhàn)都有什么影響呢?第一種挑戰(zhàn)意味著開發(fā)全新的產(chǎn)品,其功能是獨(dú)一無二的,具有較低的價(jià)格以及較低

2019-08-09 07:41:27

。由于HDL仿真不足以發(fā)現(xiàn)系統(tǒng)級(jí)錯(cuò)誤,芯片設(shè)計(jì)人員正利用FPGA來加速算法創(chuàng)建和原型設(shè)計(jì)。利用FPGA處理大型測試數(shù)據(jù)集可以使工程師快速評(píng)估算法和架構(gòu)并迅速做出權(quán)衡。工程師也可以在實(shí)際環(huán)境下測試設(shè)計(jì),避免

2020-05-04 07:00:00

采用基于現(xiàn)場可編程門陣列(FPGA)的原型的驗(yàn)證團(tuán)隊(duì)面臨的最大挑戰(zhàn)之一在于當(dāng)原型系統(tǒng)未能發(fā)揮期望的性能時(shí)了解原型系統(tǒng)的內(nèi)部行為。分析和調(diào)試這些設(shè)計(jì)的一個(gè)關(guān)鍵因素是難以觀察內(nèi)部信號(hào)。 目前的頂級(jí)

2019-07-12 06:38:15

復(fù)用器重構(gòu)降低FPGA成本

2012-08-17 10:43:02

FPGA的功耗高度依賴于用戶的設(shè)計(jì),沒有哪種單一的方法能夠?qū)崿F(xiàn)這種功耗的降低,如同其它多數(shù)事物一樣,降低功耗的設(shè)計(jì)就是一種協(xié)調(diào)和平衡藝術(shù),在進(jìn)行低功耗器件的設(shè)計(jì)時(shí),人們必須仔細(xì)權(quán)衡性能、易用性、成本、密度以及功率等諸多指標(biāo)。

2019-08-15 08:28:42

降低工業(yè)應(yīng)用的總體擁有成本大約三分之一的嵌入式設(shè)計(jì)人員考慮在嵌入式應(yīng)用中采用FPGA,只是認(rèn)為在設(shè)計(jì)中使用FPGA 過于昂貴。但是,從系統(tǒng)級(jí)了解總體擁有成本(TCO) ( 由產(chǎn)品生命周期中的開發(fā)

2013-11-13 11:17:35

ASIC驗(yàn)證能夠采用的主要技術(shù)是什么?如何利用現(xiàn)成FPGA開發(fā)板進(jìn)行ASIC原型開發(fā)?

2021-05-08 07:51:04

有什么方法可以提高片上系統(tǒng)級(jí)集成嗎?有什么方法可以降低物料成本嗎?

2021-05-14 06:20:23

芯片設(shè)計(jì)和驗(yàn)證工程師通常要為在硅片上實(shí)現(xiàn)的每一行RTL代碼寫出多達(dá)10行測試平臺(tái)代碼。驗(yàn)證任務(wù)在設(shè)計(jì)周期內(nèi)可能會(huì)占用50%或更多的時(shí)間。盡管如此辛苦,仍有接近60%的芯片存在功能瑕疵,需要返工。由于HDL仿真不足以發(fā)現(xiàn)系統(tǒng)級(jí)錯(cuò)誤,芯片設(shè)計(jì)人員正利用FPGA來加速算法創(chuàng)建和原型設(shè)計(jì)。

2019-09-18 07:50:02

對(duì)于各種不同的數(shù)據(jù)中心工作負(fù)載,FPGA 可以顯著提高性能,最大程度減少附加功耗并降低總體擁有成本 (TCO)。

2019-10-10 07:46:05

數(shù)十億臺(tái)5G設(shè)備將面世,如何有效降低5G測試成本?

2021-02-22 08:15:00

FPGA在嵌入式系統(tǒng)中的優(yōu)勢有哪些?如何通過LabVIEW FPGA加速嵌入式系統(tǒng)原型化?

2021-05-06 07:42:56

迫使設(shè)計(jì)團(tuán)隊(duì)不得不重新思考其發(fā)展策略。再加消費(fèi)類物聯(lián)網(wǎng)設(shè)備對(duì)產(chǎn)品上市時(shí)間的壓力,很顯然工程師需要適當(dāng)?shù)慕?決方案來解決這些問題。讓你在設(shè)計(jì)初期信心倍增基于FPGA 的原型系統(tǒng)是專門針對(duì)物聯(lián)網(wǎng)設(shè)備

2018-08-07 09:41:23

具、改進(jìn)的方法以及更高的抽象級(jí)正在幫助工程師實(shí)踐不同的宏架構(gòu)和微架構(gòu),并幫助他們提高其總設(shè)計(jì)生產(chǎn)力。 對(duì)于驗(yàn)證而言,這些設(shè)計(jì)的絕對(duì)規(guī)模和復(fù)雜度再加上大幅增加的軟件內(nèi)容使得FPGA原型對(duì)于通過硬件加速

2020-07-07 09:08:34

采用基于現(xiàn)場可編程門陣列(FPGA)的原型的驗(yàn)證團(tuán)隊(duì)面臨的最大挑戰(zhàn)之一在于當(dāng)原型系統(tǒng)未能發(fā)揮期望的性能時(shí)了解原型系統(tǒng)的內(nèi)部行為。分析和調(diào)試這些設(shè)計(jì)的一個(gè)關(guān)鍵因素是難以觀察內(nèi)部信號(hào)。

2019-10-14 07:07:06

為什么不能采用基于現(xiàn)場可編程門陣列(FPGA)的原型?驗(yàn)證團(tuán)隊(duì)面臨的最大挑戰(zhàn)之一在于當(dāng)原型系統(tǒng)未能發(fā)揮期望的性能時(shí)了解原型系統(tǒng)的內(nèi)部行為。分析和調(diào)試這些設(shè)計(jì)的一個(gè)關(guān)鍵因素是難以觀察內(nèi)部信號(hào)。

2019-08-13 07:45:06

請問有什么方法可以降低Linux的成本嗎?

2021-04-25 06:15:12

有什么方法可以降低微波/射頻器件的成本嗎?

2021-05-25 06:49:40

描述用于原型的小型低成本電路開發(fā)板近年來,我用 Arduino 開發(fā)了許多原型。在這些創(chuàng)作過程中,總有一些事情困擾著我。在原型中使用 Arduino 板占用了大量空間,價(jià)格昂貴,并且難以連接

2022-09-05 07:18:07

從去年開始,由于去產(chǎn)能、環(huán)保督查等因素引起電機(jī)原材料大幅漲價(jià),從而導(dǎo)致生產(chǎn)成本推高,很多企業(yè)在不斷尋求降低成本的途徑。然而,也有不少企業(yè)在降成本的過程中走入了誤區(qū)!企業(yè)衡量成本優(yōu)勢的原則是:在保證

2018-10-11 10:20:16

,該如何從工程的角度來應(yīng)對(duì)挑戰(zhàn),降低研發(fā)和成本呢?本期設(shè)計(jì)坊與你一起來探討如何降低工業(yè)應(yīng)用總體擁有成本(TCO)?看Altera公司的FPGA器件如何幫你降低總體擁有成本(TCO)?下載閱讀《降低工業(yè)

2013-11-12 10:51:03

FPGA供應(yīng)商很重要,要考慮影響系統(tǒng)成本的方方面面,這體現(xiàn)在整個(gè)產(chǎn)品設(shè)計(jì)周期中。降低成本和功耗,提高效能,讓產(chǎn)品更快地運(yùn)行,這些均是設(shè)計(jì)工程師目前必須面對(duì)的棘手問題,因此,FPGA的選擇很重

2015-02-09 15:02:06

工業(yè)電子產(chǎn)品的發(fā)展趨勢是更小的電路板尺寸、更時(shí)尚的外形和更具成本效益。由于這些趨勢,電子系統(tǒng)設(shè)計(jì)人員必須降低印刷電路板(PCB)的尺寸和成本。使用現(xiàn)場可編程門陣列(FPGA)和片上系統(tǒng)(SoC

2019-03-08 06:45:06

。基于FPGA的原型驗(yàn)證方法憑借其速度快、易修改、真實(shí)性的特點(diǎn),已經(jīng)成為ASIC芯片設(shè)計(jì)中重要的驗(yàn)證方法。本文主要描述高頻RFID芯片的FPGA原型驗(yàn)證平臺(tái)的設(shè)計(jì),并給出驗(yàn)證結(jié)果。1、RFID芯片的FPGA

2019-05-29 08:03:31

FPGA 原型設(shè)計(jì)人員艱苦努力所得的明顯回報(bào)就是 ASIC* 設(shè)計(jì)可以及時(shí)而毫無問題地完成產(chǎn)品定案(tape-out)。不過,原型設(shè)計(jì)還有一點(diǎn)日益重要的優(yōu)勢,即 ASIC 或 SoC 中嵌入的軟件在項(xiàng)目

2010-01-18 08:35:09 18

18 Xilinx擴(kuò)展Spartan-3A FPGA系列,降低大容量成本敏感應(yīng)用系統(tǒng)總成本

賽靈思公司宣布,作為Spartan-3A FPGA系列平臺(tái)延伸的小封裝FPGA正式量產(chǎn)。這些小封裝FPGA在提供突破性價(jià)位的同

2008-09-02 08:50:17 643

643 摘 要: 本文介紹了一種新的復(fù)用器重構(gòu)算法,能夠降低FPGA實(shí)際設(shè)計(jì)20%的成本。該算法通過減少復(fù)用器所需查找表(LUT)的數(shù)量來實(shí)現(xiàn)。算法以效率更高的4:1復(fù)用

2009-06-20 10:40:38 568

568

賽靈思宣布推出EasyPath-6 FPGA,從原型設(shè)計(jì)到量產(chǎn)僅需六周

全球可編程邏輯解決方案領(lǐng)導(dǎo)廠商賽靈思公司日前宣布隆重推出EasyPath-6 FPGA,該產(chǎn)品為高性能 FPGA 進(jìn)入量產(chǎn)器

2009-11-19 08:47:37 456

456 TI新推高集成正弦波時(shí)鐘緩沖器可顯著降低成本,節(jié)省板級(jí)空間

日前,德州儀器 (TI) 宣布推出業(yè)界最小型 4 通道、低功耗、低抖動(dòng)正弦至正弦波時(shí)鐘緩沖器。作為正弦

2009-12-01 08:43:11 1112

1112 電子發(fā)燒友網(wǎng)核心提示 :Maxim Integrated Products, Inc.推出兩組高速串行/解串(SerDes)芯片組,顯著降低汽車攝像頭系統(tǒng)成本。MAX9273/MAX9272 (22位)和MAX9271/MAX9272 (16位)芯片組通過標(biāo)準(zhǔn)的同軸電纜

2012-10-05 23:24:50 1582

1582 Altera公司近日宣布,幫助編程人員在FPGA中大幅度加速實(shí)現(xiàn)算法。Altera面向OpenCL的SDK 14.0版包括對(duì)程序設(shè)計(jì)非常熟悉的快速原型設(shè)計(jì)流程,支持用戶在FPGA加速板上快速進(jìn)行設(shè)計(jì)原型開發(fā)。

2014-07-03 09:52:07 907

907 顧名思義,proFPGA 的 Ultra-Scale? XCVU440 FPGA 模塊基于賽靈思 Virtex? UltraScale VU440,而且該原型板的額定容量高達(dá) 3000

2017-02-08 12:12:11 343

343 加速 RTI 前的軟件開發(fā)。 基于 FPGA 的原型設(shè)計(jì),提供精確的周期、較高的執(zhí)行效率和連接到外部的實(shí)際接口。 Synopsys 的混合原型解決方案將虛擬原型和基于 FPGA 的原型優(yōu)勢集于一身,加速了項(xiàng)目周期中軟件開發(fā)和系統(tǒng)集成的進(jìn)度。 借助 Synopsys 的混合原型驗(yàn)

2017-02-08 14:32:11 293

293 作者:Steve Leibson, 賽靈思戰(zhàn)略營銷與業(yè)務(wù)規(guī)劃總監(jiān) ?想開發(fā)一款能在多個(gè)地理位置處理任何設(shè)計(jì)規(guī)模的FPGA原型系統(tǒng)么?那么,最好擬定一個(gè)大規(guī)模的計(jì)劃方案。S2C新發(fā)布的Prodigy

2017-02-09 03:49:04 437

437 2017年3月2日,上海——楷登電子(美國 Cadence 公司,NASDAQ: CDNS)今日發(fā)布全新基于FPGA的Protium? S1原型驗(yàn)證平臺(tái)。借由創(chuàng)新的實(shí)現(xiàn)算法,平臺(tái)可顯著提高工程生產(chǎn)

2017-03-02 11:13:11 2744

2744 門陣列(FPGA)做為安謀國際核心測試芯片,進(jìn)而建構(gòu)SoC原型制作平臺(tái)。 驗(yàn)證SoC設(shè)計(jì) FPGA原型最穩(wěn)當(dāng) FPGA原型制作是在FPGA上實(shí)作SoC或特定應(yīng)用集成電路(ASIC)設(shè)計(jì)的方法,并進(jìn)行硬件驗(yàn)證和早期軟件開發(fā)。

2018-05-11 09:07:00 2405

2405

對(duì)于各種不同的數(shù)據(jù)中心工作負(fù)載,FPGA 可以顯著提高性能,最大程度減少附加功耗并降低總體擁有成本 (TCO)。

2018-07-07 10:38:00 6130

6130 由于FPGA具有可編程專用性,高性能及低功耗的特點(diǎn),浪潮推出基于FPGA的深度學(xué)習(xí)加速解決方案,希望通過更高配置的硬件板卡設(shè)計(jì)和內(nèi)置更高效已編譯算法,來加速FPGA在人工智能領(lǐng)域的應(yīng)用。

2018-02-19 05:02:00 656

656 目前處于AI大爆發(fā)時(shí)期,異構(gòu)計(jì)算的選擇主要在FPGA和GPU之間。盡管目前異構(gòu)計(jì)算使用最多的是利用GPU來加速,FPGA作為一種高性能、低功耗的可編程芯片,在處理海量數(shù)據(jù)時(shí),FPGA計(jì)算效率更高,優(yōu)勢更為突出,尤其在大量服務(wù)器部署時(shí),隱形的運(yùn)營成本會(huì)得到顯著降低。

2018-04-25 09:17:27 10593

10593 Maxim外設(shè)模塊借助多種便利的模擬和混合信號(hào)功能節(jié)省設(shè)計(jì)時(shí)間和成本。這些模塊可以很容易地插入配置為Pmod?的任意FPGA/CPU擴(kuò)展端口。

此外還提供模塊軟件支持,包括用于三個(gè)主流FPGA平臺(tái)

2018-06-22 11:00:00 3528

3528 FPGA (現(xiàn)場可編程門陣列)由于其硬件并行加速能力和可編程特性,在傳統(tǒng)通信領(lǐng)域和IC設(shè)計(jì)領(lǐng)域大放異彩。一路走來,FPGA的技術(shù)并不是一個(gè)新興的硬件器件,由于其開發(fā)門檻過高,硬件加速算法的發(fā)布

2018-07-27 14:25:00 1488

1488 reconfigure.io的Rob Taylor在法蘭克福的XDF 2018云軌道中展示了一個(gè)用例。

Rob討論了FPGA在FPGA中的可訪問性,降低了評(píng)估和利用FPGA的成本。

2018-11-22 06:08:00 3402

3402 競爭激烈的存儲(chǔ)器件市場上還從未出現(xiàn)過合適的金線替代品。如今,賀利氏推出的AgCoatPrime鍍金銀線,具有堪比金線的結(jié)合性與可靠性,可幫助半導(dǎo)體廠商顯著降低凈成本。

2019-03-26 17:04:56 3847

3847 隨著新型SoC(片上系統(tǒng))設(shè)計(jì)的成本和復(fù)雜性的不斷提高,現(xiàn)場可編程門陣列(FPGA)原型技術(shù)正日益成為SoC新項(xiàng)目的重要組成部分,甚至是至關(guān)重要的組成部分。通過提供一種更快到達(dá)硬件的方法,FPGA

2019-06-25 08:00:00 2

2 據(jù)外媒報(bào)道,德國馬克斯普朗克聚合物研究所(Max Planck Institute for Polymer Research)開發(fā)出一種單層OLED的原型,這預(yù)示著相對(duì)于現(xiàn)在多層疊在一起的OLED來說,制造成本可能大大降低。

2019-07-15 15:18:05 1829

1829 據(jù)外媒報(bào)道,德國馬克斯普朗克聚合物研究所開發(fā)出一種單層OLED的原型,制造成本可能大大降低。

2019-07-17 17:25:02 2069

2069 作為GPU在算法加速上強(qiáng)有力的競爭者,FPGA是否立即支持不同硬件,顯得尤為重要。FPGA與GPU不同之處在于硬件配置靈活,且FPGA在運(yùn)行深入學(xué)習(xí)中關(guān)鍵的子程序(例如對(duì)滑動(dòng)窗口的計(jì)算)時(shí),單位能耗下通常能比GPU提供更好的表現(xiàn)。

2019-10-18 15:42:04 626

626 國微思爾芯推出VU19P原型驗(yàn)證系統(tǒng),加速十億門級(jí)芯片設(shè)計(jì) 新分割引擎顯著提升性能和效率 模塊化、可擴(kuò)展的單、雙、四核VU19P原型系統(tǒng),單系統(tǒng)支持高達(dá)1億9600萬門ASIC設(shè)計(jì) 增強(qiáng)的分割引擎

2020-10-23 15:02:18 2375

2375 低功耗藍(lán)牙是藍(lán)牙技術(shù)聯(lián)盟設(shè)計(jì)和銷售的一種個(gè)人局域網(wǎng)技術(shù),相較經(jīng)典藍(lán)牙,低功耗藍(lán)牙旨在保持同等通信范圍的同時(shí)顯著降低功耗和成本。 在設(shè)計(jì)初始階段,優(yōu)化低功耗藍(lán)牙芯片能耗的訣竅會(huì)影響存儲(chǔ)器大小、時(shí)鐘速度

2021-03-05 15:31:04 1006

1006 從系統(tǒng)的特性上看,FPGA 原型系統(tǒng)支持多FPGA、自動(dòng)分割;性能較高的情況下運(yùn)行系統(tǒng)軟件;仿真加速器的超大容量可以放全芯片的設(shè)計(jì),進(jìn)行全芯片的系統(tǒng)功能/性能/功耗驗(yàn)證。

2022-05-25 09:35:13 7629

7629 作為還包括形式驗(yàn)證、仿真和仿真的 Cadence 驗(yàn)證套件的一部分,基于 FPGA 的原型設(shè)計(jì)剛剛通過自動(dòng)化進(jìn)行了重新發(fā)明,并可供更廣泛的物聯(lián)網(wǎng)設(shè)計(jì)開發(fā)人員使用。

2022-06-09 16:39:01 1562

1562

FPGA(Field Programmable Gate Array)原型驗(yàn)證,基于其成本適中、速率接近真實(shí)系統(tǒng)環(huán)境等優(yōu)點(diǎn),受到了驗(yàn)證工程師的青睞。正是由于廣泛豐富的應(yīng)用場景,FPGA 原型系統(tǒng)

2022-09-19 13:40:03 533

533

使用 Maxim 開發(fā)板的脈搏血氧飽和度應(yīng)用原型

2023-01-04 11:17:16 469

469 proFPGA 四模塊英特爾 Stratix 10 GX 10M FPGA 原型設(shè)計(jì)系統(tǒng)采用 4 個(gè)基于英特爾 Stratix 10 GX 10M FPGA 的可插拔 FPGA 模塊。

2023-03-17 11:22:30 470

470 在現(xiàn)代SoC芯片驗(yàn)證過程中,不可避免的都會(huì)使用FPGA原型驗(yàn)證,或許原型驗(yàn)證一詞對(duì)你而言非常新鮮,但是FPGA上板驗(yàn)證應(yīng)該是非常熟悉的場景了。

2023-03-28 09:33:16 854

854 FPGA原型驗(yàn)證在數(shù)字SoC系統(tǒng)項(xiàng)目當(dāng)中已經(jīng)非常普遍且非常重要,但對(duì)于一個(gè)SoC的項(xiàng)目而言,選擇合適的FPGA原型驗(yàn)證系統(tǒng)顯的格外重要

2023-04-03 09:46:45 928

928 FPGA原型平臺(tái)的性能估計(jì)與應(yīng)用過程的資源利用率以及FPGA性能參數(shù)密切相關(guān),甚至FPGA的制程也是一個(gè)因素。

2023-04-04 09:49:04 1475

1475 FPGA原型設(shè)計(jì)是一種成熟的技術(shù),用于通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗(yàn)證專門應(yīng)用的集成電路(ASIC),專用標(biāo)準(zhǔn)產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能和性能。

2023-04-10 09:23:29 947

947 FPGA原型驗(yàn)證平臺(tái)系統(tǒng)靈活性主要體現(xiàn)在其外部連接表現(xiàn)形式,由單片FPGA平臺(tái)或者2片的FPGA,抑或是4片的FPGA組成一個(gè)子系統(tǒng)。

2023-04-11 09:50:03 628

628 FPGA原型驗(yàn)證系統(tǒng)要盡可能多的復(fù)用SoC相關(guān)的模塊,這樣才是復(fù)刻SoC原型的意義所在。

2023-04-19 09:08:15 852

852 多片FPGA原型驗(yàn)證系統(tǒng)的拓?fù)溥B接方式各不相同,理想的多片FPGA原型驗(yàn)證系統(tǒng)應(yīng)該可以靈活配置,可以使用其相應(yīng)的EDA工具

2023-05-08 11:51:40 326

326

FPGA原型驗(yàn)證系統(tǒng)要盡可能多的復(fù)用SoC相關(guān)的模塊,這樣才是復(fù)刻SoC原型的意義所在。

2023-05-23 16:50:34 381

381

多片FPGA的原型驗(yàn)證系統(tǒng)的性能和容量通常受到FPGA間連接的限制。FPGA中有大量的資源,但I(xiàn)O引腳的數(shù)量受封裝技術(shù)的限制,通常只有1000個(gè)左右的用戶IO引腳。

2023-05-23 17:12:35 1149

1149

在現(xiàn)代SoC芯片驗(yàn)證過程中,不可避免的都會(huì)使用FPGA原型驗(yàn)證,或許原型驗(yàn)證一詞對(duì)你而言非常新鮮,但是FPGA上板驗(yàn)證應(yīng)該是非常熟悉的場景了。

2023-05-30 15:04:06 905

905

綜合工具的任務(wù)是將SoC設(shè)計(jì)映射到可用的FPGA資源中。自動(dòng)化程度越高,構(gòu)建基于FPGA的原型的過程就越容易、越快。

2023-06-13 09:27:06 278

278

所有形式的原型都為驗(yàn)證硬件設(shè)計(jì)和驗(yàn)證軟件提供了強(qiáng)大的方法,模型或多或少地模仿了目標(biāo)環(huán)境。基于FPGA的原型設(shè)計(jì)在項(xiàng)目的關(guān)鍵后期階段尤其有益。用戶有幾個(gè)原型設(shè)計(jì)選項(xiàng)根據(jù)他們的主要需求,可以選擇各種基于軟件和硬件的技術(shù)來原型他們的設(shè)計(jì)。

2023-10-11 12:39:41 275

275

FPGA原型設(shè)計(jì)是一種成熟的技術(shù),用于通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗(yàn)證專門應(yīng)用的集成電路(ASIC),專用標(biāo)準(zhǔn)產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能和性能。

2024-01-12 16:13:01 220

220 FPGA原型驗(yàn)證流程是確保FPGA(現(xiàn)場可編程門陣列)設(shè)計(jì)正確性和功能性的關(guān)鍵步驟。它涵蓋了從設(shè)計(jì)實(shí)現(xiàn)到功能驗(yàn)證的整個(gè)過程,是FPGA開發(fā)流程中不可或缺的一環(huán)。

2024-03-15 15:05:33 97

97

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論