電子發(fā)燒友網(wǎng)訊:新的一周悄然而去,但本周PLD行業(yè)發(fā)生的大事卻讓工程師們流連忘返。FPGA憑借三大法寶雄霸市場;RADX、Xilinx和ADI的聯(lián)合演示振奮人心;Altrea最新在線免費培訓(xùn)讓工程師們蠢蠢欲動;中國自主研發(fā)SOC表現(xiàn)到底如何?華為ASIC設(shè)計案,F(xiàn)PGA雙雄到底勝算幾何?PLD行業(yè)大事件,電子發(fā)燒友網(wǎng)一“網(wǎng)”打盡。特此推出最新一期《PLD每周焦點聚焦(10.22-10.28)》以饗讀者。

電子發(fā)燒友網(wǎng)訊:從28nm到3D堆疊,F(xiàn)PGA身價突然翻漲,不再是過去那個扮演配角的被支配角色。由于FPGA功能日益強大、對整個行業(yè)越來越重要,目前在許多應(yīng)用中,F(xiàn)PGA已逐漸成為支配系統(tǒng)運作的主角。而現(xiàn)階段FPGA的三大發(fā)展方向:28納米、3D堆疊,以及SoC系統(tǒng)化,也成為FPGA制霸市場的決勝關(guān)鍵。

28nm FPGA和SOC系統(tǒng)化:FPGA廠商立足市場的兩大利器

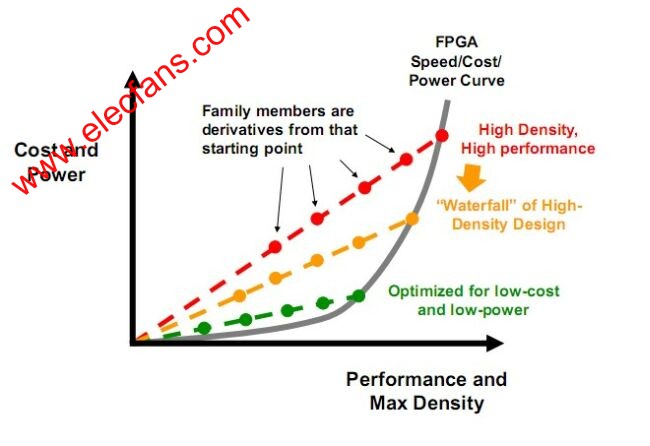

28納米目前已正式量產(chǎn),這宣告FPGA真正走入了28納米制程的新階段。包括Altera、Xilinx、Lattice在內(nèi)的主要FPGA廠商紛紛端出28納米FPGA大餐,意圖喂飽市場那張饑渴的大嘴。似乎只要擁有28納米產(chǎn)品,就象征了該廠家所擁有足夠的技術(shù)實力與研發(fā)創(chuàng)新。

FPGA走入28納米制程之后,不僅功能與整合度能超越傳統(tǒng)FPGA。最重要的是,產(chǎn)品性價比也進一步逼近ASSP與ASIC。走入28納米制程之后,F(xiàn)PGA可突破以往功耗過高的問題,成為高性能、低功耗以及小尺寸的代名詞。此外,F(xiàn)PGA廠商不斷提升IP及開發(fā)工具的支持能力,使FPGA在系統(tǒng)中的角色越來越重要;近年來更直接從“配角”升級為"主角"。FPGA的SOC系統(tǒng)化對助力FPGA廠商立足市場更是百利而無一害。

FPGA將替代ASIC?持久戰(zhàn)!

依據(jù)市調(diào)公司的研究數(shù)據(jù)來看,ASIC的確受到FPGA的沉重壓力。Gartner分析,受全球金融風(fēng)暴影響,2009年起FPGA取代ASIC的趨勢更為明顯,兩者采用比重已經(jīng)達到30:1。由于成本因素,許多公司紛紛延后甚至取消ASIC的設(shè)計方案。

采用FPGA,讓工程師免去開發(fā)ASIC的高成本,同時能獲得ASSP所缺少的差異化,這使得軍事、工業(yè)和網(wǎng)通等產(chǎn)業(yè),成為FPGA的主力市場。隨著制程不斷升級,加上各大廠商推出低價化和超低功耗產(chǎn)品后,讓FPGA直闖高量產(chǎn)市場。

只不過,這意味著ASIC被宣判死刑。但是,難道這就意味著FPGA從此可以躺著賺了嗎?倒也未必。盡管FPGA在功耗方面有所進步,但比起ASIC仍嫌不足,特別是在動態(tài)與靜態(tài)電源管理及漏電等問題上。此外,在高量產(chǎn)市場,短期內(nèi)FPGA仍舊難敵ASIC既有的成本優(yōu)勢。然而說會從此取代ASIC仍言之過早,畢竟28納米FPGA是否真能對市場產(chǎn)生決定性影響,還有待時間觀察。而這段時間,ASIC也將持續(xù)精進。因此這場戰(zhàn)爭并非結(jié)束,其實反倒可以期待一場新局面的開始。

3D堆疊打造異質(zhì)系統(tǒng)

3D IC技術(shù)在市場上醞釀已久,卻遲遲停留在只聞樓梯響,不見人下來的階段。然而,3D堆疊架構(gòu)對于芯片間的異質(zhì)性整合,其實扮演著十分重要的角色,特別是極力打造SoC芯片的半導(dǎo)體設(shè)計商們。而3D堆疊的芯片整合方式,將在FPGA上率先實現(xiàn)。

目前FPGA廠商Xilinx在其高階元件上,已經(jīng)開始采用3D堆疊架構(gòu)。這也是全球首款異質(zhì)的3D FPGA芯片,主要技術(shù)基礎(chǔ)是透過SSI(堆疊芯片互聯(lián)),將 FPGA與收發(fā)器進行整合,這同時也是一種創(chuàng)新。Xilinx未來更多的FPGA產(chǎn)品,包括最新的ZYNQ平臺,都會采用3D堆疊的方式來設(shè)計。

3D堆疊,無疑將成為FPGA未來征服市場的又一大利器。特別是未來FPGA將朝向SoC方向發(fā)展,透過3D立體堆疊,讓FPGA的整合之路將更為順暢。

電子發(fā)燒友網(wǎng)編輯觀點

FPGA從以前的“配角”到“主角”得益于28nm新進程的應(yīng)用、3D堆疊以及SoC系統(tǒng)化等發(fā)展方向的確定。FPGA想要制霸市場、對市場產(chǎn)生任何決定性的作用,就一定得拽緊這三大“法寶”,從而繼續(xù)“抗戰(zhàn)”ASIC。同時FPGA廠商固然不會固步自封,就像之前FPGA市場中的28nm爭霸戰(zhàn)【詳情參閱:Xilinx緊逼Altera,哪家FPGA更好? 】和20nm預(yù)決賽【詳情參見:清算Xilinx與Altera“流水賬”,不只是角逐戰(zhàn)?? 】一樣,說不定以后還會出現(xiàn)更高層次的對壘。未來的戰(zhàn)場只會愈發(fā)精彩。在今后的戰(zhàn)場中,不然還會迸發(fā)出更為精妙絕倫的新技術(shù)、新產(chǎn)品和創(chuàng)新性思維!敬請期待!

RADX、Xilinx和ADI聯(lián)合演示先進的可編程EdgeQAM技術(shù)方案

2012年10月22日,RADX Technologies公司、賽靈思公司和ADI公司在2012年SCTE有線電視技術(shù)展會上聯(lián)合演示了業(yè)界最具擴展性的EdgeQAM可編程解決方案。這些創(chuàng)新的解決方案使有線電視設(shè)備OEM廠商能夠開發(fā)和部署各種新一代EdgeQAM產(chǎn)品,滿足有線電視運營商對要求最高QAM應(yīng)用的各種需求, 從酒店應(yīng)用到完整融合有線接入平臺(CCAP)解決方案。

EdgeQAM技術(shù)解決方案采用了賽靈思聯(lián)盟計劃認證成員RADX公司的FrontierEQ? IP、賽靈思的28nm Kintex?-7和/或Virtex?-7 FPGA,以及ADI公司的AD9129 DAC,使OEM廠商能夠部署低成本、低功耗且極其先進的可編程系統(tǒng)。

RADX IP包含可在單個FPGA中支持32至160個單播頻道和多達640個單播/廣播頻道的J.83 Annex A/C/B內(nèi)核;支持特定頻率范圍內(nèi)通道任意布置的捷頻數(shù)字上變頻器(DUC);以及采用ADI許可的非線性校正技術(shù),用于提升整個有線電視頻譜范圍內(nèi)的DAC線性度的數(shù)字預(yù)失真(DPD)模塊。

前瞻性

RADX、賽靈思、ADI聯(lián)合打造的 EdgeQAM技術(shù)解決方案最大的優(yōu)勢之一,就是具備可編程的功能。

前所未有的高可擴展性、通道密度和低功耗性能

以FPGA為基礎(chǔ)的EdgeQAM產(chǎn)品的另一大優(yōu)勢是,OEM廠商可以將他們的電子元器件集成到單個芯片中,以降低材料清單(BOM)成本和功耗要求,這是新一代EdgeQAM系統(tǒng)的主要行業(yè)要求。

高靈活性與高性能

該解決方案采用了FrontierEQ捷頻DUC和NLC,結(jié)合使用新型Analog Device AD9129,可讓OEM廠商及其客戶實時地在任何頻率上布置通道,且能夠在整個有線電視頻段上實現(xiàn)超過45dB的平均均衡調(diào)制誤差率(MER)。這種高度的靈活性和卓越的性能讓OEM廠商能夠輕松地滿足嚴(yán)格的DRFI和CCAP RF標(biāo)準(zhǔn)要求。

參考平臺方法

為簡化OEM廠商的開發(fā)工作,加速產(chǎn)品上市進程,RADX已開發(fā)出一系列集成式FrontierEQ EdgeQAM RADX FrontierEQ參考平臺。借助FrontierEQ參考平臺,OEM廠商幾乎一夜之間就能夠完成組件的集成和運行工作,無需在此花費過多寶貴的設(shè)計時間。

更多詳細內(nèi)容及業(yè)界評價請繼續(xù)瀏覽:【 先進的可編程EdgeQAM技術(shù)方案 】

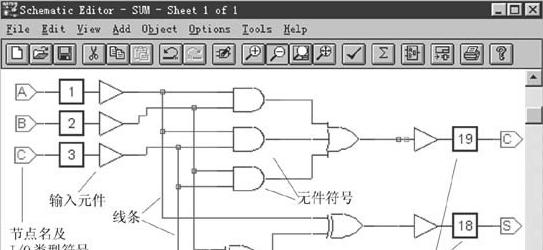

電子發(fā)燒友網(wǎng)訊:各位FPGA愛好者們,您打算提高自己的設(shè)計技巧,更迅速的完成項目嗎?Altera公司提供免費在線培訓(xùn)課程,該課程是由經(jīng)驗豐富的工程師和系統(tǒng)規(guī)劃人員開發(fā)的,能幫助您前所未有的深入了解FPGA設(shè)計的關(guān)鍵點。詳情見本文,也可登錄到官網(wǎng)了解相信信息。

這里列出了一些您目前可以觀看的免費在線培訓(xùn)新課程:

課程1:怎樣開始一個簡單的FPGA設(shè)計

課程2:通過系統(tǒng)控制臺進行調(diào)試

課程3:縮短您的編譯時間!

課程4:在1個小時內(nèi)基本了解收發(fā)器

培訓(xùn)課程詳情請關(guān)注:【免費參加Altera在線培訓(xùn)課程 】

10月14日成功發(fā)射的實踐九號A、B衛(wèi)星上衛(wèi)星控制計算機目前在軌工作穩(wěn)定,其中實踐9B衛(wèi)星控制計算機的核心是我國首枚應(yīng)用于航天的片上系統(tǒng)芯片SoC2008,由中國航天科技集團公司五院502所自主研制,具有完全自主知識產(chǎn)權(quán)。這標(biāo)志著我國已經(jīng)全面突破和掌握了SoC系統(tǒng)級設(shè)計、抗輻射加固設(shè)計、容錯設(shè)計、高可靠實時操作系統(tǒng)設(shè)計以及驗證等關(guān)鍵技術(shù),在國內(nèi)國際上均處于領(lǐng)先地位。

SoC技術(shù)是微電子技術(shù)發(fā)展到高級階段的必然產(chǎn)物。SoC技術(shù)為系統(tǒng)設(shè)計人員提供了一種全新的設(shè)計思路和手段,即在單一芯片上實現(xiàn)系統(tǒng)功能。采用SoC技術(shù)以后,航天型號不再處于持續(xù)基于國外計算機芯片進行設(shè)計的局面,而可以立足于國內(nèi)設(shè)計、生產(chǎn)和工藝水平,更加合理地確定航天電子產(chǎn)品技術(shù)方案、系統(tǒng)架構(gòu)和性能指標(biāo),并根據(jù)航天的需要進行自主的改進和提高,逐步實現(xiàn)更高端國產(chǎn)化。因此SoC技術(shù)是擺脫核心元器件受制于人的具有戰(zhàn)略意義的關(guān)鍵技術(shù)。

502所研制的SoC2008是一款面向航天電子系統(tǒng)應(yīng)用的高性能、低功耗的抗輻射加固的片上系統(tǒng)芯片,它可滿足各類星載電子系統(tǒng)的應(yīng)用需求。 SoC2008的整體性能指標(biāo)與歐洲2010年推出的產(chǎn)品相當(dāng),達到國際同期先進水平。SoC2008目前已確定應(yīng)用于CAST100小衛(wèi)星平臺控制計算機、衛(wèi)星小型化長壽命星敏感器、衛(wèi)星著陸上升器中心控制單元、空間站機械臂分系統(tǒng)控制器、貨運飛船GNC分系統(tǒng)制導(dǎo)、導(dǎo)航與控制計算機監(jiān)測單元等產(chǎn)品中。

SoC2008的成功上天應(yīng)用是502所多部門配合、通力合作的結(jié)晶。在歷時近5年的研制過程中,502所SoC研制團隊積極發(fā)揚吃苦耐勞和嚴(yán)慎細實的工作作風(fēng),矢志創(chuàng)新、引領(lǐng)前沿,通過采用新技術(shù)和新方法,屢克技術(shù)難關(guān),取得了SoC2008的一次性流片和應(yīng)用成功,并為SoC技術(shù)在后續(xù)型號的成功應(yīng)用打下了堅實的基礎(chǔ)。

Kalray公司完成256核處理器28nm SoC設(shè)計

電子發(fā)燒友網(wǎng)訊【編譯/Triquinne】:通過使用Mentor Graphics公司的設(shè)計和測試工具,Kalray公司完成256核處理器28nm SoC設(shè)計。

近日,Mentor Graphics公司宣布Kalray公司已經(jīng)完成了其多功能處理器陣列集成電路的設(shè)計。該集成電路具有1.6億個門和30億晶體管。該設(shè)計是在Mentor Graphics公司的功能驗證、物理設(shè)計、物理驗證和可測試性設(shè)計流和Questa、奧林巴斯soc、Calibre和Tessent產(chǎn)品套件的基礎(chǔ)上完成的。

Kalray公司 MPPA-256多核處理器是一個256核的SoC,具備47MB的內(nèi)存芯片。它使用28nm制程工藝技術(shù)實現(xiàn),包括16個處理器的16個叢集排列,并通過高速低延遲網(wǎng)絡(luò)芯片彼此通訊,就像是數(shù)據(jù)中心的大型集群計算機一樣。多個 MPPA 晶片可透過 Interlaken 介面在PCB板級實現(xiàn)互連,以提高處理器陣列的尺寸與性能。MPPA多核處理器的目標(biāo)市場是嵌入式計算機市場領(lǐng)域,如圖像和信號處理、科學(xué)計算、數(shù)據(jù)安全、工業(yè)、航空和運輸?shù)取?/p>

Kalray公司采用基于OVM的功能驗證方法,使用Mentor公司的Questa產(chǎn)品(該產(chǎn)品能提供支持Questa驗證IP庫中的AXI協(xié)議)。對物理設(shè)計(布局)而言,Kalray公司使用奧林巴斯SoC 布局布線系統(tǒng)。因為該系統(tǒng)具有多線程布線和時序分析、具有基于多電壓流的多角多核模式、內(nèi)部具有內(nèi)置Calibre signoff。Calibre平臺包括Calibre 納米LVS和DFM平臺。該平臺因其大容量和高可靠性而受到廣泛應(yīng)用。Kalray公司能夠在具有160個CPU的多線程模式上運行DRC,以達到減少周轉(zhuǎn)時間的目的。Kalray公司選擇Tessent silicon測試平臺用于存儲器內(nèi)置自測的實現(xiàn)以及高壓自動測試模式的生成。

kalray公司的設(shè)計運行在多達160個處理器的多線程模式下,能夠減少周轉(zhuǎn)時間。kalray選擇tessent硅試驗存儲器內(nèi)建自測試的軟件平臺和高壓自動測試模式生成,兩者都能做到固定和高速過渡故障測試。

華為ASIC設(shè)計案,F(xiàn)PGA雙雄勝算幾何?

電子發(fā)燒友網(wǎng)訊:中國通信網(wǎng)絡(luò)設(shè)備廠商華為正在其部分產(chǎn)品中或采用ASIC以取代Altera的FPGA。這項進展將影響Altera的銷售,并可能打擊“FPGA正在取代ASIC傳統(tǒng)地位”頗具爭議性的說法。華為首次采用ASIC到底會對Altera的銷售有何影響?FPGA和ASIC之間的拉鋸戰(zhàn)到底誰的勝算更大?詳情請參閱本文分析報道。

華為或?qū)⑹状尾捎肁SIC

Altera總裁、主席兼CEO John Daane在10月23日的第三季度營收報告中表示,有兩個客戶在近月內(nèi)將三種產(chǎn)量大的設(shè)計轉(zhuǎn)向了ASIC。Daane并沒有指出客戶的名字,但他說其中一個是Altera最大的客戶,相信應(yīng)該是華為。

根據(jù)JP摩根分析師Christopher Danely的說法,華為占據(jù)Altera第三季度銷售額的16%,是Altera最大的客戶。Danely表示,華為是最后一個只采用可編程邏輯的電信設(shè)備OEM廠商。

根據(jù)周二的一份報告,Danely說他認為華為是FPGA最大的買家,每年花費3.5億美元,也就是華為年度應(yīng)收的1%來購買FPGA。 他說,華為每年從Altera采購的FPGA價值3億美元。

為何選擇FPGA和ASIC混合設(shè)計模式?

大多電信設(shè)備制造商從最開始廣泛使用自己開發(fā)的專用集成電路(ASIC),到后來對能為其提供更多靈活的解決方案的FPGA的青睞,再到現(xiàn)在對FPGA和ASIC的混合芯片技術(shù)的摩拳擦掌,無一不證明著電信設(shè)備制造商對更高品質(zhì)、更低功耗、更短上市時間和更低成本的無限追求。當(dāng)然,作為全球領(lǐng)先的信息與通信解決方案供應(yīng)商的華為公司也不會例外。

華為到底會選擇哪種技術(shù)呢?據(jù)電子發(fā)燒友網(wǎng)編輯的深入分析,華為或?qū)⒉捎肍PGA和ASIC的混合芯片技術(shù),其主要原因有三點。(因篇幅問題,具體原因,詳見本文最后的原文鏈接。)

至于華為最終會選擇Altera公司還是Xilinx公司合作,本站編輯認為Xilinx在堆疊硅片互聯(lián)技術(shù)上的創(chuàng)新舉措將會在此次角逐中贏得不可或缺的優(yōu)勢。再者,我們或許能從上文Altera公司領(lǐng)導(dǎo)John Daane的觀點中分析出些端倪。接下來,電子發(fā)燒友網(wǎng)編輯將會為各位作進一步分析。

搶食華為設(shè)計案,Xilinx與Altera誰將勝出?

JP摩根分析師Christopher Danely預(yù)估,隨著華為從只使用可編程邏輯到混合使用ASIC和可編程邏輯的變化,Altera明年的年營業(yè)額將損失1.5億美元左右。Danely說道,類似的可編程邏輯收入下降發(fā)生在數(shù)年前,EMC公司從只采用FPGA的模式轉(zhuǎn)向采用FPGA和ASIC的混合模式。

Danely說,讓Altera情況更糟的是,另一可編程邏輯市場領(lǐng)導(dǎo)者賽靈思(Xilinx)將從其與華為的首批設(shè)計案(design win)中獲益。為什么預(yù)測AlteraAltera情況會“糟”,Xilinx會從中受益?可參考原文。

電子發(fā)燒友網(wǎng)編輯評論

對于華為將首次采用ASIC的事件,相信勢必會在整個行業(yè)產(chǎn)生影響。可以預(yù)測的是,若此事件演變成事實后,Altera營業(yè)銷售亦將由此而受到不可忽視的影響。根據(jù)以上的種種分析,由于堆疊硅片互聯(lián)技術(shù)的創(chuàng)新舉措,作為Altera老冤家的可編程邏輯市場領(lǐng)導(dǎo)者賽靈思(Xilinx)或?qū)⒃谌A為的首批設(shè)計案(design win)中獲益。“FPGA正在取代ASIC傳統(tǒng)地位”的說法或再一次受到?jīng)_擊,那FPGA和ASIC究竟孰優(yōu)孰劣?華為將首次使用ASIC事件會對Altera和Xlinx這兩大巨頭及其FPGA市場產(chǎn)生何種影響?歡迎大家積極討論。更多進展與動態(tài),敬請關(guān)注電子發(fā)燒友網(wǎng)的后續(xù)報道。

為何選擇FPGA和ASIC混合設(shè)計模式?搶食華為設(shè)計案,Xilinx與Altera誰將勝出?電子發(fā)燒友網(wǎng)編輯會做出怎樣的評論?請繼續(xù)瀏覽原文:【華為ASIC設(shè)計案,F(xiàn)PGA雙雄勝算幾何? 】

——電子發(fā)燒友網(wǎng)整合,本站版權(quán)所有,轉(zhuǎn)載請注明出處!

電子發(fā)燒友App

電子發(fā)燒友App

評論