Cadence宣布業內首個DDR4 Design IP解決方案在28納米級芯片上得到驗證

2012-09-10 09:53:24 1403

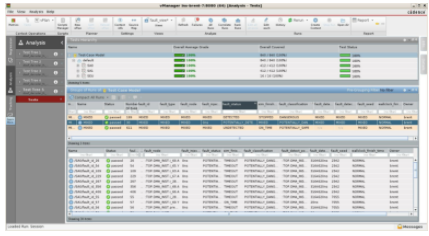

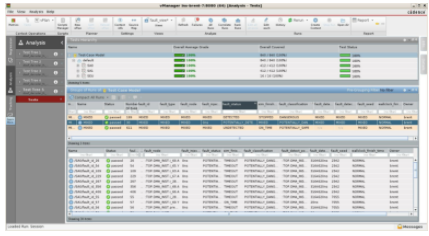

1403 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS),近日推出新版本Incisive Enterprise Simulator,該版本將復雜SoC的低功耗驗證效率提高了30

2013-05-14 10:31:40 1832

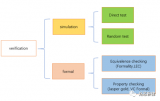

1832 確保汽車 SoC 在功能上安全還可以讓駕駛員和乘客對他們的車輛充滿信心。將安全驗證集成到功能驗證流程中可以是加快流程和管理符合 ISO 26262 等標準的工作的有效方法。

2022-06-15 16:09:40 3256

3256

汽車外,還有很多其他行業也能從電子器件的增加受益,當然保障功能安全是大的前提。本文討論SOC芯片設計驗證、驗證計劃和策略以及驗證方法。它定義了功能模擬、功能覆蓋、

2023-07-31 23:45:12 836

836

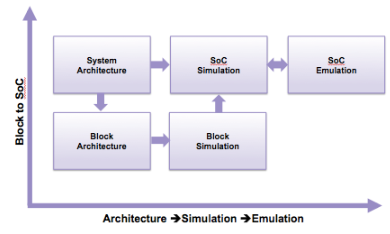

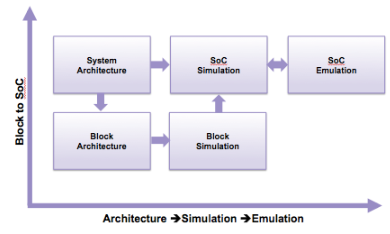

SoC芯片的規模一般遠大于普通的ASIC,同時深亞微米工藝帶來的設計困難等使得SoC設計的復雜度大大提高。仿真與驗證是SoC設計流程中最復雜、最耗時的環節,約占整個芯片開發周期的50%~80%,采用

2019-10-11 07:07:07

SoC驗證超越了常規邏輯仿真,但用于加速SoC驗證的廣泛應用的三種備選方法不但面臨可靠性問題,而且難以進行權衡。而且,最重要的問題還在于硬件加速訪問權限、時機及其穩定性。

2019-11-11 06:37:11

由于片上系統(SoC)設計變得越來越復雜,驗證面臨著巨大的挑戰。大型團隊不斷利用更多資源來尋求最高效的方法,從而將新的方法學與驗證整合在一起,并最終將設計與驗證整合在一起。雖然我們知道實現驗證計劃

2019-07-11 07:35:58

通用的驗證相關實用程序。 OVM 版本將采用 Apache 2.0 許可,任何人都可以將 OVM 庫用于任何目的,包括創建衍生作品。 OVM 由 Cadence 和 Mentor Graphics

2022-02-13 17:03:49

ALLEGRO導出CSV格式的坐標文件該方案是本人使用cadence allegro 17.2版本驗證。16.6版本待驗證。具體操作如下1、Tools→Reports2、找到placed component report并雙擊

2019-07-04 21:21:47

Graphics公司Veloce驗證平臺在超大規模IC系統中仿真驗證的應用。借助Veloce的高速和大容量的特性,極大的提高功能驗證的效率,解決由于芯片規模大FPGA無法驗證的問題,保證芯片的按時投片

2010-05-28 13:41:35

我用quartus II調用modelsim仿真fft ip核,仿真結束后我想驗證下數據是否正確,結果是:我用matlab生成同樣的整形數據,然后用modelsim仿出的結果txt文件與用

2012-09-20 12:48:37

小編前段時間幫客戶找到一些人解決了SOC驗證環境的問題。在招人的時候我們和不少人進行了溝通交流,從中發現SOC驗證環境一千家公司有一千家公司的做法。那么一個優秀的SOC驗證環境應該具備哪些功能呢

2022-05-31 11:39:18

隨著系統芯片(SoC)設計的體積與復雜度持續升高,驗證作業變成了瓶頸:占了整個SoC研發過程中70%的時間。因此,任何能夠降低驗證成本并能更早實現驗證sign-off的方法都是眾人的注目焦點。

2019-08-26 07:06:04

的新方法,提高了驗證效率。論文還研究了運用形式驗證的方法對RTL級和RTL級以及RTL級和門級網表進行等價性驗證。為了進一步保證RTL級設計和對應的全定制設計模塊之間功能的等價性,設計了一個能同時考察兩種

2011-12-07 17:40:14

onchip,片上系統)開發效率和質量的重要手段。如果能對IP核進行驗證、測試和集成.就可以加速SoC的設計,而這需要從以下5個方面進行考慮。代碼純化.指在代碼設計中及完成后進行自定義的、IEEE標準

2021-09-01 19:32:45

制用于將外部驗證環境融入到在系統CPU上運行的軟件。ST Microelectronics驗證工程師可以使用VAL對內部設計IP和外部驗證組件進行編程和配置。“我們為早期項目開發的這個機制在模擬中運行

2017-04-05 14:17:46

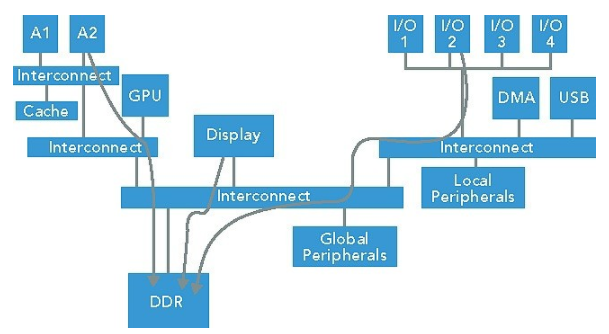

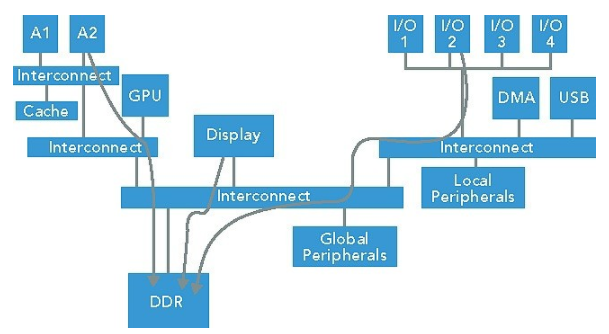

SoC系統驗證平臺總體框架是怎樣的?SoC系統驗證平臺如何去構建?

2021-04-28 07:13:41

上次說到CPU的boot,今天說說SOC環境的另外一種啟動方式。用C啟動SOC驗證環境有幾個問題。一是CPU boot過程比較慢,每次仿真前都需要很長的一段初始化時間。二是IP驗證環境的測試用例無法

2022-06-17 14:41:50

SoC與IP有什么關系?如何去驗證IP?

2021-04-28 06:02:37

請問一下,如何利用AMSVF來進行混合信號SoC的全芯片驗證?

2021-05-06 07:56:08

固網短信電話專用SoC芯片介紹一種數模混合SoC設計協同仿真的驗證方法

2021-04-23 06:06:39

、包和庫,特別是半導體知識產權 (IP) 核心設計過程,包括以下章節:驗證方法——概述驗證方法——簡介驗證 IP - 方法論的作用如何選擇驗證方法基于標準的 IP 和 SoC 的驗證方法功能驗證方法

2022-11-26 20:43:20

數模混合信號仿真已經成為SoC芯片驗證的重要環節。文章以一款固網短信電話專用SoC芯片為例,介紹一種使用Synopsys公司的NanoSim-VCS協同仿真環境進行仿真的驗證方法,并給出驗證結

2009-05-15 15:41:26 19

19 數模混合信號仿真已經成為SoC芯片驗證的重要環節。文章以一款固網短信電話專用SoC芯片為例,介紹一種使用Synopsys公司的NanoSim-VCS協同仿真環境進行仿真的驗證方法,并給出驗證結

2009-05-15 15:41:26 5

5 探討了IP 核的驗證與測試的方法及其和VHDL 語言在IC 設計中的應用,并給出了其在RISC8 框架CPU 核中的下載實例。關鍵詞:IP 核;片上系統;驗證

2009-06-15 10:59:14 32

32 本文針對目前芯片驗證中出現的瓶頸問題,闡述了當前流行的驗證技術和部分硬件驗證語言。文中介紹了SystemC 和E 語言,以及多種功能驗證技術。最后通過對Rana接口芯片的功

2009-08-13 08:44:19 27

27 近幾年來,SoC 技術已經得到了迅速的發展,隨之而來的是 SoC 設計的驗證也變得更加復雜,花費的時間和人力成倍增加。一個SoC 芯片的驗證可能會用到多種驗證技術,常用的 SoC 的

2009-08-31 10:33:25 24

24 本文首先介紹RVM驗證方法學和覆蓋率驅動技術,然后詳細分析如何使用結合覆蓋率驅動技術的RVM驗證方法學對SOC(System On Chip)進行完備的功能驗證, 最

2009-09-05 08:53:00 15

15 ESL 設計和驗證方法使設計工程師能夠專注于那些給產品及IP 帶來差異化和價值的系統設計屬性,即功能性和性能。本文討論電子系統級(ESL)設計和驗證方法學在系統級芯片(SoC)設

2009-11-30 16:15:15 33

33 本文從SoC (System on a Chip)驗證環境外在的框架結構、內在的驗證數據的組織與管理和體現其工作原理的系統腳本的設計思想三方面出發,討論SoC 驗證環境的搭建方法,并搭建的驗證環

2009-12-14 09:52:58 22

22 本文介紹了基于事務的SoC驗證方法,詳細說明了事務、事務處理器的概念和事務級驗證平臺的功能結構。Synopsys公司的RVM驗證方法學是當前比較流行的基于事務的SoC驗證方法,文中詳細

2010-02-24 11:44:04 8

8 提高算法驗證以及目標硬件實施的效率

2010-07-16 18:05:42 12

12 無線溫度驗證系統 溫度壓力一體 溫度驗證儀分有線系統與無線系統。有線的溫度驗證系統精度低,價格相對于無線產品的價格要低廉的多,無線驗證系統操作方便,節省時間,而有線布線特別麻煩。所以在某些全封閉

2023-12-20 10:10:23

IP驗證增量仿真技術的運用

驗證涉及每個階段的迭代循環:仿真、檢查結果,改變激勵或設計或調試設置,重新仿真并不斷重復。在系統調

2009-01-27 17:58:24 834

834 Cadence推出首個TLM驅動式設計與驗證解決方案

Cadence設計系統公司今天推出首個TLM驅動式協同設計與驗證解決方案和方法學,使SoC設計師們可以盡享事務級建模(TLM)的好處。

2009-08-07 07:32:00 674

674 Cadence推出首個TLM驅動式設計與驗證解決方案提升基于RTL流程的開發效率

Cadence設計系統公司推出首個TLM驅動式協同設計與驗證解決方案和方法學,使SoC設計師們可以盡

2009-08-11 09:12:18 499

499 Cadence為PCI Express 3.0推出首款驗證解決方案

Cadence設計系統公司宣布其已經開發了基于開放驗證方法學(OVM)的驗證IP(VIP)幫助開發者應用最新的PCI Express Base Specification

2009-11-04 16:59:59 1142

1142 設計與驗證復雜SoC中可綜合的模擬及射頻模型

設計用于SoC集成的復雜模擬及射頻模塊是一項艱巨任務。本文介紹的采用基于性能指標規格來優化設計(如PLL或ADC等)的方

2009-12-26 14:38:13 557

557

芯邦采用Cadence Incisive Xtreme III系統提升SoC驗證實效

全球電子設計創新領先企業Cadence設計系統公司今天宣布,位于中國深圳的、無晶圓廠集成電路設計領先企業芯邦科

2010-03-02 10:32:47 573

573 全球電子設計創新領先企業Cadence設計系統公司,今天宣布了業界最全面的用于系統級芯片(SoC)驗證的通用驗證方法學(UVM)開源參考流程。為了配合Cadence EDA360中SoC實現能力的策略,

2010-06-28 08:29:14 2240

2240 Cadence設計系統公司600多種新功能擴展了指標驅動型驗證(MDV)的范圍,幫助工程師實現更快、更全面的驗證閉合與硅實現。

2011-01-13 11:26:17 768

768 Cadence Incisive Conformal ASIC是Incisive驗證平臺等效檢查解決方案的一部分,設計者無需測試向量就能驗證和調試數百萬門的設計。它組合了業界最優的等效檢查工具和擴展功能檢查,數據路

2011-04-13 23:40:45 17

17 電子設計創新企業Cadence設計系統公司(NASDAQ: CDNS)今天宣布,中國科學院計算技術研究所(簡稱計算所)采用了Cadence? Incisive?Xtreme Ⅲ? 系統,來加速其下一代6400萬門以上龍芯3號高級多

2011-05-27 10:49:34 646

646 IP核驗證平臺采用6層板PCB設計,使用獨立的外部時鐘同步芯片,可以為PCI及其它接口提供穩定的零延遲時鐘系統電路,滿足PCI總線的時鐘要求,使驗證平臺高速,穩定,可靠的工作。

2012-01-17 14:02:19 1501

1501

本文利用Altera公司的FPGA開發工具對皋于國產龍芯I號處理器IP核的SoC芯片進行ASIC流片前的系統驗證,全實時方式運行協同設計所產生的硬件代碼和軟件代碼,構建一個可獨立運行、可現場

2012-04-21 15:22:01 3161

3161

芯片驗證的工作量約占整個芯片研發的70%,已然成為縮短芯片上市時間的瓶頸。應用OVM方法學搭建SoC設計中的DMA IP驗證平臺,可有效提高驗證效率。

2012-06-20 09:03:29 2627

2627 電子設計創新企業Cadence設計系統公司,今天宣布使用ARM AMBA協議類型的Cadence驗證IP(VIP)實現多個成功驗證項目,這是業界最廣泛使用的AMBA協議系列驗證解決方案之一。頂尖客戶,包括

2012-11-07 08:21:52 997

997 通過對Evatronix公司的收購,Cadence就能順理成章地進入移動、連線與云端市場領域。Evatronix公司提供的獲得芯片驗證的IP產品陣容,包括公認的 USB 2.0 /3.0、顯示器

2013-05-20 09:27:46 2397

2397 9月26日——全球電子設計創新領先企業Cadence設計系統公司(納斯達克股票代碼:CDNS)今天宣布可提供業界首款支持全新HDMI 2.0規范的驗證IP(VIP)。這款VIP使設計師們可以快速

2013-09-27 16:19:08 857

857 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS)今天發布了新版 Incisive? 功能驗證平臺,再一次為整體驗證性能和生產率設定新標準。

2014-01-16 17:36:13 1047

1047 日益增長的驗證復雜性正推動著包括形式分析的多種互補驗證方法的需求,而 Jasper是快速增長形式分析行業的領導者,目標針對各種復雜驗證的挑戰,Cadence與Jasper的結合將擴大產業最強與最廣泛的系統驗證產品的差異性優勢。

2014-04-25 18:32:48 2326

2326 SoC基于IP設計的特點使驗證項目中多語言VIP(Verification IP)協同驗證的需求不斷增加,給驗證工作帶來了很大的挑戰。為了解決多語言VIP在SoC驗證環境靈活重用的問題。提出了一種

2015-12-31 09:25:13 12

12 基于IEEE1500標準的IP核測試殼的設計與驗證_馮燕

2017-01-07 19:00:39 23

23 ? 可以顯著縮短片上系統(SoC)面市時間。較Cadence上一代仿真平臺,Xcelium? 單核版本性能平均可提高2倍,多核版本性能平均可提高5倍以上。

2017-03-01 15:57:05 3341

3341 2017年3月2日,上海——楷登電子(美國 Cadence 公司,NASDAQ: CDNS)今日發布全新基于FPGA的Protium? S1原型驗證平臺。借由創新的實現算法,平臺可顯著提高工程生產

2017-03-02 11:13:11 2744

2744 參數化的IP是可配置的,這意味著在不同的SOC中IP設計可以有不同的設計參數,設計參數可以對應到協議、端口號、端口名稱、以及內部邏輯。大量的IP設計參數非常影響驗證環境的構建,比如testbench

2017-09-15 14:37:34 6

6 功能驗證正成為IP 驗證的瓶頸,并影響到整個設計團隊。設計工程師想方設法提高驗證效率,以實現整個芯片設計的最佳利益。在這里,我們提供10 個簡單技巧,顯著提升您的IP 驗證效率。 1.參與驗證計劃

2017-10-19 09:17:23 8

8 技術方法,驗證了SoC系統、DSP指令、硬件IP等。實驗證明,此FPGA驗證平臺能夠驗證SoC設計,提高了設計效率。

2017-11-17 03:06:01 13138

13138

技術方法,驗證了SoC系統、DSP指令、硬件IP等。實驗證明,此FPGA驗證平臺能夠驗證SoC設計,提高了設計效率。

2017-11-17 03:06:01 3769

3769

本文檔內容介紹了基于零成本快速完成 SoC 概念驗證,供參考

2018-03-19 11:21:52 5

5 為了充分利用系統級芯片(SoC)設計帶來的優點,業界需要一種可以擴展的驗證解決方案,解決設計周期中各個階段的問題,縮短驗證鴻溝。本文將探討可擴展驗證解決方案為何能夠以及如何解決SoC設計目前面臨的功能方面的嚴峻挑戰,以達到提高設計生產力、保證設計質量、縮短產品上市時間以及提高投資回報率的目的。

2018-06-04 03:13:00 743

743

版圖驗證是指采用專門的軟件工具,對版圖進行幾個項目的驗證,例如是否符合設計規則?版圖和電路圖是否一致?版圖是否存在短路、斷路及懸空的節點?借助于計算機和Cadence軟件的功能,對版圖設計進行高效而全面的驗證。經過版圖驗證后,一次流片成功率大大提高。

2018-04-20 15:56:47 0

0 在片上系統的設計與實現中,驗證這一環節日益重要,整個過程中花在驗證的時間比重越來越大,主要原因在于隨著SOC 芯片復雜度的提高,驗證的規模也成指數級的增加。系統芯片的時代已經到來,在RTL級硬件

2018-06-01 07:18:00 1367

1367 復旦大學微電子學院某國家重點實驗室內部教學視頻:基于ZYNQ FPGA與PC的IP設計與驗證方案。

關鍵詞:IP設計,IP驗證,AXI總線協議,ARM,UDP傳輸,PYTHON

2019-08-06 06:16:00 1968

1968

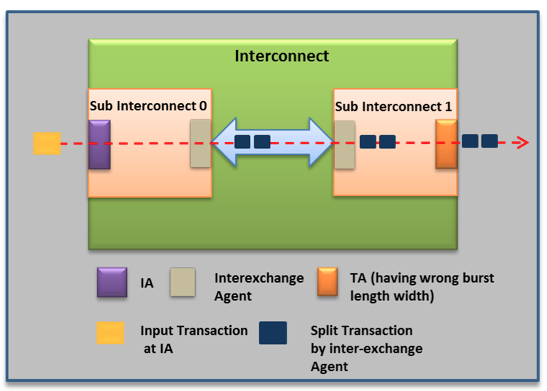

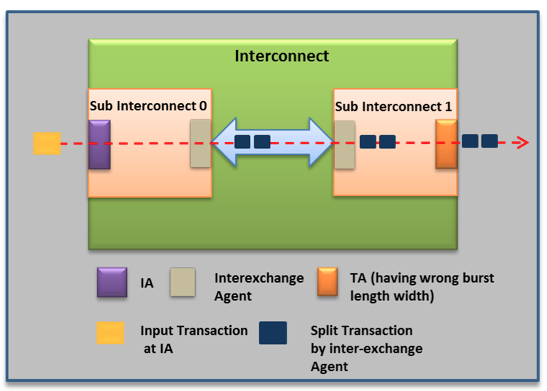

在我們之前的博客中,我們提到驗證NoC系統遠遠超出了事務路由檢查。我們能夠在SoC級別的復雜互連驗證期間捕獲各種問題,其中NoC具有20多個總線主控器,80多個總線從器件,以及具有不同總線協議的多個

2019-08-12 11:22:54 2299

2299

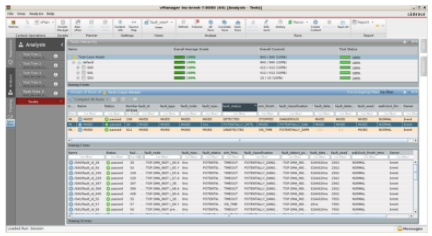

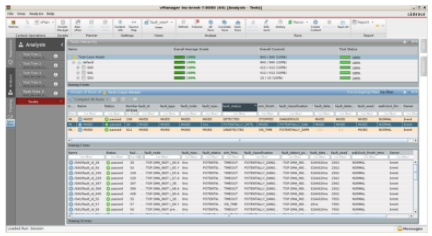

,已成為驗證進程管理的棘手問題。本文主要跟小伙伴們聊一聊智能跟蹤SoC驗證進度的方法。 EDA工具兩大巨頭Synopsys和Cadence都有自己的驗證計劃工具,分別是Synopsys公司

2021-03-28 10:52:02 3292

3292

SoC設計中的驗證技術有哪些。

2021-03-29 10:37:30 12

12 Cadence擁有最完整的IP與SoC驗證、硬件與軟件回歸測試及早期軟件開發的全系列解決方案。

2021-04-06 13:48:53 2431

2431 的頻段與帶寬,使得測試驗證的復雜度也隨之提高。 ? 如何提高PA的設計驗證效率? ? 如何真實地反映PA本身的EVM指標? ? 為什么經常遇到不同的測試儀表平臺的EVM測試結果有很大差別? 相信這些都是大家在平時的工作中常遇到的困擾,基于此,我們總結

2021-11-05 15:24:34 2494

2494 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,SK hynix Inc. 已部署 Cadence? Spectre? FX Simulator 仿真器,用于對其面向 PC 和移動應用的 DDR4 和 DDR5 DRAM 進行基于 FastSPICE 的功能驗證。

2022-04-08 14:49:00 1565

1565 Cadence Clarity 3D Solver 2022版本發布 電磁設計同步分析功能提高效率 最新的電磁設計同步分析功能有助于提高 IC、IC 封裝和高性能 PCB 設計的速度。 美國加州

2022-04-29 14:42:29 4770

4770 擁有如此多的利益相關者和優先事項正在推動迫切需要一種更好的方法來完成 SoC 驗證。軟件定義的驗證和驗證環境和方法將使工程團隊能夠交付復雜的 SoC,滿足上市時間,提供更徹底的檢查,并降低風險和成本。

2022-06-02 10:00:02 1034

1034 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布推出 15 種新的驗證 IP(VIP)解決方案,助力工程師迅速有效地驗證設計,以滿足最新標準協議的要求。

2022-06-06 11:18:21 2665

2665 確保汽車 SoC 在功能上安全還可以讓駕駛員和乘客對他們的車輛充滿信心。將安全驗證集成到功能驗證流程中可以是加快流程和管理符合 ISO 26262 等標準的工作的有效方法。

2022-06-13 15:17:20 1177

1177

面對持續不斷的上市時間壓力和日益復雜的 SoC 設計,很難找到不想從設計周期中縮短時間的工程師。特別是在高級節點,驗證 SoC 互連已成為一個耗時的步驟。但是,工具現在可以高效且有效地執行周期精確的性能分析和互連驗證。

2022-06-14 10:12:17 1692

1692

利用Systemverilog+UVM搭建soc驗證環境

2022-08-08 14:35:05 5

5 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,瑞薩電子(Renesas Electronics)已采用全新的人工智能(AI)驅動的 Cadence Verisium 驗證

2023-03-15 09:07:00 539

539 在現代SoC芯片驗證過程中,不可避免的都會使用FPGA原型驗證,或許原型驗證一詞對你而言非常新鮮,但是FPGA上板驗證應該是非常熟悉的場景了。

2023-03-28 09:33:16 854

854 FPGA原型驗證系統要盡可能多的復用SoC相關的模塊,這樣才是復刻SoC原型的意義所在。

2023-04-19 09:08:15 852

852 FPGA原型驗證系統要盡可能多的復用SoC相關的模塊,這樣才是復刻SoC原型的意義所在。

2023-05-23 16:50:34 381

381

如果沒有經過深思熟慮的驗證環境,驗證團隊會浪費大量時間在 SoC 級別重新創建驗證環境以實現芯片級驗證,因為他們不考慮重用最初開發的環境來驗證其塊級 IP。即使跨相同的抽象級別,也無法重用相同的驗證IP和環境來支持仿真和仿真,也會導致延遲,并消耗不必要的工程資源。

2023-05-29 10:13:16 335

335

我們當然希望在項目中盡快準備好基于FPGA原型驗證的代碼,以便最大限度地為軟件團隊和RTL驗證人員帶來更客觀的收益。

2023-05-30 11:10:27 769

769

在現代SoC芯片驗證過程中,不可避免的都會使用FPGA原型驗證,或許原型驗證一詞對你而言非常新鮮,但是FPGA上板驗證應該是非常熟悉的場景了。

2023-05-30 15:04:06 905

905

思爾芯(S2C)近日宣布,公司的系統級驗證原型驗證解決方案獲得了較為全面的正向市場反饋,成功協助多家設計企業完成低功耗藍牙音頻(BLE Audio)領域的IP/藍牙SoC定制方案設計。

2023-05-30 15:52:52 402

402 了 Cadence 在面對 SoC 設計驗證挑戰下的應對之法。 隨著 SoC 設計的發展,如何在有限的時間內盡可能發現更多的 bug 和實現更多的溯源分析,讓項目各方面的投資都做到物盡其用,這是驗證工作所面臨

2023-06-07 00:20:03 466

466

隨著SOC/ASIC設計規模不斷增大,且結構愈加復雜,導致驗證的復雜度呈指數級增長。為了縮短芯片的上市周期,在不同設計階段工程師們往往選擇不同的仿真驗證工具,提高整個芯片開發效率。在一個芯片

2023-01-12 17:11:15 492

492

和混合信號 IP,與現有流程相比,在達到所需精度的同時,可幫助提升 2 倍性能。 Cadence 的這款解決方案助力 DB GlobalChip 加速了 IP 開發和驗證周期,可以更快將產品推向市場。 在客戶規定的時間內滿足模擬和混

2023-06-25 12:25:02 512

512 移動電話技術的進步不斷挑戰極限,要求SoC在提供不斷提升的性能的同時,還能保持較長的電池續航時間。為了滿足這些需求,業界正在逐步采用更低的技術節點,目前的設計都是在5納米或更低的工藝下完成的。在這

2023-07-17 10:12:18 433

433

很多其他行業也能從電子器件的增加受益,當然保障功能安全是大的前提。本文討論SOC芯片設計驗證、驗證計劃和策略以及驗證方法。它定義了功能模擬、功能覆蓋、代碼覆蓋以及設計驗證中使用的重要術語。本文還涉及FPGA驗證及其在S

2023-07-20 09:05:59 597

597 相信很多人已經接觸過驗證。如我以前有篇文章所寫驗證分為IP驗證,FPGA驗證,SOC驗證和CPU驗證,這其中大部分是采用動態仿真(dynamic simulation)實現,即通過給定設計(design)端口測試激勵,結合時間消耗判斷設計的輸出結果是否符合預期。

2023-07-21 09:53:24 4286

4286

電子設計自動化領域領先的供應商 Cadence,誠邀您參加 “ 2023 Cadence 中國技術巡回研討會”。會議將集聚 Cadence 的開發者與資深技術專家,與您分享系統驗證及 IC 驗證

2023-09-21 17:20:02 339

339

電子設計自動化領域領先的供應商 Cadence,誠邀您參加“2023 Cadence 中國技術巡回研討會”。會議將集聚 Cadence 的開發者與資深技術專家,與您分享系統驗證及 IC 驗證解決方案

2023-10-23 11:55:02 287

287

雙方的共同客戶可獲取 Cadence 的全流程系統級設計驗證和實現解決方案以及接口 IP,依托 Neoverse CSS 加速開發基于 Arm 的定制 SoC 中國上海,2023 年 10 月 25

2023-10-25 10:40:02 197

197

電子設計自動化領域領先的供應商 Cadence,誠邀您參加“2023 Cadence 中國技術巡回研討會”。會議將集聚 Cadence 的開發者與資深技術專家,與您分享系統驗證及 IC 驗證解決方案

2023-10-25 10:40:02 190

190

電子發燒友App

電子發燒友App

評論