電子發(fā)燒友網(wǎng)訊:在半導(dǎo)體行業(yè),大家最常見的口水戰(zhàn)除了英特爾和AMD,演進(jìn)到現(xiàn)在的英特爾和ARM,就當(dāng)數(shù)PLD領(lǐng)域的兩大霸主Xilinx和Altera。在近十幾年里,二者的爭霸戰(zhàn)就不曾停歇,行

2012-09-26 11:48:03 60805

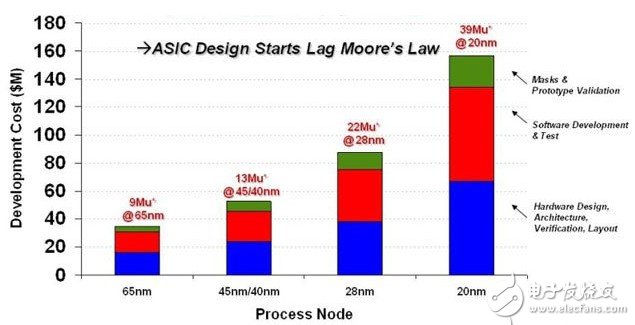

60805 不久前,據(jù)國外媒體報(bào)道,華為公司正在首次使用ASIC來替代其設(shè)備中的FPGA芯片,而這些芯片原本采購于FPGA主要廠商之一的Altera【 電子發(fā)燒友網(wǎng)關(guān)于此事報(bào)道:華為ASIC設(shè)計(jì)案,FPGA雙雄

2012-11-14 08:47:56 1970

1970 FPGA雙雄——Xilinx及Altera先后公布了公司最新季度報(bào)告。盡管FPGA雙雄都出現(xiàn)了利潤下滑的現(xiàn)象,但對(duì)于未來信心滿滿。本文從Xilinx及Altera近五個(gè)季度以來的銷售額與凈利潤的增長率進(jìn)行對(duì)比分析。

2013-01-25 14:00:24 1810

1810 物聯(lián)網(wǎng)著眼于芯片整合及訴求超低功耗,晶圓雙雄臺(tái)積電和聯(lián)電均建立相關(guān)制程平臺(tái),協(xié)助芯片廠搶商機(jī);聯(lián)發(fā)科也成立Linkit開發(fā)平臺(tái),以整合戰(zhàn)方式卡位。

2016-05-30 11:26:37 665

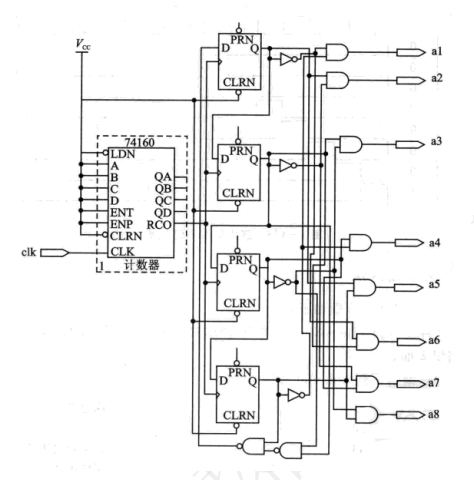

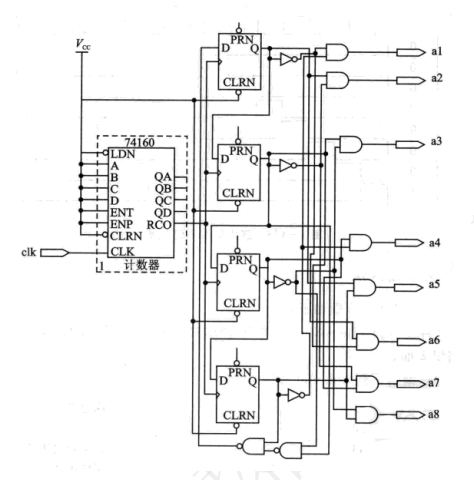

665 流水廣告燈主要應(yīng)用于LED燈光控制。通過程序控制LED的亮和滅, 多個(gè)LED燈組成一個(gè)陣列,依次逐個(gè)點(diǎn)亮的時(shí)候像流水一樣,所以叫流水燈。由于其形成美觀大方的視覺效果,因此廣泛應(yīng)用于店鋪招牌、廣告、大型建筑夜間裝飾、景觀裝飾等

2017-08-09 15:14:21 16567

16567

完成項(xiàng)目需求分析、電路圖分析以及方案設(shè)計(jì)后,接下來可以進(jìn)行FPGA設(shè)計(jì)了。如果用戶的計(jì)算機(jī)已安裝云源軟件GOWIN FPGA Designer,雙擊桌面上的程序圖標(biāo),即可打開GOWIN FPGA

2022-10-13 14:36:00 1107

1107 手頭的某個(gè)設(shè)計(jì)需要拿樹莓派4的ubuntu core啟動(dòng)時(shí)間做個(gè)對(duì)比。原來的SD卡壞了,只好重新安裝,記個(gè)流水賬。

2023-11-09 11:07:59 409

409

介紹一種基于 FPGA的音樂流水燈控制器, 采用硬件描述語言對(duì)其進(jìn)行描述, 分別實(shí)現(xiàn)樂曲的播放和同步流水燈的閃爍。并構(gòu)建一個(gè) SOPC系統(tǒng), 集成 LCD模塊來顯示實(shí)時(shí)音樂的音階值和頻率強(qiáng)度

2011-10-20 17:21:29 4128

4128 電子發(fā)燒友網(wǎng)訊【編譯/Triquinne 】: 在PLD行業(yè),大家耳熟能詳?shù)膽?zhàn)役要數(shù)Xilinx和Altera之間的瓜葛糾纏了【 具體可參考電子發(fā)燒友網(wǎng)原創(chuàng)文章: FPGA雙雄針鋒相對(duì),Xilinx與Altera霸主之爭

2012-10-15 16:13:29 3523

3523 在PLD應(yīng)用領(lǐng)域,真正值得稱道的FPGA后起之秀并不多,但作為FPGA新秀的Achronix公司近期以凌厲的市場攻勢,吸引了眾多科技專業(yè)媒體的關(guān)注。可以說,FPGA市場又加入了一員具備競爭力的悍將

2013-03-05 11:10:55 2448

2448 “ASIC將會(huì)被大幅削減!”當(dāng)身處前沿陣地的通信系統(tǒng)供應(yīng)商剛得到該消息,FPGA廠商已然制定策略,紛紛囤積庫存,瞄準(zhǔn)通信系統(tǒng)核市場商機(jī)。

2013-03-12 15:52:41 3186

3186 月份之前的霸主戰(zhàn)爭奪賽詳情請(qǐng)關(guān)注【霸主戰(zhàn)策略變,細(xì)數(shù)FPGA雙雄流水賬】 5月之后的戰(zhàn)況,電子發(fā)燒友網(wǎng)小編為您一一播報(bào),或許你也能從中看出些許端倪。 1. 工藝制程之戰(zhàn):從28nm轉(zhuǎn)戰(zhàn)更低先進(jìn)

2013-08-22 14:46:48

FPGA初級(jí)實(shí)驗(yàn) verilog let's start (流水燈實(shí)驗(yàn))module countpro(sys_clk,rst_n,led); //接口定義input sys_clk,rst_n

2012-02-08 16:28:30

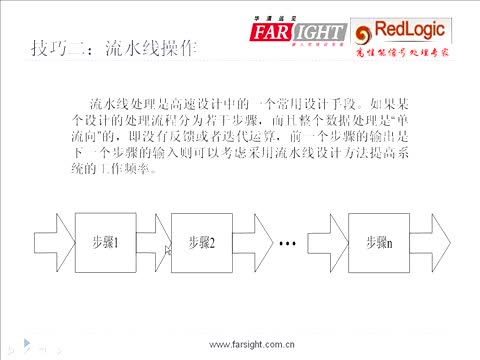

`流水線設(shè)計(jì)前言:本文從四部分對(duì)流水線設(shè)計(jì)進(jìn)行分析,具體如下:第一部分什么是流水線第二部分什么時(shí)候用流水線設(shè)計(jì)第三部分使用流水線的優(yōu)缺點(diǎn)第四部分流水線加法器舉例第一 什么是流水線流水線設(shè)計(jì)就是將組合

2020-10-26 14:38:12

` 隨著可編程邏輯器件應(yīng)用的日益廣泛,許多IC制造廠家涉足PLD/FPGA領(lǐng)域。目前世界上有十幾家生產(chǎn)CPLD/FPGA的公司,最大的三家是:ALTERA,XILINX,Lattice,其中

2012-02-09 14:21:32

摘要:FPGA異步時(shí)鐘設(shè)計(jì)中如何避免亞穩(wěn)態(tài)的產(chǎn)生是一個(gè)必須考慮的問題。本文介紹了FPGA異步時(shí)鐘設(shè)計(jì)中容易產(chǎn)生的亞穩(wěn)態(tài)現(xiàn)象及其可能造成的危害,同時(shí)根據(jù)實(shí)踐經(jīng)驗(yàn)給出了解決這些問題的幾種同步策略。關(guān)鍵詞

2009-04-21 16:52:37

看是如何實(shí)現(xiàn)的吧。一、 知識(shí)點(diǎn)集中化。(實(shí)例實(shí)證28原則)二、 填空式的設(shè)計(jì)過程。通常,我們通過敲代碼實(shí)現(xiàn)程序功能類似于記流水賬,一行一行一頁一頁的向下寫。在這個(gè)過程中,難免遇到設(shè)計(jì)無思路、代碼冗長重復(fù)

2017-12-15 15:10:57

EDA技術(shù)具有什么特征?FPGA是什么原理?FPGA設(shè)計(jì)應(yīng)用及優(yōu)化策略基于VHDL的FPGA系統(tǒng)行為級(jí)設(shè)計(jì)

2021-04-15 06:33:58

本系列將帶來FPGA的系統(tǒng)性學(xué)習(xí),從最基本的數(shù)字電路基礎(chǔ)開始,最詳細(xì)操作步驟,最直白的言語描述,手把手的“傻瓜式”講解,讓電子、信息、通信類專業(yè)學(xué)生、初入職場小白及打算進(jìn)階提升的職業(yè)開發(fā)者都可以有

2023-03-07 16:39:52

Altium-正規(guī)實(shí)戰(zhàn)教程(珍藏版)看了太多太多的EDA書籍,幾乎都是蜻蜓點(diǎn)水、流水賬式的介紹軟件操作界面說明,深入一點(diǎn)也僅是描述某某功能可以做什么以及怎么操作而已;共同點(diǎn)就是讀者看完整本書,本來會(huì)

2015-07-09 10:20:47

人工智能大熱之前,Cloud或Data Center已經(jīng)開始使用FPGA做各種加速了。而隨著Deep Learning的爆發(fā),這種需求越來越強(qiáng)勁。本文主要討論Cloud巨頭Amazon和Microsoft的FPGA策略。

2019-08-13 08:37:24

。又到工程目錄下去搜索涉及的頭文件,才發(fā)現(xiàn)有兩個(gè)名稱相同的頭文件init.h,原來后面添加的代碼有與之前重名的文件,導(dǎo)致編譯器在編譯時(shí)尋找頭文件時(shí),因?yàn)橛袃蓚€(gè)相同名稱的頭文件,使得編譯出錯(cuò)。后面修改就簡單了,把其中一個(gè)頭文件名稱修改掉,不重名就可以編譯通過啦。第一次寫博客,有點(diǎn)記流水賬的感覺,后面

2021-11-30 06:58:26

第一個(gè)問題,究竟要玩哪一個(gè)芯?今年真是變幻莫測的一年,芯片的真是流水賬的價(jià)格,一天一個(gè)樣,翻翻自己的抽屜,一堆的板卡,不知玩弄哪一個(gè),一直想玩弄一下新塘的片子,可惜論壇沒怎么做過新塘的開發(fā)板評(píng)測活動(dòng)

2021-07-21 08:49:01

U-BOOT移植過程流水賬1,修改MAKEFILE增加開發(fā)板編譯定義at91sam9260ek_config : unconfig @./mkconfig $(@:_config=) arm

2011-11-29 14:21:42

`Xilinx FPGA入門連載19:流水燈實(shí)例特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能簡介如圖所示,在SF-SP6

2015-10-31 12:15:44

`Xilinx FPGA入門連載22:經(jīng)典模式流水燈實(shí)驗(yàn)特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能簡介本實(shí)例使用一個(gè)撥碼

2015-11-06 13:48:22

利用 FPGA 實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA 具有以多個(gè)時(shí)鐘運(yùn)行的多重?cái)?shù)據(jù)通路,這種多時(shí)鐘 FPGA 設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率、抖動(dòng)、最大時(shí)鐘數(shù)、異步時(shí)鐘設(shè)計(jì)和時(shí)鐘/數(shù)據(jù)關(guān)系

2012-03-05 14:42:09

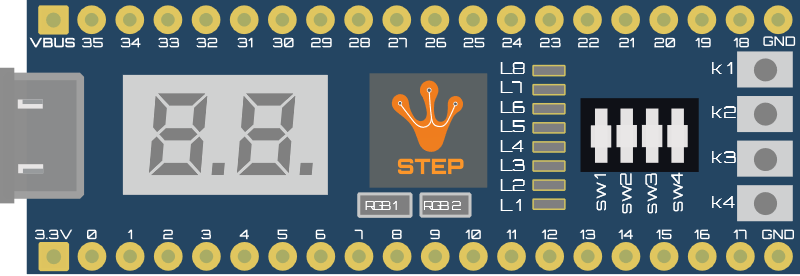

項(xiàng)目名稱:流水燈。具體要求:復(fù)位時(shí),所有燈全滅。打開開關(guān)SW1時(shí),所有燈做流水動(dòng)作。系統(tǒng)設(shè)計(jì):硬件介紹:開發(fā)板上有9個(gè)LED,包含 1 路 FPGA_DONE 信號(hào)指示燈,1 路3.3V 電源指示燈

2021-07-30 11:04:26

` 本帖最后由 suyong_yq 于 2015-8-20 00:20 編輯

【在PC上安裝Linux虛擬機(jī)】【在PC和虛擬Linux主機(jī)之間建立數(shù)據(jù)通道并上傳交叉編譯器】【登錄開發(fā)板并配置網(wǎng)絡(luò)連接】【通過 NFS 建立虛擬Linux主機(jī)同開發(fā)板之間的數(shù)據(jù)通信】【編寫并運(yùn)行第一個(gè)程序HelloWorld】------------------------------------------------------------------------------------【在PC上安裝Linux虛擬機(jī)】1. VirtualBox2. Ubuntu 12.04 LTS3. 配置虛擬Linux網(wǎng)絡(luò)類型為NAT,在系統(tǒng)內(nèi)設(shè)定固定IP為192.168.2.105【在PC和虛擬Linux主機(jī)之間建立數(shù)據(jù)通道并上傳交叉編譯器】使用sftp實(shí)現(xiàn)網(wǎng)絡(luò)文件共享1. 首先在虛擬Linux主機(jī)上安裝ssh server[tr=inherit]sudo apt-get install ssh[/tr]2. 在PC上安裝SFTP要去下載一個(gè) winSCP,項(xiàng)目主頁鏈接:http://winscp.net/eng/index.phpFigure_01在PC上通過WinSCP登錄虛擬Linux主機(jī)。Figure_023. 上傳交叉編譯器在虛擬Linux的/home/andrew/下創(chuàng)建目錄“fsl_imx283”作為開發(fā)根目錄,專門用于存放imx283開發(fā)資料及代碼。Figure_034. 解壓壓縮包在虛擬Linux主機(jī)上切換當(dāng)前目錄至開發(fā)根目錄。解壓剛剛從PC上傳過來的壓縮包。[tr=inherit]tar xvf gcc-4.4.4-glibc-2.11.1-multilib-1.0_EasyARM-iMX283.tar.bz2[/tr]壓縮包里的文件不少,所以要稍微等一下。解壓之后可以看到解壓出來的“gcc-4.4.4-glibc-2.11.1-multilib-1.0”文件夾下只有一個(gè)“arm-fsl-linux-gnueabi”目錄,把這個(gè)目錄提出來到開發(fā)根目錄下。[tr=inherit]mv -f gcc-4.4.4-glibc-2.11.1-multilib-1.0/arm-fsl-linux-gnueabi/ .rm -rf gcc-4.4.4-glibc-2.11.1-multilib-1.0[/tr]5. 接下來把這個(gè)工具鏈添加到環(huán)境變量.在當(dāng)前用戶(andrew)下,編輯 .bashrc 文件[tr=inherit]nano ~/.bashrc[/tr]在文件的最最后一行添加:[tr=inherit]export PATH=$PATH:/home/andrew/fsl_imx283/arm-fsl-linux-guneabi/bin[/tr]使用以下命令,使新的環(huán)境變量 立即生效[tr=inherit]source ~/.bashrc [/tr]打印環(huán)境變量,看看新添加的變量是否生效了[tr=inherit]echo $PATH[/tr]Figure_04查看 arm-fsl-linux-gnueabi-gcc 的版本. 如有有輸出即表示安裝成功.[tr=inherit]arm-fsl-linux-gnueabi-gcc -v[/tr]Figure_05【登錄開發(fā)板并配置網(wǎng)絡(luò)連接】1. 在PC機(jī)通過串口終端登錄開發(fā)板使用一個(gè)USB轉(zhuǎn)TTL串口的小電路板將PC同開發(fā)板的串口連接起來。 串口波特率:115200 登錄用戶名:root 登錄密碼:root登錄成功!Figure_062. 設(shè)置固定IP在"/etc/rc.d/init.d/start_userapp"文件中添加配置靜態(tài)IP語句[tr=inherit]ifconfig eth0 192.168.12.120[/tr]3. 嘗試使用ssh通信登錄開發(fā)板1) 在PC上使用ssh通信登錄a. 在Tera Term的終端創(chuàng)建新的連接:Figure_07b. 首次登錄需要添加“指紋”:Figure_08c. 在對(duì)話框中輸入登錄用戶名和密碼:Figure_09登錄成功:Figure_102) 在Linux主機(jī)登錄開發(fā)板系統(tǒng)在Terminal中使用ssh命令登錄:[tr=inherit]ssh root@192.168.2.120[/tr]然后就是輸入密碼“root”。登錄成功:Figure_11【通過 NFS 建立虛擬Linux主機(jī)同開發(fā)板之間的數(shù)據(jù)通信】1. 在虛擬機(jī)Linux中安裝nfs-kernel-server[tr=inherit]sudo apt-get install nfs-kernel-server[/tr]2. 編輯配置文件,指定共享目錄。這里共享整個(gè)“/home”,以后再增加新用戶就不需要再配置NFS服務(wù)了。[tr=inherit]sudo nano /etc/exports[/tr]Figure_123. 重啟服務(wù),使新配置生效[tr=inherit]sudo /etc/init.d/nfs-kernel-server restart[/tr]4. 在開發(fā)板上掛載 NFS這里在虛擬Linux主機(jī)登錄開發(fā)板的ssh終端中操作開發(fā)板[tr=inherit]mount 192.168.2.105:/home /mnt -o nolock[/tr]Figure_13進(jìn)入開發(fā)板的/mnt 目錄, 發(fā)現(xiàn)Linux主機(jī)中的 /home 目錄的所有文件都掛載到開發(fā)板上了Figure_14【編寫并運(yùn)行第一個(gè)程序HelloWorld】1. 在Linux主機(jī)上創(chuàng)建源文件“HelloWorld.c”在開發(fā)根目錄下創(chuàng)建“code”子目錄,并在其中創(chuàng)建“HelloWorld.c”源代碼文件。[tr=inherit]mkdir codenano HelloWorld.c[/tr]Figure_152. 然后在Linux主機(jī)上使用交叉編譯器編譯源文件[tr=inherit]arm-fsl-linux-gnueabi-gcc HelloWorld.c -o HelloWorld[/tr]編譯成功,產(chǎn)生 HelloWorld文件Figure_163. 在開發(fā)板上運(yùn)行HelloWorld切回到登錄開發(fā)板的終端,由于建立了NFS映射,在開發(fā)板的文件系統(tǒng)中也能看到生成的HelloWorld可執(zhí)行文件。運(yùn)行HelloWorld[tr=inherit]./HelloWorld[/tr]Figure_17至此,編程環(huán)境搞定,準(zhǔn)備下一步應(yīng)用程序的開發(fā)。網(wǎng)頁排版系統(tǒng)還是搞得不太理想。若是想要更好的閱讀體驗(yàn),可以戳進(jìn)我的筆記分享頁面,http://note.youdao.com/share/?id=d82b738bbf6dc30636075d8eaaa903c8&type=note`

2015-08-20 00:15:17

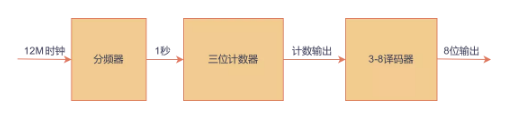

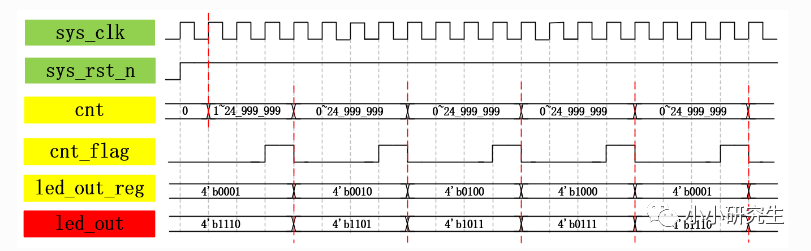

本視頻是Runber FPGA開發(fā)板的配套視頻課程,主要通過LED流水燈實(shí)驗(yàn)來介紹如何利用計(jì)數(shù)器按一定的時(shí)鐘頻率進(jìn)行計(jì)時(shí)和數(shù)據(jù)位拼接操作,實(shí)現(xiàn)LED流水燈每0.5秒狀態(tài)跳轉(zhuǎn)一次,幫助用戶快速掌握

2021-04-12 18:28:35

本帖最后由 china_he 于 2017-1-5 16:32 編輯

今天給板子上電,首先看了一下“TMS320C6678開發(fā)板開箱即用”這篇文檔,依然是創(chuàng)龍的“流水賬”風(fēng)格。首先試了一下

2016-12-26 19:57:40

本帖最后由 拾光333 于 2020-1-11 12:14 編輯

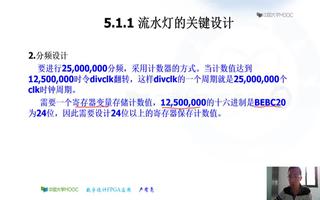

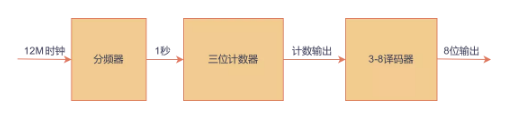

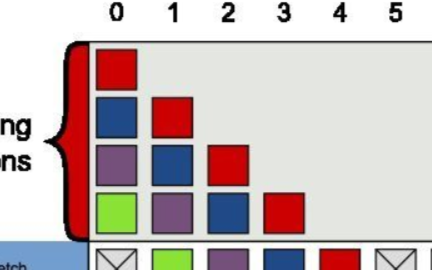

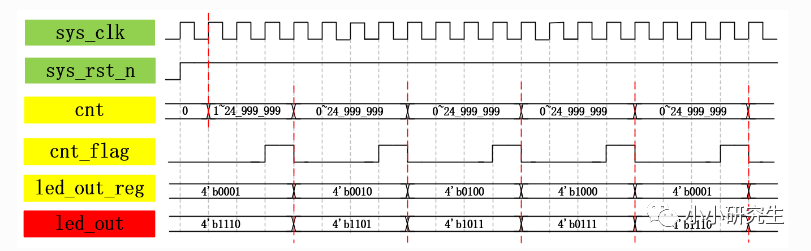

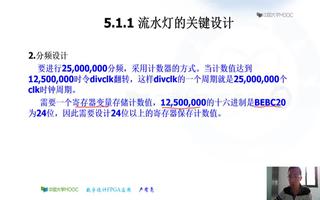

設(shè)計(jì)內(nèi)容 將4個(gè)LED每隔1s從左往右分別依次點(diǎn)亮熄滅,形成流水狀。按復(fù)位鍵時(shí)進(jìn)行復(fù)位,重新開始流水。流程 FPGA的時(shí)鐘頻率

2020-01-11 11:07:59

如何理解fpga流水線

2015-08-15 11:43:23

前段時(shí)間發(fā)了個(gè)關(guān)于fpga的PID實(shí)現(xiàn)的帖子,有個(gè)人說“整個(gè)算法過程說直白點(diǎn)就是公式的硬件實(shí)現(xiàn),用到了altera提供的IP核,整個(gè)的設(shè)計(jì)要注意的時(shí)鐘的選取,流水線的應(yīng)用”,本人水平有限,想請(qǐng)教一下其中時(shí)鐘的選取和流水線的設(shè)計(jì)應(yīng)該怎么去做,需要注意些什么,請(qǐng)大家指導(dǎo)一下。

2015-01-11 10:56:59

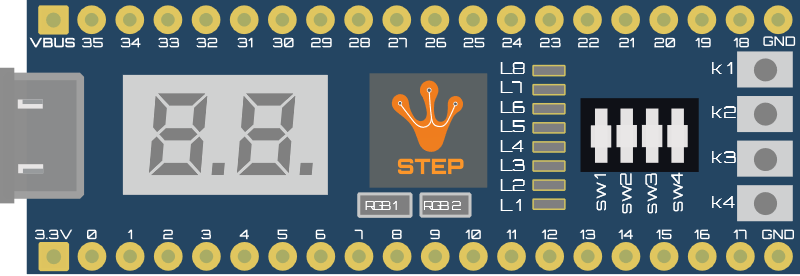

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載21:蜂鳴器、數(shù)碼管、流水燈、撥碼開關(guān)電路特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD

2017-11-17 19:12:26

各位大俠,有用FPGA做過旋變解碼芯片算法的嗎?

2014-03-22 08:23:16

【流水燈樣例】基于 FPGA Vivado 的數(shù)字鐘設(shè)計(jì)前言模擬前言Vivado 設(shè)計(jì)流程指導(dǎo)手冊(cè)——2013.4密碼:5txi模擬

2022-02-07 08:02:04

以降低系統(tǒng)速度為代價(jià)。從FPGA發(fā)展趨勢和DSP運(yùn)算要求看,系統(tǒng)速度指標(biāo)的意義比面積指標(biāo)更趨重要,需要我們進(jìn)一步深入研究提高芯片的最高工作速度的設(shè)計(jì)策略。我們需要討論一下基于FPGA的DSP系統(tǒng)設(shè)計(jì)中的流水線技術(shù)主要應(yīng)用在哪些方面?

2019-08-02 06:03:48

基于FPGA的三相電流型PWM整流器過調(diào)制策略的研究

2017-09-30 09:17:14

基于FPGA的移位寄存器流水線結(jié)構(gòu)FFT處理器

2012-08-18 00:04:21

本帖最后由 eehome 于 2013-1-5 10:02 編輯

基于FPGA的音樂流水燈控制系統(tǒng)設(shè)計(jì)

2012-08-19 23:22:53

為了緩解能源問題,在完全兼容現(xiàn)有供電系統(tǒng)的基礎(chǔ)上,該系統(tǒng)采用風(fēng)能和太陽能對(duì)電能進(jìn)行補(bǔ)給的方法,并且附帶快速檢測孤島效應(yīng),快速并網(wǎng)和斷網(wǎng)的功能。系統(tǒng)的功率電路部分采用全橋拓?fù)溥M(jìn)行逆變,數(shù)字控制系統(tǒng)采用

2019-09-24 06:43:06

LED流水廣告燈工程說明在本案例中,使用常用的verilog語言完成該程序,設(shè)計(jì)并控制8個(gè)燈的花式或循環(huán)點(diǎn)亮;即上電后,實(shí)現(xiàn)左移和右移交替的流水燈。案例補(bǔ)充說明在FPGA電路設(shè)計(jì)中,盡管流水

2017-08-02 17:56:09

工作記錄流水賬1.機(jī)器人電機(jī)驅(qū)動(dòng)器安裝接線。2.CML2.00開發(fā)包繼續(xù)研究:電機(jī)驅(qū)動(dòng)器底層API。3.基于電機(jī)驅(qū)動(dòng)CML-2.00程序編寫(控制臺(tái))實(shí)現(xiàn)功能:多驅(qū)動(dòng)器串聯(lián)同時(shí)控制速度角度控制連續(xù)運(yùn)行4.MFC界面實(shí)現(xiàn)功能:多驅(qū)動(dòng)器串聯(lián)同時(shí)控制速度角度控制連續(xù)運(yùn)行第一版:運(yùn)動(dòng)控制系統(tǒng)...

2021-09-13 06:27:55

本帖最后由 mingzhezhang 于 2012-5-23 20:05 編輯

大型設(shè)計(jì)中FPGA的多時(shí)鐘設(shè)計(jì)策略 利用FPGA實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA具有以多個(gè)時(shí)鐘運(yùn)行的多重

2012-05-23 19:59:34

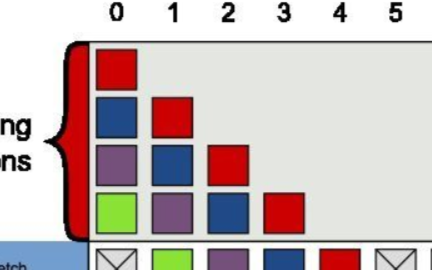

配置選擇上篇【FPGA實(shí)驗(yàn)】流水燈實(shí)驗(yàn)記錄了如何上手FPGA,實(shí)現(xiàn)簡單的流水燈效果,本篇將稍微升級(jí)一些,通過按鈕實(shí)現(xiàn)多種形態(tài)的流水燈。此次仍使用正點(diǎn)原子的開拓者FPGA開發(fā)板,配置和上篇一致。功能

2022-01-18 10:28:27

微信綁定積分沒有到賬啊,有獲得記錄

2017-01-11 14:40:27

` 本帖最后由 邁拓維矩 于 2018-4-10 17:10 編輯

未來機(jī)房霸主,工程商,采購商必備。【 一人輕松上機(jī)架,無需工具來鎖緊,全程僅需一雙手,不到十秒能搞定。】邁拓維矩新款可拆卸式MT-1708UL已開始火熱預(yù)售。歡迎致電邁拓維矩了解相關(guān)詳情!!!邁拓維矩新款MT-1708UL`

2018-04-10 17:08:15

請(qǐng)問一下高速流水線浮點(diǎn)加法器的FPGA怎么實(shí)現(xiàn)?

2021-05-07 06:44:26

與測量和高性能計(jì)算領(lǐng)域的存在及其競爭力,強(qiáng)力威脅著FPGA雙雄--Xilinx和Altera在該領(lǐng)域的龍頭地位。Achronix公司總裁兼首席執(zhí)行官Robert Blake 未來的嵌入式系統(tǒng)將需要

2013-05-07 15:05:03

永磁交流伺服電機(jī)模型是強(qiáng)耦合,時(shí)變的非線性系統(tǒng)。優(yōu)良的控制策略不但可以彌補(bǔ)硬件設(shè)計(jì)方面的不足,通過控制策略可以進(jìn)一步提高系統(tǒng)的性能,不但使系統(tǒng)具有快速的動(dòng)態(tài)響應(yīng)和高的動(dòng)、靜態(tài)精度,而且系統(tǒng)要對(duì)參數(shù)

2021-06-28 06:44:48

FPGA重要設(shè)計(jì)思想及工程應(yīng)用之流水線設(shè)

流水線設(shè)計(jì)是高速電路設(shè)計(jì)中的一 個(gè)常用設(shè)計(jì)手段。如果某個(gè)設(shè)計(jì)的處理流程分為若干步驟,而且整個(gè)數(shù)據(jù)處理 流程分

2010-02-09 11:02:20 52

52 大型設(shè)計(jì)中FPGA的多時(shí)鐘設(shè)計(jì)策略

利用FPGA實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA具有以多個(gè)時(shí)鐘運(yùn)行的多重?cái)?shù)據(jù)通路,這種多時(shí)鐘FPGA設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率

2009-12-27 13:28:04 645

645

形勢大好 晶圓雙雄訂單大增

晶圓代工廠2010年第1季業(yè)績可望超乎預(yù)期,原本業(yè)界預(yù)計(jì)晶圓雙雄臺(tái)積電、聯(lián)電第1季業(yè)績將出現(xiàn)些微衰退,但近期因

2010-01-20 10:19:44 494

494 高速流水線浮點(diǎn)加法器的FPGA實(shí)現(xiàn)

0 引言現(xiàn)代信號(hào)處理技術(shù)通常都需要進(jìn)行大量高速浮點(diǎn)運(yùn)算。由于浮點(diǎn)數(shù)系統(tǒng)操作比較復(fù)雜,需要專用硬件來完成相關(guān)的操

2010-02-04 10:50:23 2042

2042

FPGA芯片選擇策略和原則

由于FPGA具備設(shè)計(jì)靈活、可以重復(fù)編程的優(yōu)點(diǎn),因此在電子產(chǎn)品設(shè)計(jì)領(lǐng)域得到了越來越廣泛的應(yīng)用。在工程項(xiàng)目或者產(chǎn)品設(shè)計(jì)

2010-02-09 09:13:29 3080

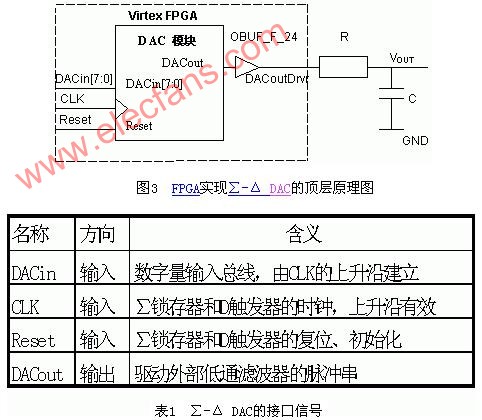

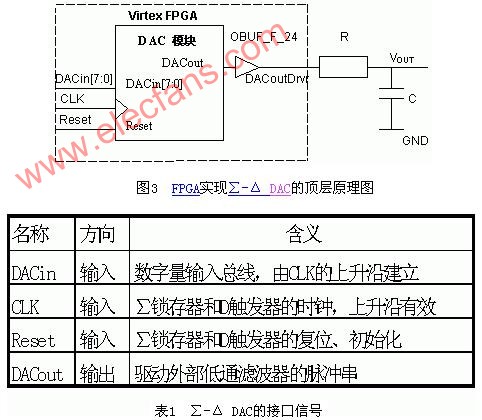

3080 根據(jù)FPGA的∑-Δ D/A轉(zhuǎn)換器的設(shè)計(jì)與實(shí)現(xiàn)策略摘要:數(shù)模轉(zhuǎn)換器可以將一個(gè)二進(jìn)制數(shù)字量轉(zhuǎn)換成與該數(shù)字量成正比的電壓值,可應(yīng)用于可

2010-04-21 15:45:51 1251

1251

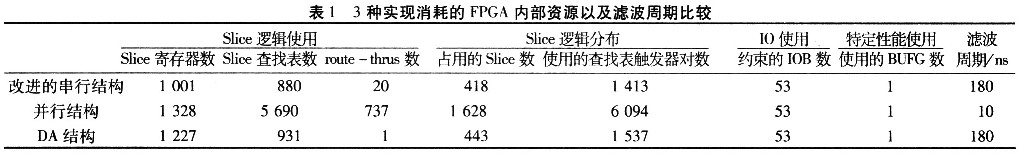

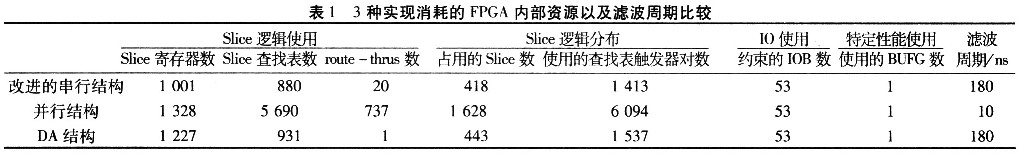

FIR數(shù)字濾波器的FPGA實(shí)現(xiàn)研究策略 如今,FPGA已成為數(shù)字信號(hào)處理系統(tǒng)的核心器件,尤其在數(shù)字通信、網(wǎng)絡(luò)、視頻和圖像處理等領(lǐng)域。現(xiàn)在的FPGA不僅包含查找表、寄存

2010-04-23 14:13:22 1077

1077

晶圓雙雄2010年資本支出大手筆擴(kuò)增

2010年一開春臺(tái)積電、聯(lián)電法說成外界關(guān)注焦點(diǎn),晶圓雙雄對(duì)于2010年景氣的論調(diào)與資

2010-01-11 09:36:51 746

746 為了提高快速傅里葉變換( FFT)處理數(shù)據(jù)的實(shí)時(shí)性,本文利用現(xiàn)場可編程陣列( FPGA)邏輯資源豐富、運(yùn)算速度快的特點(diǎn)以及FFT算法的分級(jí)特性,實(shí)現(xiàn)了高速、高階FFT的流水線工作方式設(shè)計(jì)。通

2011-10-01 01:52:51 55

55 為了提高快速傅里葉變換( FFT)處理數(shù)據(jù)的實(shí)時(shí)性,本文利用現(xiàn)場可編程陣列( FPGA)邏輯資源豐富、運(yùn)算速度快的特點(diǎn)以及FFT算法的分級(jí)特性,實(shí)現(xiàn)了高速、高階FFT的流水線工作方式設(shè)計(jì)。通

2011-10-28 17:11:26 32

32 FPGA具有產(chǎn)品設(shè)計(jì)者可以自行修改其內(nèi)部邏輯的優(yōu)點(diǎn)。作為開發(fā)費(fèi)用持續(xù)上漲的ASIC和ASSP的替代品,越來越多的電子產(chǎn)品開始配備FPGA。FPGA競爭力的源泉來自于半導(dǎo)體制造技術(shù)的微細(xì)化。

2012-03-31 09:55:49 3539

3539 電子發(fā)燒友網(wǎng)訊 :臺(tái)積電28nm良率大幅提升的利好還沒被市場徹底消化, FPGA業(yè)界雙雄 已爭先恐后地發(fā)布20nm FPGA戰(zhàn)略,在性能、功耗、集成度等方面均大幅躍升,蠶食ASIC之勢將愈演愈烈

2012-11-30 11:51:23 1865

1865 這篇博客不談技術(shù),就講講一個(gè)普通的Xilinx開發(fā)者的故事。當(dāng)年寫作文的水平就很差,流水賬一篇,不喜請(qǐng)噴:-D 今年距離世界上第一片FPGA:XC2064的產(chǎn)生,已經(jīng)整整過去了三十年,距離我接觸

2017-02-09 08:26:07 263

263

流水線是一種可用于增強(qiáng)FPGA VI吞吐量的技術(shù)。在流水線設(shè)計(jì)中,用戶可利用FPGA的并行處理功能提高順序代碼的有效性。如要實(shí)現(xiàn)流水線,必須將代碼拆分為不同的級(jí)并連線每級(jí)的輸入和輸出端至循環(huán)中的反饋

2017-11-18 06:02:01 3248

3248

asean的 FPGA DIY 流水燈視頻

2018-06-20 05:04:00 2725

2725

FPGA diy作業(yè)實(shí)現(xiàn)8位LED輸出向左的流水燈。

2018-06-20 08:26:00 4998

4998

基于FPGA的數(shù)字系統(tǒng)設(shè)計(jì)中大都推薦采用同步時(shí)序的設(shè)計(jì),也就是單時(shí)鐘系統(tǒng)。但是實(shí)際的工程中,純粹單時(shí)鐘系統(tǒng)設(shè)計(jì)的情況很少,特別是設(shè)計(jì)模塊與外圍芯片的通信中,跨時(shí)鐘域的情況經(jīng)常不可避免。如果對(duì)跨時(shí)鐘

2018-09-01 08:29:21 5302

5302

FPGA設(shè)計(jì)中,層次結(jié)構(gòu)設(shè)計(jì)和復(fù)位策略影響著FPGA的時(shí)序。在高速設(shè)計(jì)時(shí),合理的層次結(jié)構(gòu)設(shè)計(jì)與正確的復(fù)位策略可以優(yōu)化時(shí)序,提高運(yùn)行頻率。

2019-02-15 15:15:53 849

849 本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA開發(fā)板進(jìn)行奇偶流水燈的詳細(xì)資料說明。

2019-04-28 08:00:00 3

3 流水線的平面設(shè)計(jì)應(yīng)當(dāng)保證零件的運(yùn)輸路線最短,生產(chǎn)工人操作方便,輔助服務(wù)部門工作便利,最有效地利用生產(chǎn)面積,并考慮流水線安裝之間的相互銜接。為滿足這些要求,在流水線平面布置時(shí)應(yīng)考慮流水線的形式、流水線安裝工作地的排列方法等問題。

2019-11-28 07:07:00 2039

2039 流水線又稱為裝配線,一種工業(yè)上的生產(chǎn)方式,指每一個(gè)生產(chǎn)單位只專注處理某一個(gè)片段的工作。以提高工作效率及產(chǎn)量;按照流水線的輸送方式大體可以分為:皮帶流水裝配線、板鏈線、倍速鏈、插件線、網(wǎng)帶線、懸掛線及滾筒流水線這七類流水線。

2019-11-28 07:04:00 3232

3232 LED流水燈這篇采用最簡單的就是點(diǎn)亮一個(gè)燈延時(shí)一定時(shí)間,然后關(guān)閉,接下去點(diǎn)亮下一個(gè)燈,依次類推形成流水燈的效果

2019-12-04 07:09:00 3326

3326

本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA實(shí)現(xiàn)流水燈的詳細(xì)資料說明。流水燈模塊對(duì)于發(fā)展商而言,動(dòng)土儀式無疑是最重要的任務(wù)。為此,流水燈實(shí)驗(yàn)作為低級(jí)建模II的動(dòng)土儀式再適合不過了。廢話少說,我們還是開始實(shí)驗(yàn)吧。

2019-07-11 16:45:09 27

27 本人有過多年用FPGA做圖像處理的經(jīng)驗(yàn),在此也談一下自己的看法。用FPGA做圖像處理最關(guān)鍵的一點(diǎn)優(yōu)勢就是:FPGA能進(jìn)行實(shí)時(shí)流水線運(yùn)算,能達(dá)到最高的實(shí)時(shí)性。因此在一些對(duì)實(shí)時(shí)性要求非常高的應(yīng)用領(lǐng)域

2019-07-19 09:47:07 8080

8080 本文檔的主要內(nèi)容詳細(xì)介紹的是使用XIlinx的FPGA芯片開發(fā)的流水燈實(shí)驗(yàn)工程文件免費(fèi)下載,可為初學(xué)者展示FPGA工作的基本過程。

2019-07-31 08:00:00 4

4 利用 FPGA 實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA 具有以多個(gè)時(shí)鐘運(yùn)行的多重?cái)?shù)據(jù)通路,這種多時(shí)鐘FPGA 設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率、抖動(dòng)、最大時(shí)鐘數(shù)、異步時(shí)鐘設(shè)計(jì)和時(shí)鐘/數(shù)據(jù)關(guān)系。設(shè)計(jì)過程中最重要的一步是確定要用多少個(gè)不同的時(shí)鐘,以及如何進(jìn)行布線,本文將對(duì)這些設(shè)計(jì)策略深入闡述。

2021-01-13 17:00:00 11

11 利用 FPGA 實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA 具有以多個(gè)時(shí)鐘運(yùn)行的多重?cái)?shù)據(jù)通路,這種多時(shí)鐘FPGA 設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率、抖動(dòng)、最大時(shí)鐘數(shù)、異步時(shí)鐘設(shè)計(jì)和時(shí)鐘/數(shù)據(jù)關(guān)系。設(shè)計(jì)過程中最重要的一步是確定要用多少個(gè)不同的時(shí)鐘,以及如何進(jìn)行布線,本文將對(duì)這些設(shè)計(jì)策略深入闡述。

2021-01-15 15:57:00 14

14 本文檔的主要內(nèi)容詳細(xì)介紹的是使用FPGA實(shí)現(xiàn)流水燈設(shè)計(jì)的資料合集免費(fèi)下載。

2021-01-18 08:00:00 30

30 流水燈,有時(shí)候也叫跑馬燈,是一個(gè)簡單、有趣又經(jīng)典的實(shí)驗(yàn),基本所有單片機(jī)的玩家們?cè)诔跗趯W(xué)習(xí)的階段都做過。本次我們也來介紹一下如何通過小腳丫FPGA實(shí)現(xiàn)一個(gè)流水燈。

2021-03-19 16:36:28 4066

4066 引言:FPGA作為數(shù)字電路三大基石之一,其選型的好壞決定了產(chǎn)品的成本、項(xiàng)目研發(fā)效率、產(chǎn)品上市時(shí)間、產(chǎn)品生命周期等諸多方面。FPGA選型策略可以分為FPGA廠商選擇、FPGA器件家族選擇、器件型號(hào)選擇

2021-03-22 09:25:18 6517

6517 提出了一種可以進(jìn)行列主元選取的細(xì)粒度LU分解流水線算法并在現(xiàn)場編程門陣列(FPGA)上得到了實(shí)現(xiàn)。該算法可以在進(jìn)行列主元選取的同時(shí),充分利用數(shù)據(jù)的重用性,以減少數(shù)據(jù)讀寫次數(shù)。對(duì)其中的關(guān)鍵運(yùn)算實(shí)現(xiàn)

2021-03-31 09:24:16 11

11 流水燈,有時(shí)候也叫跑馬燈,是一個(gè)簡單、有趣又經(jīng)典的實(shí)驗(yàn),基本所有單片機(jī)的玩家們?cè)诔跗趯W(xué)習(xí)的階段都做過。本次我們也來介紹一下如何通過小腳丫FPGA實(shí)現(xiàn)一個(gè)流水燈。

2021-06-06 10:42:28 7565

7565

【流水燈樣例】基于 FPGA Vivado 的數(shù)字鐘設(shè)計(jì)前言模擬前言Vivado 設(shè)計(jì)流程指導(dǎo)手冊(cè)——2013.4密碼:5txi模擬

2021-12-04 13:21:08 26

26 本文解釋了流水線及其對(duì) FPGA 的影響,即延遲、吞吐量、工作頻率的變化和資源利用率。

2022-05-07 16:51:10 4734

4734

熟悉 HME FPGA PLL IP 的使用,實(shí)現(xiàn) LED 流水燈功能。

2023-05-30 10:04:21 843

843

依次點(diǎn)亮4個(gè)LED燈,實(shí)現(xiàn)流水燈的效果,兩燈之間點(diǎn)亮間隔為0.5s,LED燈一次點(diǎn)亮持續(xù)時(shí)間0.5s。

2023-06-23 16:54:00 1169

1169

流水燈,有時(shí)候也叫跑馬燈,是一個(gè)簡單、有趣又經(jīng)典的實(shí)驗(yàn),基本所有單片機(jī)的玩家們?cè)诔跗趯W(xué)習(xí)的階段都做過。本次我們也來介紹一下如何通過小腳丫FPGA實(shí)現(xiàn)一個(gè)流水燈。

2023-06-20 17:10:18 866

866

電子發(fā)燒友網(wǎng)站提供《基于流水線CORDIC算法通用數(shù)字調(diào)制器的FPGA實(shí)現(xiàn)方案.pdf》資料免費(fèi)下載

2023-10-27 09:46:19 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論