電子發(fā)燒友網(wǎng)報(bào)道(文/黃山明)近日,有知情人士透露,蘋果公司將取消已經(jīng)持續(xù)十年之久的“泰坦計(jì)劃”,這也意味著蘋果或?qū)⒎艞壪蛟燔嚪较虬l(fā)力。造車項(xiàng)目組的許多員工將被轉(zhuǎn)移到該公司的機(jī)器學(xué)習(xí)和人工智能部門

2024-02-29 00:11:00 3485

3485 產(chǎn)自主可 海思Hi3093面向服務(wù)器、工控機(jī)的高性能MPU產(chǎn)品海思Hi3093是面向服務(wù)器、工控機(jī)市場推出的高性能MPU產(chǎn)品,包括 4xA55@1.0G

2024-03-19 14:53:42

“基于OpenHarmony的團(tuán)結(jié)引擎應(yīng)用開發(fā)賽”是開放原子全球開源大賽下開設(shè)的新興及應(yīng)用賽的賽題之一,本次賽題旨在鼓勵(lì)更多開發(fā)者基于OpenHarmony 4.x版本,使用Unity中國團(tuán)結(jié)引擎

2024-03-13 10:45:10

。

FPGA 方案和 ASIC 方案成本比較

4)技術(shù)趨勢(shì):制程迭代驅(qū)動(dòng) 33 年發(fā)展,平臺(tái)型產(chǎn)品是未來。

1985 年賽靈思發(fā)明 FPGA 以來,其容量提高了一萬倍以上,速度提高了一百

2024-03-08 14:57:22

我們用的主平臺(tái)是賽靈思,想要通過CYUSB3014+FPGA實(shí)現(xiàn)OTG的功能,有幾個(gè)問題,想請(qǐng)教一下。

1.是否有可以驗(yàn)證功能的EVK呢,我找了下FX3 DVK似乎買不到

2024-02-29 07:20:21

面向未來設(shè)計(jì)

鴻蒙系統(tǒng)移植和裁剪定制

……

《鴻蒙開發(fā)實(shí)戰(zhàn)》

ArkTS實(shí)踐

UIAbility應(yīng)用

網(wǎng)絡(luò)案例

……

2024-02-27 22:08:34

400GE IP承載網(wǎng)絡(luò)即可以滿足5G移動(dòng)承載,千兆家寬及敏捷企業(yè)專線業(yè)務(wù)承載,也可以面向未來5.5G移動(dòng)寬帶、萬兆家寬寬帶、企業(yè)專線、企業(yè)園區(qū)等4類萬兆聯(lián)接升級(jí),5-10年持續(xù)平滑演進(jìn),保護(hù)投資。

2024-02-21 15:40:57 98

98 芯片原子鐘賽思是一家為萬物互聯(lián)同頻的時(shí)頻科技企業(yè),基于業(yè)界的時(shí)頻科研與方案能力,賽思打造出軟硬一體化的時(shí)頻產(chǎn)品體系,面向電力、交通、通信、智能樓宇、數(shù)據(jù)中心、前沿領(lǐng)域等核心場景提供解決方案,持續(xù)為

2024-02-02 09:39:57

Cobalt Strike是一款基于java的滲透測試神器,常被業(yè)界人稱為CS神器。

2024-01-16 09:16:20 201

201

芯片電路圖方案

2024-01-12 18:19:16

高精度低功耗授時(shí)模塊衛(wèi)星板卡,賽思是一家為萬物互聯(lián)同頻的時(shí)頻科技企業(yè),基于業(yè)界的時(shí)頻科研與方案能力,賽思打造出軟硬一體化的時(shí)頻產(chǎn)品體系,面向電力、交通、通信、智能樓宇、數(shù)據(jù)中心、前沿領(lǐng)域等核心場景

2024-01-09 13:25:01

在Vivado中禁止自動(dòng)生成BUFG(Buffered Clock Gate)可以通過以下步驟實(shí)現(xiàn)。 首先,讓我們簡要了解一下什么是BUFG。BUFG是一個(gè)時(shí)鐘緩沖器,用于緩沖輸入時(shí)鐘信號(hào),使其更穩(wěn)

2024-01-05 14:31:06 454

454 有些時(shí)候在寫完代碼之后呢,Vivado時(shí)序報(bào)紅,Timing一欄有很多時(shí)序問題。

2024-01-05 10:18:36 291

291 從互聯(lián)網(wǎng)、到移動(dòng)互聯(lián)網(wǎng),再到產(chǎn)業(yè)互聯(lián)網(wǎng),中國互聯(lián)網(wǎng)發(fā)展已經(jīng)有20多年,近十年則是產(chǎn)業(yè)互聯(lián)網(wǎng)迅猛發(fā)展的十年。近幾年,隨著中國數(shù)字經(jīng)濟(jì)的高速發(fā)展及國家的利好政策,產(chǎn)業(yè)數(shù)字化正迎來了十年來最好的時(shí)間窗口

2024-01-04 11:57:40

CMOS 邏輯由至少兩個(gè)晶體管組成:一個(gè) n 溝道 MOS FET 和一個(gè) p 溝道 MOS FET。晶體管數(shù)量最少的邏輯電路是反相器(邏輯反相電路),由1個(gè)n溝道MOS和1個(gè)p溝道MOS組成。換句話說,它需要相當(dāng)于兩個(gè)晶體管的硅面積。

2023-12-28 12:34:14 386

386 芯片原子鐘賽思是一家為萬物互聯(lián)同頻的時(shí)頻科技企業(yè),基于業(yè)界的時(shí)頻科研與方案能力,賽思打造出軟硬一體化的時(shí)頻產(chǎn)品體系,面向電力、交通、通信、智能樓宇、數(shù)據(jù)中心、前沿領(lǐng)域等核心場景提供解決方案,持續(xù)為

2023-12-25 14:31:21

vivado出現(xiàn)安裝問題剛開始還以為是安裝路徑包含中文空格了,重裝的注意了一下,發(fā)現(xiàn)還是這個(gè)問題。。。。后來又一頓操作猛如虎,終于發(fā)現(xiàn)了問題。出這個(gè)問題的原因是vivado壓縮包解壓的路徑包含中文了把解壓文件放到不含中文的地方,再重新安裝,安裝路徑也不能含中文。然后。。。。。然后就安裝完成了

2023-12-22 10:56:33 0

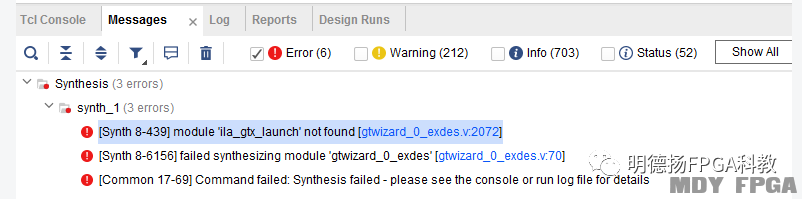

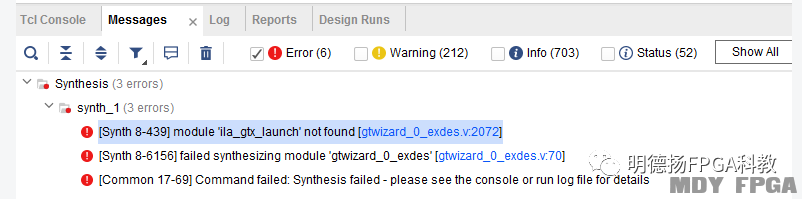

0 【關(guān)鍵問題!!!!重要!!!】VIVADO會(huì)在MESSAGE窗口出提示很多錯(cuò)誤和警告信息!

2023-12-15 10:11:22 666

666

模數(shù)轉(zhuǎn)換器AD9625的評(píng)估板AD-FMCADC3-EBZ能不能和賽靈思的Virtex7系列FPGA開發(fā)板連接,我看到他們都具備JESD204B接口,物理接口上能直接連嗎?還是說需要在使用轉(zhuǎn)換接口來連接?

2023-12-08 08:25:12

。新款PXIe嵌入式控制器第一次在單槽尺寸內(nèi)提供了面向未來的PCIe Gen 4能力。 該款符合PXI-5 PXIe硬件規(guī)范2.0的控制器,集成了第11代英特爾酷i5處理器,32 GB DDR4內(nèi)存

2023-12-01 09:21:15 306

306

應(yīng)用需求,多元化發(fā)展。

此外,集成了FPGA 架構(gòu)、硬核CPU 子系統(tǒng)(ARM/MIPS/MCU)及其他硬核IP 的芯片已經(jīng)發(fā)展到了一個(gè)“關(guān)鍵點(diǎn)”,它將在今后數(shù)十年中得到廣泛應(yīng)用,為系統(tǒng)設(shè)計(jì)人員提供

2023-11-08 17:19:01

MLX90423是一款面向未來的產(chǎn)品,適用于制動(dòng)等ADAS應(yīng)用。與其他線性位置感應(yīng)解決方案相比,該器件具備極高的性價(jià)比。

2023-11-03 12:44:39 367

367 為什么都是用的面向過程編程

2023-10-24 07:39:28

超聲波時(shí)靈使不靈,怎么辦呢??

2023-10-19 06:22:18

量化

七、Vitis AI 通過遷移學(xué)習(xí)訓(xùn)練自定義模型

八、Vitis AI 將自定義模型編譯并部署到KV260中

鋪墊

Vitis AI 是什么?

Vitis AI 是賽靈思公司推出的一款綜合 AI

2023-10-14 15:34:26

電子發(fā)燒友網(wǎng)為你提供ADI(ADI)HMC954: 32 Gbps, 2:1 Mux with Programmable Output Voltage Data Sheet相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè)

2023-10-13 18:32:27

電子發(fā)燒友網(wǎng)為你提供ADI(ADI)HMC955: 32 Gbps, 1:2 Demux with Programmable Output Voltage Data Sheet相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè)

2023-10-13 18:32:14

電子發(fā)燒友網(wǎng)站提供《面向未來汽車應(yīng)用的LIN總線系統(tǒng).doc》資料免費(fèi)下載

2023-10-09 15:00:31 0

0 面向未來,金融機(jī)構(gòu)應(yīng)用大模型的能力,將成為關(guān)鍵競爭力

2023-09-21 09:14:47 752

752

中國算力底座。 而且華為創(chuàng)始人任正非也曾直言“第四次工業(yè)革命基礎(chǔ)就是大算力”。說明華為已經(jīng)在積蓄力量。 按照孟晚舟的表述,華為All Intelligence啟動(dòng),華為將從過去十年從All IP

2023-09-20 17:17:30 665

665 Vivado 設(shè)計(jì)分為 Project Mode 和 Non-project Mode 兩種模式,一般簡單設(shè)計(jì)中,我們常用的是 Project Mode。在本手冊(cè)中,我們將以一個(gè)簡單的實(shí)驗(yàn)案例,一步一步的完成 Vivado的整個(gè)設(shè)計(jì)流程。

2023-09-20 07:37:39

想到要寫這一系列關(guān)于工具和方法學(xué)的小文章是在半年多前,那時(shí)候Vivado?已經(jīng)推出兩年,陸續(xù)也接觸了不少客戶和他們的設(shè)計(jì)。我所在的部門叫做“Tools & Methodology

2023-09-20 06:31:14

未來汽車到底怎么樣?如果這個(gè)問題放到20年前,人們或許很難設(shè)想汽車在今天會(huì)同智能化與電動(dòng)化如此密不可分。新技術(shù)正在以令人驚嘆的速度迭代,這也意味著很多今天尚受爭議的革新,很可能明天就會(huì)成為現(xiàn)實(shí)。

2023-09-18 15:27:05 215

215

Vivado是Xilinx公司2012年推出的新一代集成開發(fā)環(huán)境,它強(qiáng)調(diào)系統(tǒng)級(jí)的設(shè)計(jì)思想及以IP為核心的設(shè)計(jì)理念,突出IP核在數(shù)字系統(tǒng)設(shè)計(jì)中的作用。

2023-09-17 15:37:31 1059

1059

電子發(fā)燒友網(wǎng)站提供《Vivado Design Suite教程:動(dòng)態(tài)功能交換.pdf》資料免費(fèi)下載

2023-09-14 15:13:43 0

0 電子發(fā)燒友網(wǎng)站提供《Vivado設(shè)計(jì)套件Tcl命令參考指南.pdf》資料免費(fèi)下載

2023-09-14 10:23:05 1

1 電子發(fā)燒友網(wǎng)站提供《Vivado設(shè)計(jì)套件用戶指南.pdf》資料免費(fèi)下載

2023-09-14 09:55:18 2

2 電子發(fā)燒友網(wǎng)站提供《Vivado Design Suite用戶指南:使用約束.pdf》資料免費(fèi)下載

2023-09-13 15:48:39 0

0 電子發(fā)燒友網(wǎng)站提供《Vivado Design Suite用戶指南:綜合.pdf》資料免費(fèi)下載

2023-09-13 15:47:40 0

0 電子發(fā)燒友網(wǎng)站提供《Vivado設(shè)計(jì)套件用戶指南:邏輯仿真.pdf》資料免費(fèi)下載

2023-09-13 15:46:41 0

0 電子發(fā)燒友網(wǎng)站提供《Vivado設(shè)計(jì)套件用戶:使用Vivado IDE的指南.pdf》資料免費(fèi)下載

2023-09-13 15:25:36 3

3 電子發(fā)燒友網(wǎng)站提供《UltraFast Vivado HLS方法指南.pdf》資料免費(fèi)下載

2023-09-13 11:23:19 0

0 Vivado設(shè)計(jì)套件,是FPGA廠商賽靈思公司2012年發(fā)布的集成設(shè)計(jì)環(huán)境。包括高度集成的設(shè)計(jì)環(huán)境和新一代從系統(tǒng)到IC級(jí)的工具,這些均建立在共享的可擴(kuò)展數(shù)據(jù)模型和通用調(diào)試環(huán)境基礎(chǔ)上。這也是一個(gè)基于AMBA

2023-09-06 17:55:44

未來汽車到底怎么樣?如果這個(gè)問題放到20年前,人們或許很難設(shè)想汽車在今天會(huì)同智能化與電動(dòng)化如此密不可分。新技術(shù)正在以令人驚嘆的速度迭代,這也意味著很多今天尚受爭議的革新,很可能明天就會(huì)成為現(xiàn)實(shí)。

2023-08-31 17:38:43 244

244

一是智能化。未來戰(zhàn)場上的可重構(gòu)機(jī)器人需要具備更高的智能水平。通過借鑒結(jié)合人工智能領(lǐng)域的最新研究成果,可重構(gòu)機(jī)器人將能夠?qū)崿F(xiàn)自主感知、自主學(xué)習(xí)和決策能力的全方位提升。它們能夠自主識(shí)別目標(biāo)、判斷敵我差距并迅速做出反應(yīng),提高作戰(zhàn)效率和生存能力。

2023-08-30 15:59:08 432

432

FPGA開發(fā)中使用頻率非常高的兩個(gè)IP就是FIFO和BRAM,上一篇文章中已經(jīng)詳細(xì)介紹了Vivado FIFO IP,今天我們來聊一聊BRAM IP。

2023-08-29 16:41:49 2602

2602

2023 年 RISC-V 中國峰會(huì)上,倪光南院士表示,“RISC-V 的未來在中國,而中國半導(dǎo)體芯片產(chǎn)業(yè)也需要 RISC-V,開源的 RISC-V 已成為中國業(yè)界最受歡迎的芯片架構(gòu)”。大家怎么看呢?

2023-08-26 14:16:43

本文詳細(xì)介紹了vivado軟件和modelsim軟件的安裝,以及vivado中配置modelsim仿真設(shè)置,每一步都加文字說明和圖片。

2023-08-07 15:48:00 1478

1478

Vivado IP核提供了強(qiáng)大的FIFO生成器,可以通過圖形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 1616

1616

雙擊桌面圖標(biāo)打開Vivado 2017.2,或者選擇開始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2023-07-30 09:39:11 399

399

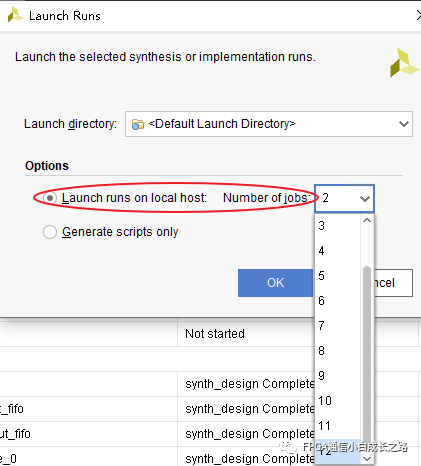

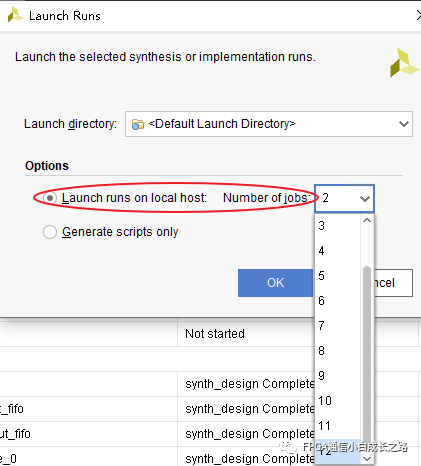

Vivado中對(duì)工程進(jìn)行綜合時(shí),會(huì)彈出如下對(duì)話框

2023-07-24 15:28:54 489

489

Modelsim是十分常用的外部仿真工具,在Vivado中也可以調(diào)用Modelsim進(jìn)行仿真,下面將介紹如何對(duì)vivado進(jìn)行配置并調(diào)用Modelsim進(jìn)行仿真,在進(jìn)行仿真之前需要提前安裝Modelsim軟件。

2023-07-24 09:04:43 1817

1817

vivado開發(fā)軟件自帶了仿真工具,下面將介紹vivado的仿真流程,方便初學(xué)者進(jìn)行仿真實(shí)驗(yàn)。

2023-07-18 09:06:59 2131

2131

vivado的工程創(chuàng)建流程對(duì)于大部分初學(xué)者而言比較復(fù)雜,下面將通過這篇博客來講解詳細(xì)的vivado工程創(chuàng)建流程。幫助自己進(jìn)行學(xué)習(xí)回顧,同時(shí)希望可以對(duì)有需要的初學(xué)者產(chǎn)生幫助。

2023-07-12 09:26:57 1098

1098

Timing Commander 軟件 for Programmable Buffers

2023-07-11 20:27:38 0

0 在2023年上海車展期間,安波福更面向中國市場推出了創(chuàng)新的全棧式解決方案,涵蓋系統(tǒng)架構(gòu)、軟件、硬件等多個(gè)層面,助力整車廠商加速打造面向未來的軟件定義的汽車,成就更加可持續(xù)的移動(dòng)出行未來。

2023-07-06 17:36:40 917

917 電子發(fā)燒友網(wǎng)站提供《無所不知的神器構(gòu)建.zip》資料免費(fèi)下載

2023-07-04 11:22:54 0

0 今天介紹一下,如何在Vivado中添加時(shí)序約束,Vivado添加約束的方法有3種:xdc文件、時(shí)序約束向?qū)В–onstraints Wizard)、時(shí)序約束編輯器(Edit Timing Constraints )

2023-06-26 15:21:11 1833

1833

FPGA開發(fā)過程中,vivado和quartus等開發(fā)軟件都會(huì)提供時(shí)序報(bào)告,以方便開發(fā)者判斷自己的工程時(shí)序是否滿足時(shí)序要求。

2023-06-23 17:44:00 531

531

在仿真Vivado IP核時(shí)分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-20 14:23:57 622

622

展示了基于先進(jìn)制造材料與工藝的現(xiàn)代濾波器研究現(xiàn)狀,進(jìn)一步分析了濾波器在通訊系統(tǒng)中的發(fā)展趨勢(shì)與存在形態(tài),為面向未來的新-代微波器件設(shè)計(jì)提供參考。

2023-06-19 15:40:19 541

541

Vivado Schematic中的實(shí)線和虛線有什么區(qū)別?

2023-06-16 16:53:42 698

698

Vivado Schematic中的實(shí)線和虛線有什么區(qū)別?

2023-06-06 11:13:39 670

670

大家好,我的需求是將FPGA(賽靈思K7)采集的數(shù)據(jù)發(fā)送至工控機(jī)(Linux),數(shù)據(jù)量為每秒5M字節(jié),并解析工控機(jī)發(fā)送的控制指令(50字節(jié)/秒),有同個(gè)問題如下:

1.ARM選什么型號(hào)比較好

2023-06-02 18:25:04

。通過 CXA 中的 X 系列可擴(kuò)展性獲得基本功能 -并期待更多。我們無法預(yù)測未來,但是德科技可以利用我們面向未來的測試資產(chǎn)幫助您塑造未來。X 系列是一種進(jìn)化的信

2023-05-26 15:05:49

周(Display Week 2023),展示面向未來顯示器的第二代LED技術(shù),包括基于WICOP Pixel技術(shù)的microLED顯示器和有助于用戶保持眼睛健康的低藍(lán)光(LBL)顯示器。

2023-05-25 10:14:05 402

402 及全場景OpenHarmony解決方案,促進(jìn)萬物互聯(lián)產(chǎn)業(yè)的繁榮發(fā)展。本大賽面向所有OpenHarmony開發(fā)者,只要完成注冊(cè),認(rèn)證即可報(bào)名參與OpenHarmony創(chuàng)新賽,獲取OpenHarmony開源

2023-05-17 16:52:38

Vivado 軟件提供了HDL編寫中常用的示例,旨在幫助初學(xué)者更好地理解和掌握HDL編程,這里分享一下verilog代碼示例。

2023-05-16 16:58:06 627

627 如果你正在使用Vivado開發(fā)套件進(jìn)行設(shè)計(jì),你會(huì)發(fā)現(xiàn)綜合設(shè)置中提供了許多綜合選項(xiàng)。這些選項(xiàng)對(duì)綜合結(jié)果有著潛在的影響,而且能夠提升設(shè)計(jì)效率。為了更好地利用這些資源,需要仔細(xì)研究每一個(gè)選項(xiàng)的功能。本文將要介紹一下Vivado的綜合參數(shù)設(shè)置。

2023-05-16 16:45:50 1855

1855

本文主要介紹Vivado布線參數(shù)設(shè)置,基本設(shè)置方式和vivado綜合參數(shù)設(shè)置基本一致,將詳細(xì)說明如何設(shè)置布線參數(shù)以優(yōu)化FPGA設(shè)計(jì)的性能,以及如何設(shè)置Vivado壓縮BIT文件。

2023-05-16 16:40:45 2955

2955

綜合性服務(wù)平臺(tái),大賽始于2015年由深圳華秋電子有限公司主辦,面向硬科技初創(chuàng)企業(yè)及團(tuán)隊(duì)的賽事。大賽將協(xié)同硬科技產(chǎn)業(yè)生態(tài)伙伴,搭建創(chuàng)業(yè)項(xiàng)目與資本之間的橋梁,挖掘孵化行業(yè)未來領(lǐng)軍企業(yè)。

2023-05-16 11:45:11

Timing Commander 軟件 for Programmable Buffers

2023-05-15 19:16:04 0

0 5?月?13?日,開源未來發(fā)展峰會(huì)在重慶隆重召開。在上午的主論壇中,宣布了一系列合作共建項(xiàng)目,并發(fā)布開源戰(zhàn)略合作重慶宣言。 本屆峰會(huì)以“天工開物,面向未來”為主題,由重慶市發(fā)展改革委、重慶市科技局

2023-05-15 09:17:52 609

609

5G網(wǎng)絡(luò),全球廠商已發(fā)布一千八百余款5G終端。面向未來,5G-Advanced將在持續(xù)升級(jí)已有網(wǎng)絡(luò)能力的基礎(chǔ)上,增強(qiáng)AR/VR、物聯(lián)網(wǎng)和空天一體化等新能力,以賦能新場景新業(yè)務(wù)的應(yīng)用,并通過減少碳排放

2023-05-10 10:39:03

的發(fā)展,一個(gè)好的 AI 技術(shù)產(chǎn)品該如何迭代與運(yùn)營……

為了能夠與廣大開發(fā)者一起更好地?fù)肀?AI 技術(shù)的發(fā)展,5 月 13 日,由天工開物開源基金會(huì)、開源中國社區(qū)聯(lián)合發(fā)起的,面向廣大開發(fā)者的中國開源未來

2023-05-09 09:49:41

隨著聊天機(jī)器人在理解和響應(yīng)用戶問題方面越來越好,它可能會(huì)不斷進(jìn)化并成為主流。未來的聊天機(jī)器人可能會(huì)帶來豐富的會(huì)話用戶界面,使用戶可以自然地與計(jì)算機(jī)、智能手機(jī)和機(jī)器人等進(jìn)行交互。

2023-05-08 09:38:15 532

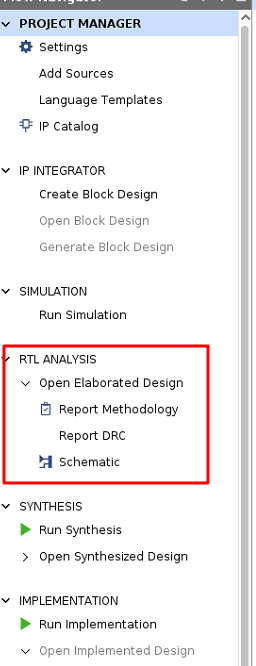

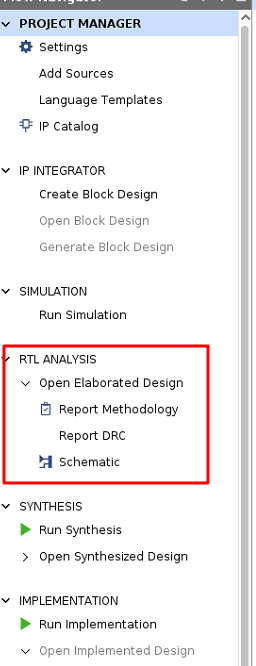

532 在Vivado的界面中,有個(gè)RTL ANALYSIS->Open Elaborated Design的選項(xiàng),可能很多工程師都沒有使用過。因?yàn)榇蠹一径际菑腞un Synthesis開始的。

2023-05-05 16:00:18 803

803

關(guān)于 Tcl 在 Vivado中的應(yīng)用文章從 Tcl 的基本語法和在 Vivado 中的 應(yīng)用展開,繼上篇《用 Tcl 定制 Vivado 設(shè)計(jì)實(shí)現(xiàn)流程》介紹了如何擴(kuò)展甚 至是定制 FPGA

2023-05-05 15:34:52 1612

1612

今天推出Xilinx已發(fā)布的《Vivado使用誤區(qū)與進(jìn)階》系列:用TCL定制Vivado設(shè)計(jì)實(shí)現(xiàn)流程。

2023-05-05 09:44:46 674

674

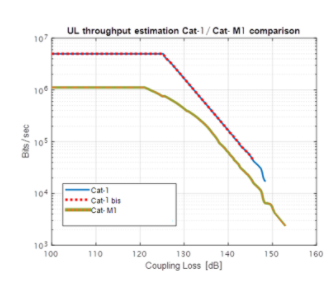

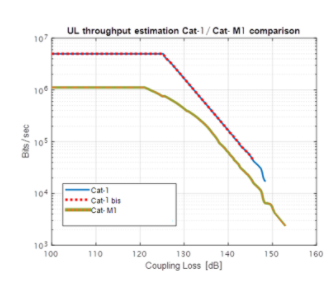

與LTE-M相比,CAT-1有幾個(gè)關(guān)鍵優(yōu)勢(shì)。它提供了更高的最大吞吐量,這可能需要某些應(yīng)用程序,并且在上傳或下載大量數(shù)據(jù)時(shí)功耗更低(傳輸速度更快,時(shí)間更短),以及略低的延遲。然而,大多數(shù)物聯(lián)網(wǎng)設(shè)備很少需要高吞吐量或容量,因?yàn)樗鼈儽举|(zhì)上設(shè)計(jì)為以低數(shù)據(jù)速率運(yùn)行。因此,這些優(yōu)勢(shì)并沒有為智能城市和公用事業(yè)提供令人信服的用例。

2023-05-05 09:26:46 812

812

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因?yàn)楣こ讨泻芏郔P核不能用所以在重新生成過程中發(fā)現(xiàn)了這個(gè)問題,還請(qǐng)大神告知是怎么回事?

2023-04-24 23:42:21

開放原子開源大賽OpenHarmony創(chuàng)新賽,正式啟動(dòng)啦!

“OpenHarmony創(chuàng)新賽”是開放原子全球開源大賽下開設(shè)的創(chuàng)新賽道,面向企業(yè)、個(gè)人、高校師生等廣大開發(fā)者,聚焦OpenHarmony

2023-04-23 11:15:44

Keysight Agilent HP 可以通過我們面向未來的測試資產(chǎn)幫助您塑造未來。X 系列是一種跨越儀器、測量和軟件的信號(hào)分析的進(jìn)化方法。它使您能夠靈活地滿足

2023-04-18 17:13:45

用戶體驗(yàn),搭建更多面向未來的交互應(yīng)用新場景。礪算科技礪算科技致力于自主研發(fā)全性能TrueGPU軟硬件體系,擁有自研架構(gòu),研發(fā)自有知識(shí)產(chǎn)權(quán)的國產(chǎn)GPU芯片,覆蓋“端+云+邊”全

2023-04-17 09:35:21 681

681

Xilinx的新一代設(shè)計(jì)套件Vivado相比上一代產(chǎn)品 ISE,在運(yùn)行速度、算法優(yōu)化和功能整合等很多方面都有了顯著地改進(jìn)。但是對(duì)初學(xué)者來說,新的約束語言 XDC 以及腳本語言 Tcl 的引入則成為

2023-04-15 09:43:09 956

956 未來三十年中,20項(xiàng)影響世界的核心科技趨勢(shì)

2023-04-14 10:33:03 544

544

虹科分享HK-Edgility面向未來的安全SD-WAN通過上期的文章,我們了解到虹科HK-Edgility軟件系統(tǒng)《隨時(shí)隨地保護(hù)您的遠(yuǎn)程工作解決方案》的解決方案。今天的文章,我們將帶您了解虹科系

2023-04-13 14:52:59 288

288

Keysight Agilent HP 可以通過我們面向未來的測試資產(chǎn)幫助您塑造未來。X 系列是一種跨越儀器、測量和軟件的信號(hào)分析的進(jìn)化方法。它使您能夠靈活地滿足現(xiàn)在和

2023-04-07 16:31:12

PLUG AC INTERCHANGE ALL COUNTRY

2023-03-31 11:06:58

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

HDP-ALL-0004

2023-03-29 22:43:01

NCEP40T20ALL

2023-03-28 18:07:38

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論