在我從事半導體設備的職業生涯之初,晶圓背面是個麻煩問題。當時發生了一件令我記憶深刻的事:在晶圓傳送的過程中,幾片晶圓從機器人刀片上飛了出來。收拾完殘局后,我們想到,可以在晶圓背面沉積各種薄膜,從而降低其摩擦系數。放慢晶圓傳送速度幫助我們解決了這個問題,但我們的客戶經理不太高興,因為他們不得不向客戶解釋由此導致的產量減少的原因。

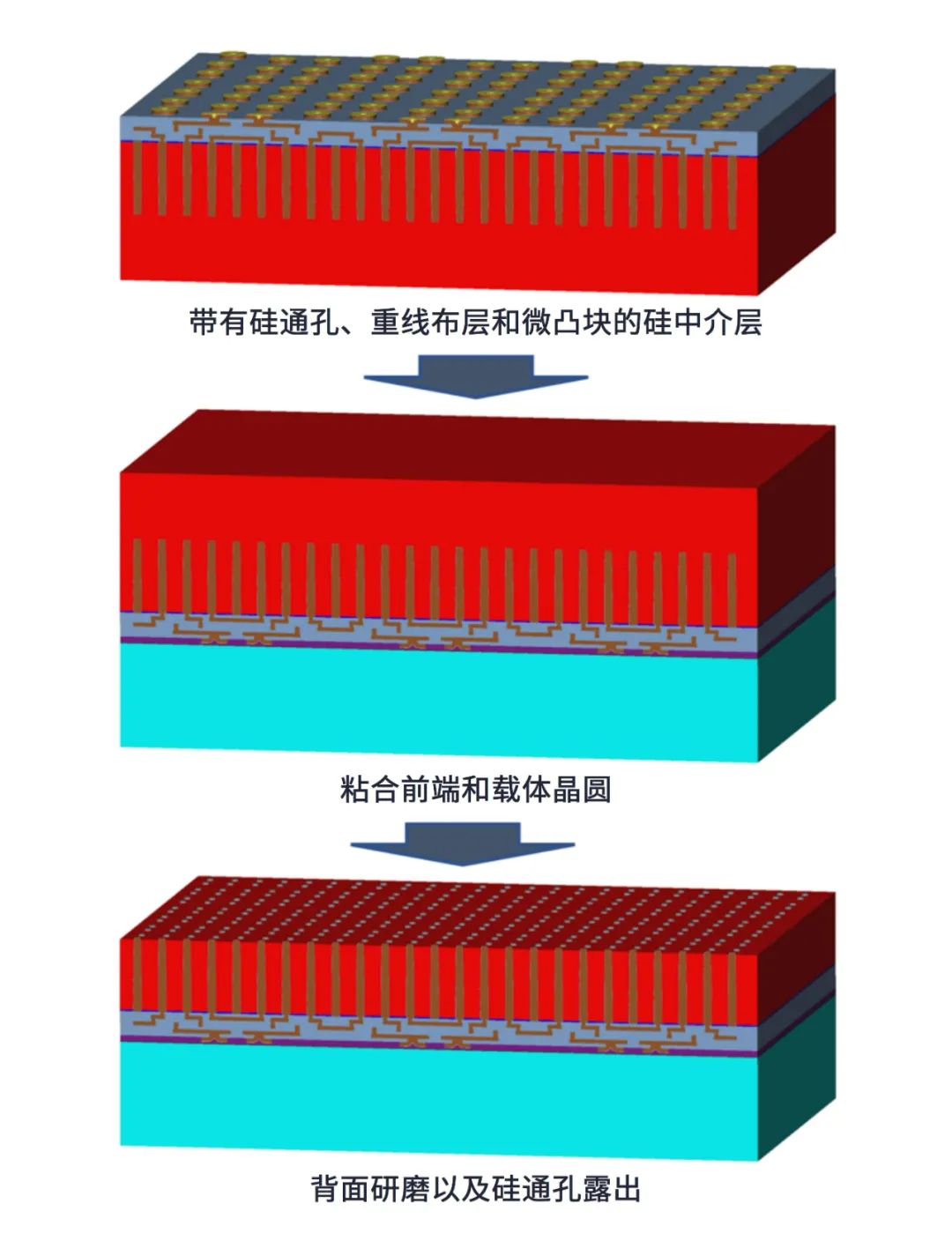

盡管初識晶圓背面的過程不太順利,但當2010年代早期Xilinx Virtex-7系列FPGA發布時,我開始更加關注這個領域。Xilinx的產品是首批采用“堆疊硅互連技術”的異構集成的FPGA[1]。該技術使用了在不同的FPGA組件之間傳遞電信號或電力的硅中介層,這一中介層通過創建部分通過硅晶圓的硅通孔 (TSV) 并在頂部創建信號重布線層而成形。通過對晶圓背面進行工藝處理,連接硅通孔的兩端:晶圓的正面暫時粘到一個載體晶圓上,然后倒置硅中介層進行工藝處理,隨后使用背面研磨和刻蝕來暴露硅通孔。Xilinx產品推出時,我已經離開這個行業,回到了研究生院。在課堂上,硅通孔的金屬化是個熱門話題,而隨著異構集成不斷發展,晶圓背面也在工程師中成為了更有意思的話題。

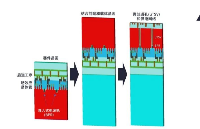

圖1:硅中介層的工藝處理。通孔和初始金屬化之后,研磨晶圓背面直至到達通孔

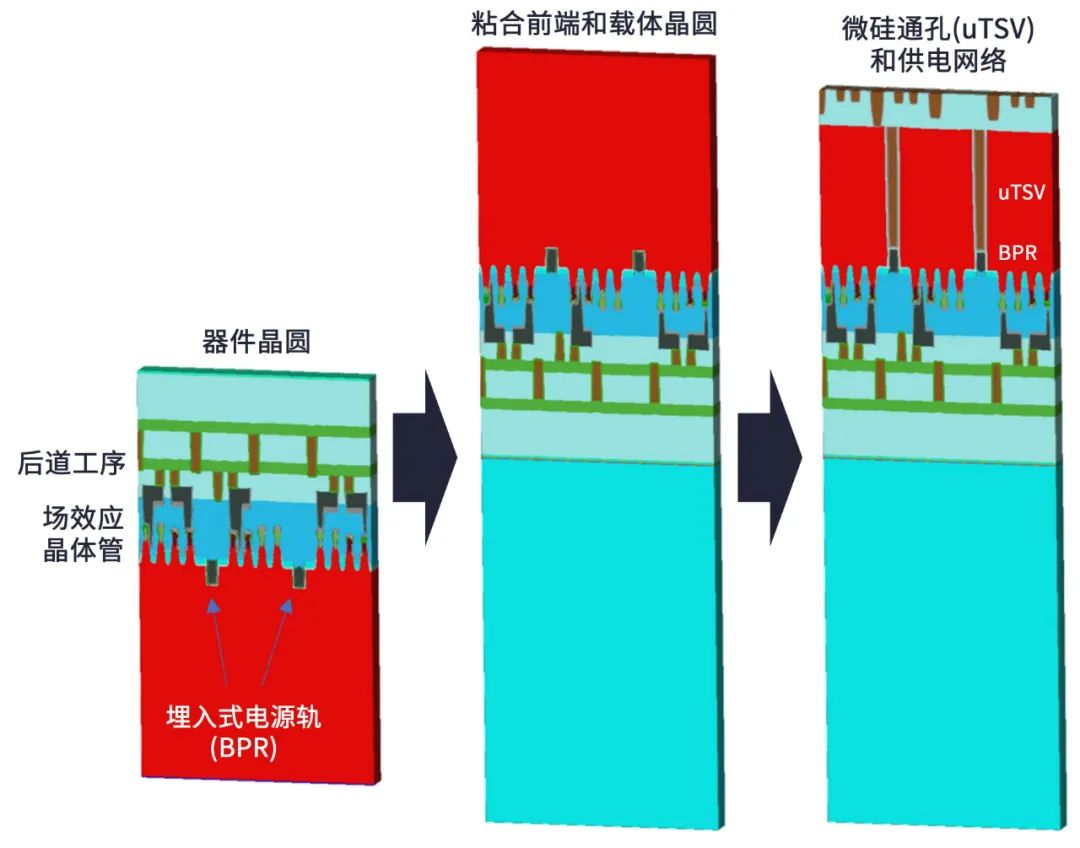

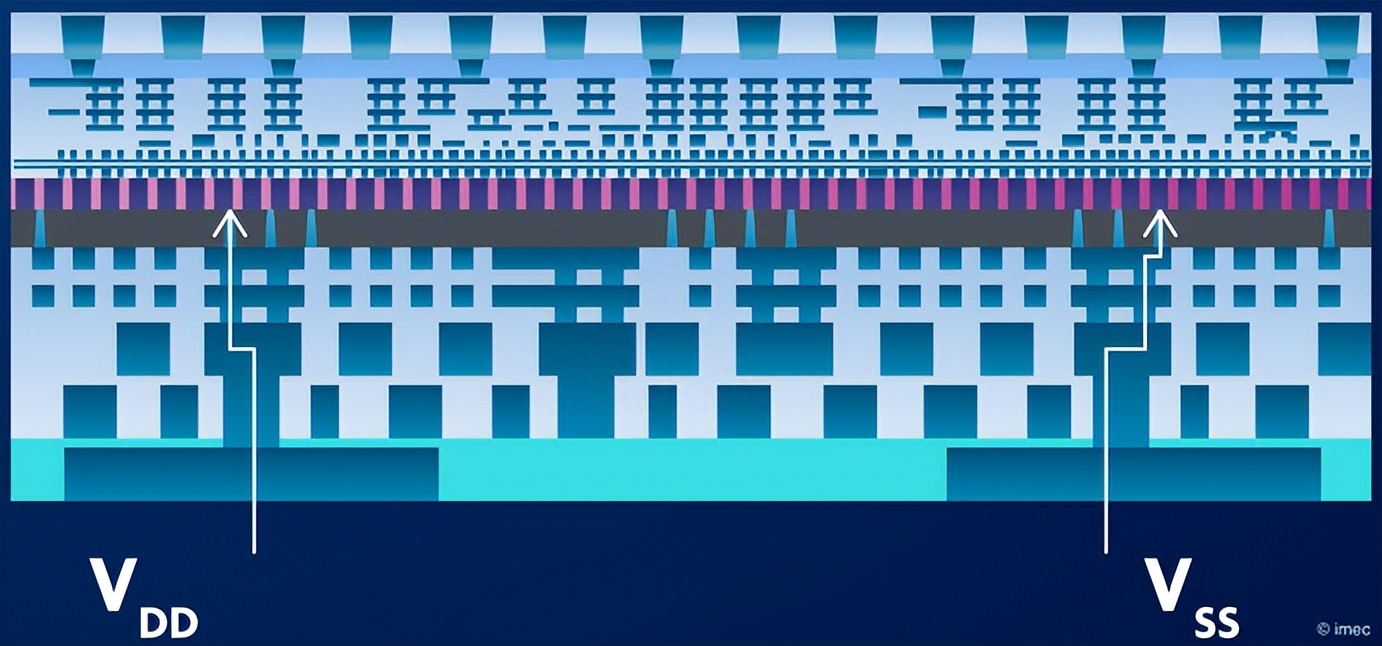

雖然Xilinx FPGA使用了硅中介層來處理信號傳輸和帶寬要求,但去除中介層、直接使用晶圓背面進行電氣布線的做法會更有前瞻性。背面供電是“背面”架構的示例之一,它的供電不是來源于傳統的晶圓正面的后道工序,而是背面。這種架構可能可以減少電源軌和有源器件之間的電壓降。作為背面架構的示例,imec正嘗試在鰭片架構中使用埋入式電源軌[2]。在imec的工藝流程中,導軌位于鰭片之間,類似DRAM(動態隨機存取存儲器)埋入式字線。為了信號傳輸建成后道工序后,在器件晶圓的背面創建硅通孔,連通埋入式導軌。為了供電也可以在背面進行進一步的互連。

圖2:參考資料[2],使用埋入式電源軌進行背面供電(不按比例)

至少出于性能原因,器件晶圓背面的空間看起來很有發展潛力。把電源軌從前端移到背面可以緩解晶圓正面的擁塞,實現單元微縮并減少電壓降。領先的半導體邏輯企業深知背面供電的優勢,正積極開發背面分布網絡。2021年年中,英特爾宣布將使用公司的“PowerVia”技術進行晶背供電;臺積電也計劃在他們下一節點的技術中使用埋入式電源軌[3]。我們期待看到晶圓背面的未來發展。

審核編輯:劉清

-

FPGA

+關注

關注

1620文章

21507瀏覽量

598836 -

半導體

+關注

關注

334文章

26305瀏覽量

209906 -

DRAM芯片

+關注

關注

1文章

84瀏覽量

17973 -

TSV技術

+關注

關注

0文章

17瀏覽量

5649 -

隨機存取存儲器

+關注

關注

0文章

44瀏覽量

8941

原文標題:晶圓的另一面:背面供電領域的最新發展

文章出處:【微信號:泛林半導體設備技術,微信公眾號:泛林半導體設備技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

使用單一晶圓加工工具蝕刻晶圓背面薄膜的方法

晶圓的另一面:背面供電領域的最新發展研究

晶圓的另一面:背面供電領域的最新發展研究

評論