0 引言

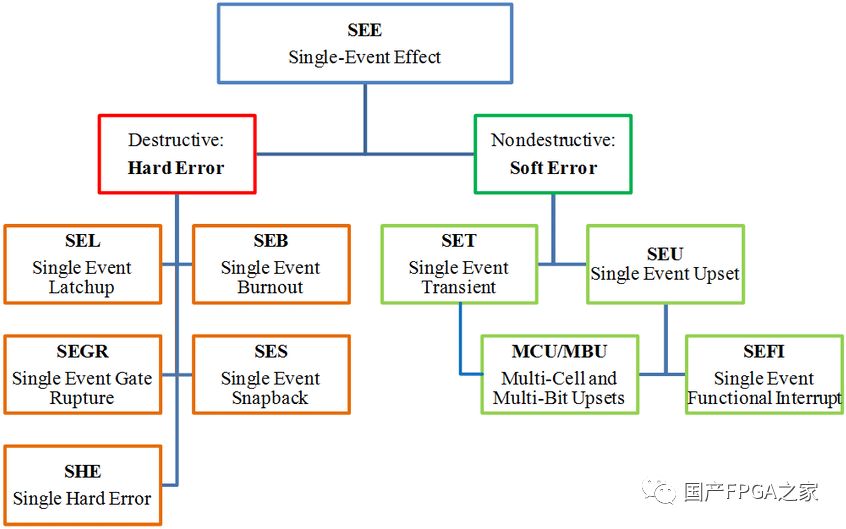

隨著航天技術的發展,空間任務日益復雜化、多樣化,未來航天系統對處理器的性能要求越來越高。在一些航天設備如星載 ATP 等系統的電子模塊設計中,基于 SRAM 的現場可編程門陣列(FPGA)得到了日益廣泛的應用。空間環境中的電子系統設計,不僅要滿足高性能,而且其數據處理、傳輸和控制的準確性和可靠性也必須得到保證。對于機載、星載、空間武器和其他空間應用電子系統,往往暴露在形形色色的電磁輻射環境中,如α粒子、宇宙射線、外太空強輻射等等惡劣環境,加之一些電子系統工作在地面的高電磁輻射環境中,這些輻射環境中充滿了各種高能粒子,高能粒子撞擊工作中的電子器件會引發輻射效應,如單粒子翻轉(SEU)等,并導致器件發生故障,由輻射效應引起的軟錯誤是導致空間環境中電子系統失效的重要原因之一[1]。

在提高系統可靠性與安全性方面,避錯與容錯技術是常用的兩種關鍵技術。微電子抗輻射加固技術[2],通過對材料選取、工藝結構設計等方面進行加固設計,在物理層消除導致損傷的各類寄生參數, 能有效提高電子器件的抗輻射能力。但是僅在物理層上對系統進行故障防護不能滿足惡劣環境中的系統可靠性要求,還需要從電路設計方面對系統功能進行保護。運用錯誤校正碼(ECC)技術[3],在數據包的后端添加額外的校驗數據位,來實現讀取 / 寫入數據的準確性,能在一定程度上對存儲器進行檢錯和糾錯。容錯設計技術,如采用冗余設計來“屏蔽”或“隔離”故障,如信息冗余[4]、硬件冗余[5]等,進而在一定時期內將故障的影響掩蓋起來,使發生故障的電子系統在一定時期內仍能正常工作,但這種方式并未排除故障,隨著故障的累積和疊加,系統仍然可能失效,所以賦予系統故障自修復能力能有效減少故障累積,提高系統的可靠性。

本文從故障容錯和故障自修復角度對系統進行芯片級的可靠性設計,提出了一種基于 SRAM 型 FPGA 的實時容錯自修復系統結構,并將該設計結構在 Xilinx Virtex-6 FPGA 上進行了設計驗證。

1 基于動態部分重構的模塊修復

FPGA 的配置可分為靜態配置和動態配置,靜態配置通常對整個 FPGA 模塊進行重新配置,系統功能在配置過程時中斷,并在配置結束后改變系統功能。動態配置,又稱為動態部分重構,能夠在不干擾 FPGA 內部其他模塊工作的同時動態地對部分區域的邏輯功能進行修改。其核心思想是將 FPGA 內部的邏輯資源從物理布局上劃分為靜態區域和若干個動態區域。每個動態區域可以對應有多個配置文件,以實現不同的功能,將這些配置文件事先存放在片外存儲器中。在系統運行的不同時刻,根據系統的實際需求加載不同的配置文件到同一個動態區域來實現相應的邏輯功能。在某一動態區域進行功能切換時,不影響靜態區域和其他動態區域的邏輯功能,系統依然處于連續運行狀態。

動態部分重構技術能對 FPGA 的部分資源實現分時復用,使芯片能夠在不同時刻實現不同的功能,提高了芯片資源的利用率,已廣泛應用于工業系統設計中,如文獻[6]中結合動態部分重構技術對工業傳感器數據采集系統進行設計,針對不同的傳感器切換不同的功能。該技術還可應用于可重構計算[7]、可進化硬件[8-9]、容錯設計[10-14]等方面。將動態部分重構技術和冗余技術結合,即將冗余設計中各冗余模塊分別置于一動態區域中,在故障發生時通過動態重構對故障模塊進行修復,可以避免故障的累積和疊加,在容錯的同時賦予系統故障自修復能力。

2 粗粒度和細粒度的三模冗余自修復結構

2.1 粗粒度的三模冗余設計結構

典型的模塊冗余技術——N 模冗余設計:將功能模塊復制為 N 份,N 個模塊具有相同的輸入,N 個模塊的輸出經過多數表決器表決輸出。N 模冗余系統在工作過程中能同時容忍不超過半數的冗余模塊發生故障而不影響最終的系統輸出。隨著冗余模塊的數量增加,系統的容錯能力提高,但同時系統的硬件資源開銷和功耗增大,綜合考慮容錯能力和資源開銷,三模冗余(TMR)技術具有最高的性能表現。

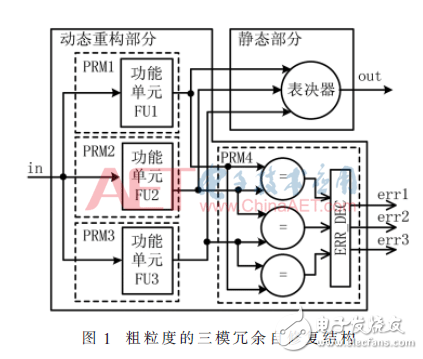

FPGA 的系統通常可以分為多個功能模塊,粗粒度的三模冗余設計結構以整個功能模塊為單位進行冗余設計,如圖 1 所示,即將整個功能模塊作為一個冗余單位,將整個功能模塊復制三份,將每個功能單元模塊 FU1~FU3 配置到單獨的部分重構模塊(PRM)中,使得每個冗余模塊都可以獨立被修復。表決器選擇多數的輸入結果進行輸出。在粗粒度的三模冗余設計結構中,只要兩個冗余模塊的輸出結果正確,就能保證整個模塊輸出正常,當其中任意模塊發生故障時,通過系統的故障檢測機制可進行故障定位,隔離故障區域并進行自修復操作。

2.2 細粒度的三模冗余設計結構

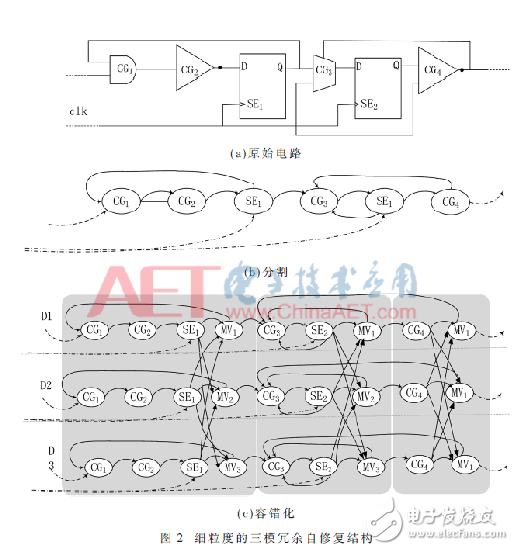

采用粗粒度設計結構能有效提高系統的可靠度,但其仍然存在一些不足,一是當多數表決器出現故障時整個自修復結構本身不可靠;二是由于模塊粒度較大,一些不能導致模塊功能失效的隱性故障持續累積,容易導致多個模塊同時故障,使得防護結構失效。本文中細粒度的三模冗余設計結構能有效減少故障累積,該設計結構將一功能模塊拆分為若干個獨立的時序元件和組合邏輯部分,本文將該設計結構利用圖形化表示來說明,將功能單元模塊中的組合邏輯表示為 CG,時序元件表示為 SE,則利用有向圖表示方法可以將圖 2(a)電路表示為圖 2(b)。

細粒度的三模冗余容錯自修復結構建立在有向圖表示方法基礎之上,其核心思想是,將電路分割為邏輯電路和時序電路,在時序電路輸出插入多數表決器,然后再對原始電路進行三模冗余設計,使得此自修復結構具有三個表決器,因此加強了此結構的故障容錯能力,同時減輕了時序電路引起的錯誤累積,可以成功避免域交叉錯誤的出現。圖 2(a)表示的原始電路,利用有向圖表示方法將原始電路分割開來如圖 2(b)所示,利用 TMR 三模冗余技術將其容錯化如圖 2(c)所示。MV 表示多數表決器(Multiple Voter)在電路時序元件輸出之后插入,利用其三模冗余結構,增強了電路容錯能力。當 D1 模塊的組合、時序電路以及表決器出現故障時,D2 模塊和 D3 模塊通過多數表決器可以檢測到此類故障,并經中斷喚醒處理器進行部分動態重構處理,使得 D1 部分重構區域得以自修復。

細粒度的三模冗余容錯自修復結構同時降低了時序電路引起的錯誤累積的概率,可以成功避免域交叉錯誤的產生。當 D1 模塊的 SE2 電路和 D3 模塊的 CG4 電路同時出現故障的時候,由于在時序電路的輸出端用表決器成功地將 SE2 故障進行檢測和隔離,不會傳遞積累影響下一級的 CG4 錯誤,因此可以成功避免域交叉錯誤的產生。

2.3 可靠度對比

功能模塊在 FPGA 內部的實現可以用邏輯資源來表示,如查找表(LUTs)、觸發器(Flip-Flops)、塊存儲器(BRAM)等。而各邏輯資源的連接和使用通過比特流文件配置來實現。比特流文件由若干個配置幀(frame)組成,配置幀又包含若干個表示配置信息的比特位。在輻射環境中,當 FPGA 中的電路模塊發生單粒子翻轉效應時,并不是模塊任意比特位發生翻轉就會導致模塊功能失效,該模塊功能往往由一些關鍵比特位所決定。考慮該粗粒度的三模冗余設計結構的容錯能力,討論馬爾科夫模型下的三模冗余結構[15],假設功能模塊在時間 t 內功能正常的可靠度隨著時間的推移呈指數遞減,其可靠度可以表示為:

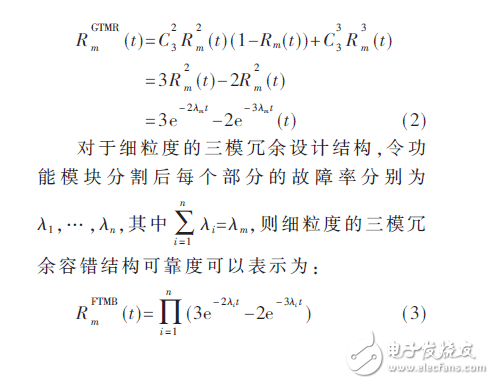

其中λm 表示功能模塊 m 的故障率,其由比特位在單位時間內的翻轉速率和模塊對應的關鍵比特位數量所決定。對于一個三模冗余系統來說只有當兩個或者兩個以上的模塊發生錯誤時系統防護功能才會失效,假設三模冗余系統表決邏輯功能正常,那么對于該粗粒度的三模冗余設計結構其可靠度可以表示為:

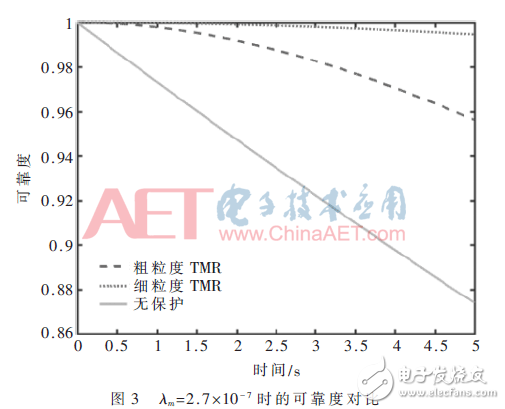

將提出的細粒度的三模冗余結構和粗粒度的三模冗余結構的可靠度進行比較,其可靠度示意圖如圖 3 所示。細粒度的三模冗余結構容錯可靠度相對于粗粒度的可靠度有顯著的提高,但同時細粒度的三模冗余結構會引入額外表決器和故障檢測邏輯,導致額外資源開銷的增加。細粒度的三模冗余結構更適用于對故障率高的電路模塊進行防護。

3 實時故障自修復系統設計

3.1 實時故障自修復系統整體設計結構

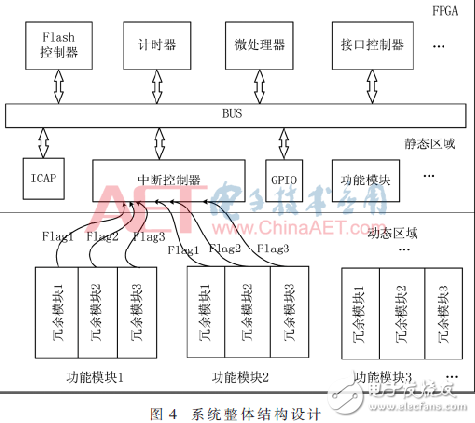

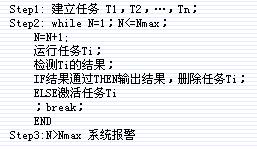

圖 4 給出了一種基于 Xilinx FPGA 實現的故障自修復系統整體結構設計方案。整個系統實現基于 MicroBlaze 軟核的片上微處理器系統,主要劃分為兩個部分:靜態區域和動態部分重構區域。靜態區域主要包括:軟核 MicroBlaze、串口控制器、Flash 控制器等,這部分區域包括了整個關鍵處理模塊不適于動態重構的模塊,主要負責運行低優先級程序和檢測動態重構區域的正常運行。動態部分重構區域是整個電子系統自修復的基礎,所有的自修復操作都在其他模塊監測、控制下有序地進行,保證整個電子系統不間斷正常的工作,其中各個冗余模塊的標準配置文件存放于片外 Flash 中。當系統收到重構請求時,由 Flash 控制器讀取片外存儲器中對應模塊的比特流文件并通過內部配置訪問端口(ICAP)寫入重構區域。動態部分重構區域結合上文提出的容錯方案進行容錯設計,同時 MicroBlaze 負責控制和監測每個動態重構單元的工作情況:比如當設計動態重構單元為三模冗余故障容錯模塊時,當此模塊內部故障檢測單元檢測到發生故障時,通過中斷的形式將信息發送到 MicroBlaze 中,MicroBlaze 讀取此模塊的狀態寄存器以判明故障類型和區域,根據應用場合不同選擇不同的故障自修復策略將此模塊進行有序的自重構,實現故障自修復的同時并不影響系統正常運行。

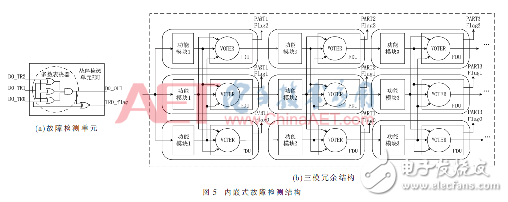

3.2 內嵌式故障檢測結構

采用一內嵌式故障檢測結構對冗余模塊進行故障檢測,該方案將故障檢測單元嵌入到冗余模塊中。圖 5(a)所示為三模冗余容錯自修復結構中以邏輯門描述的故障檢測單元示意圖,該故障檢測單元由多數表決器和異或非門構成,將多數表決器的輸出和檢測的冗余模塊的輸出接到異或非門的輸入端,多數表決器的輸出作為錯誤標志信號 FLAG。當檢測的冗余模塊的輸出和表決器的輸出相同,則異或門輸出為邏輯 1,表示該檢測的冗余模塊無故障發生,若異或門輸出邏輯為 0,則表明檢測的冗余模塊發生故障或故障檢測單元自身發生故障。具有該故障檢測單元的三模冗余結構如圖 5(b)所示。

功能模塊在 FPGA 內部的實現可以用邏輯資源來表示,如查找表(LUTs)、觸發器(Flip-Flops)、塊存儲器(BRAM)等。而各邏輯資源的連接和使用通過比特流文件(Bitstream)配置來實現。比特流文件由若干個配置幀(frame)組成,功能模塊大小也可通過配置幀的數量來表示。

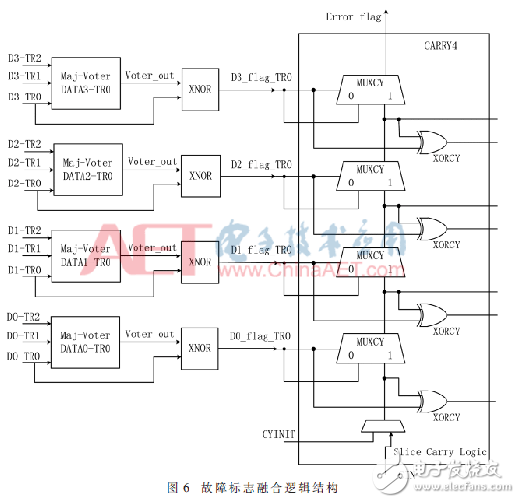

該檢測單元從細粒度的角度對電路輸出的每一位進行比較,也就是說對于一個輸出信號為 N 位的功能模塊來說,采用該故障檢測單元會對每一個冗余模塊會產生 N 個故障標志信號。然而對于一個冗余模塊來說只需要一個標志信號來表明該模塊是否發生故障。對此提出了一種將標志信號進行融合的邏輯結構,該融合邏輯結構采用 FPGA 片內進位鏈邏輯來實現。如圖 6 所示,以 4 位的輸出信號為例,故障檢測單元對 TR1 模塊的輸出位進行檢測,將故障標志信號分別接入進位鏈的 C0~C3 端口。進位鏈 CIN 端口輸入邏輯 1,當無故障發生時進位鏈輸出邏輯 1,當其中一位或者多位錯誤發生時,進位鏈中的二選一選擇器選擇故障標志信號進行傳遞,進位鏈輸出邏輯 0,表示 TR1 模塊發生故障。對于模塊輸出信號位數少于 4 位的情況,可以將進位鏈空閑的輸入端輸入邏輯 1 即可。對于模塊輸出信號位數大于 4 位的情況,可以將前一進位鏈的標志輸出 FLAG 接入后一進位鏈的 CIN 輸入端,將進位鏈串行連接。

4 實驗設計與分析

本節中將上文提出的故障自修系統在 Xilinx XC6VLX240T-1FF1156 FPGA 上進行設計實現,實驗中靜態區域包含了一基于 MicroBlaze 核的片上微處理器系統,該微處理器系統主要負責與上位機進行交互、響應重構請求、控制片外存儲器讀取比特文件數據和控制內部配置訪問端口(ICAP)對重構區域進行重配置等任務。動態區域中將 ITC99 benchmark 電路中 8 個不同粒度的標準電路進行冗余設計,以分析不同粒度模塊的故障自修復時間。

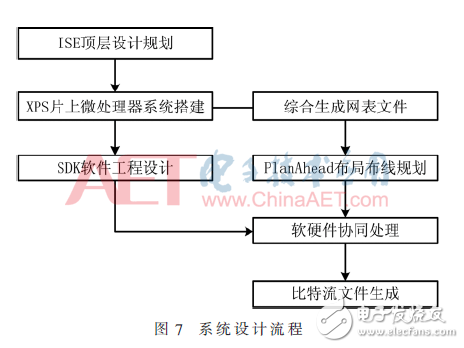

4.1 FPGA 系統設計流程

實驗中對系統進行設計實現采用的是基于 Xilinx ISE 開發工具的設計流程,設計流程如圖 7 所示。在 ISE 頂層設計規劃中對系統各模塊進行劃分,定義系統中的各靜態模塊和動態模塊,并對動態模塊進行冗余保護設計。片上微處理器系統在 Xilinx 的 XPS 設計工具中進行設計搭建,并在 SDK 設計工具中對微處理器系統進行軟件功能編譯,PlanAhead 設計工具可通過圖形界面(GUI)對 FPGA 進行早期分析和布局規劃功能,施加物理約束,分析布線和時序的結果。實驗中各動態模塊的區域劃分在 PlanAhead 中進行設計。PlanAhead 中比特流文件生成完成后,需要進行軟硬件協同處理,即將 XPS 生成的塊存儲器映射文件(*.bmm)、SDK 生成的可執行文件(*.elf)和 PlanAhead 生成的全局比特流文件合為一個新的比特流文件,借助 Xilinx 命令行工具 ISE Design Suite Command Prompt,通過命令指令合成最終的比特流文件。

4.2 實驗結果分析

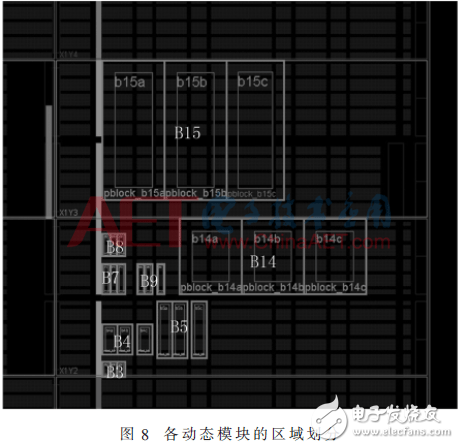

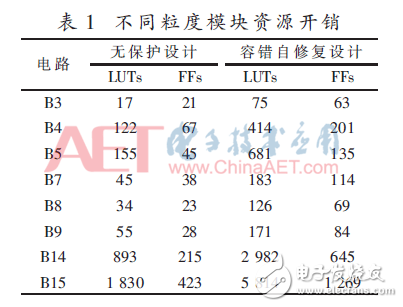

實驗中各動態模塊的區域劃分如圖 8 所示,動態區域內的邏輯資源能夠滿足各模塊功能實現。各動態模塊的資源開銷如表 1 所示,由實驗結果可知,模塊粒度越小其冗余設計中表決器和故障檢測結構所占的資源比例則越大,即系統模塊粒度劃分越小、重構區域劃分越多,則容錯自修復設計所帶來的額外資源開銷越大。

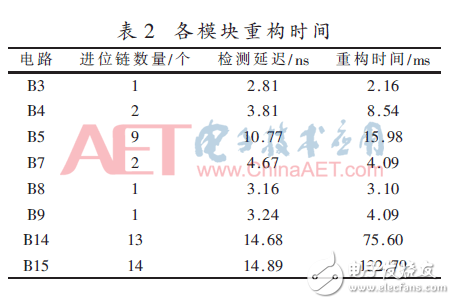

各動態模塊重構時間花費表 2 所示。實驗中所采取的故障注入方式同樣采取動態重構方式,即通過 FPGA 的內部配置訪問通道(ICAP)動態地對各模塊進行錯誤配置來實現。實驗中故障檢測方案采用上文所提出的內嵌式故障檢測結構,其故障檢測延遲與信號在進位鏈中的傳播延遲相關,即和進位鏈的串聯個數相關,而進位鏈中信號傳播延遲為納秒級,遠小于模塊重構時間,可認為模塊的自修復時間近似于模塊的重構時間。由實驗結果可看出模塊重構時間與模塊占用資源數和模塊重構區域大小成正比,即模塊占用資源數越多,其劃分的最小重構區域則越大,模塊重構時間花費越大。而同時,功能模塊劃分越小,其進行冗余設計時所帶來的額外資源開銷比例則越大。故在系統設計時,需要綜合考慮資源分配情況和故障修復時間要求,合理地進行模塊粒度劃分,實現粗粒度和細粒度的靈活組合。

5 結論

本文提出了一種基于 SRAM 型 FPGA 的實時容錯自修復系統結構和設計方法。該設計方法將系統分為若干功能模塊,采用粗粒度三模冗余結構和細粒度三模冗余結構并結合動態重構對系統進行容錯自修復設計,實驗結果表明該設計結構下故障修復時間短,系統的可靠性得到有效提高。在系統設計時,可以綜合考慮資源分配情況和故障修復時間要求,合理進行模塊粒度劃分,實現粗粒度和細粒度的靈活組合。

電子發燒友App

電子發燒友App

評論