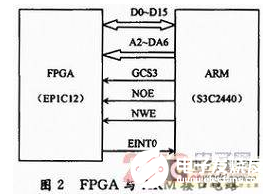

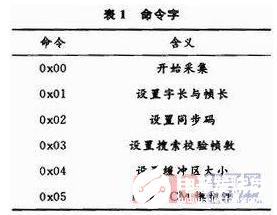

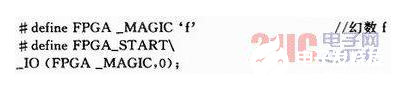

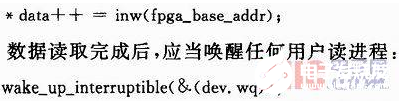

由于FPGA技術(shù)和ARM技術(shù)應(yīng)用越來(lái)越廣泛,通過(guò)設(shè)計(jì)并行總線接口來(lái)實(shí)現(xiàn)兩者之間的數(shù)據(jù)交換,可以較容易地解決快速傳輸數(shù)據(jù)的需求,因此設(shè)計(jì)滿足系統(tǒng)要求的FPGA并行總線顯得尤為重要。本文設(shè)計(jì)的FPGA的ARM外部并行總線接口,滿足了總線的時(shí)序要求,并在某航空機(jī)載雷達(dá)應(yīng)答機(jī)中進(jìn)行了應(yīng)用.

2013-08-15 10:44:19 7204

7204

基于ARM芯片和FPGA的特點(diǎn),設(shè)計(jì)了一種ARM與FPGA人工神經(jīng)網(wǎng)本文首先介紹了人工神經(jīng)網(wǎng)絡(luò)的模型和算法以及FPGA的實(shí)現(xiàn),并通過(guò)對(duì)網(wǎng)絡(luò)結(jié)構(gòu)的分析設(shè)計(jì)了FPGA端的數(shù)據(jù)存儲(chǔ)系統(tǒng)。然后分析了ARM端和FPGA端各自的功能,在此基礎(chǔ)上把兩者結(jié)合在一起,設(shè)計(jì)了一種利用ARM的ZDMA方式相互通信的方案。

2015-08-10 10:54:51 1676

1676

FPGA的嵌入式應(yīng)用。某人工神經(jīng)網(wǎng)絡(luò)的FPGA處理器能夠?qū)?b class="flag-6" style="color: red">數(shù)據(jù)進(jìn)行運(yùn)算處理,為了實(shí)現(xiàn)集數(shù)據(jù)通信、操作控制和數(shù)據(jù)處理于一體的便攜式神經(jīng)網(wǎng)絡(luò)處理器,需要設(shè)計(jì)一種基于嵌入式ARM內(nèi)核及現(xiàn)場(chǎng)可編程門(mén)陣列FPGA的主從結(jié)構(gòu)處理系統(tǒng)滿足要求。

2015-08-19 08:54:23 1936

1936

如圖1.9所示。這個(gè)流程圖是一個(gè)相對(duì)比較高等級(jí)的FPGA開(kāi)發(fā)流程,從項(xiàng)目的提上議程開(kāi)始,設(shè)計(jì)者需要進(jìn)行FPG

2017-10-24 10:43:09 7183

7183

FPGA的開(kāi)發(fā)流程是遵循著ASIC的開(kāi)發(fā)流程發(fā)展的,發(fā)展到目前為止,FPGA的開(kāi)發(fā)流程總體按照?qǐng)D1進(jìn)行,有些步驟可能由于其在當(dāng)前項(xiàng)目中的條件的寬度的允許,可以免去。

2023-01-06 11:19:28 1403

1403 FPGA設(shè)計(jì)流程是利用EDA開(kāi)發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開(kāi)發(fā)的過(guò)程。FPGA的設(shè)計(jì)流程如上圖所示:包括設(shè)計(jì)定義、代碼實(shí)現(xiàn)、功能仿真、邏輯綜合、前仿真、布局布線、后仿真和板級(jí)調(diào)試等步驟!

2023-04-04 10:29:51 1281

1281 。FPGA是由存放在片內(nèi)RAM中的程序來(lái)設(shè)置其工作狀態(tài)的,因此工作時(shí)需要對(duì)片內(nèi)的RAM 進(jìn)行編程。用戶可以根據(jù)不同的配置模式,采用不同的編程方式。加電時(shí),FPGA芯片將EPROM中數(shù)據(jù)讀入片內(nèi)編程RAM中

2014-06-26 14:23:43

進(jìn)行加密解 密、調(diào)制解調(diào)等,優(yōu)勢(shì)是強(qiáng)大的數(shù)據(jù)處理能力和較高的運(yùn)行速度。FPGA可以用VHDL或verilogHDL來(lái)編程,靈活性強(qiáng),由于能夠進(jìn)行編程、除錯(cuò)、 再編程和重復(fù)操作,因此可以充分地進(jìn)行

2013-05-06 15:56:02

驗(yàn)證無(wú)誤,則可以生產(chǎn)下載配置文件燒錄的實(shí)際器件中進(jìn)行板級(jí)的調(diào)試工作。圖5.15 FPGA/CPLD開(kāi)發(fā)流程當(dāng)然了,對(duì)于沒(méi)有實(shí)際工程經(jīng)驗(yàn)的初學(xué)者而言,這個(gè)流程圖可能不是那么容易理解。不過(guò)沒(méi)有關(guān)系,我們會(huì)

2019-01-28 02:29:05

FPGA的設(shè)計(jì)流程就是利用EDA開(kāi)發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開(kāi)發(fā)的過(guò)程。FPGA的開(kāi)發(fā)流程一般如圖1-10所示,包括電路功能設(shè)計(jì)、設(shè)計(jì)輸入、功能仿真、綜合優(yōu)化、綜合后仿真、實(shí)現(xiàn)、布線后仿真

2021-07-23 09:12:07

FPGA如何通過(guò)SPI向ARM上傳數(shù)據(jù)?而且是依次上傳六個(gè)電機(jī)的數(shù)據(jù)

2014-05-26 20:53:01

如圖1.6所示。這個(gè)流程圖是一個(gè)相對(duì)比較高等級(jí)的FPGA開(kāi)發(fā)流程,從項(xiàng)目的提上議程開(kāi)始,設(shè)計(jì)者需要進(jìn)行FPGA功能的需求分析,然后進(jìn)行模塊的劃分,比較復(fù)雜和龐大的設(shè)計(jì),則會(huì)通過(guò)模塊劃分把工作交給一個(gè)

2019-01-28 04:24:37

第二章 FPGA 開(kāi)發(fā)流程FPGA 的設(shè)計(jì)流程就是利用 EDA 開(kāi)發(fā)軟件和編程工具對(duì) FPGA 芯片進(jìn)行開(kāi)發(fā)的過(guò)程。原理圖和HDL(Hardware description language,硬件

2022-02-23 06:23:33

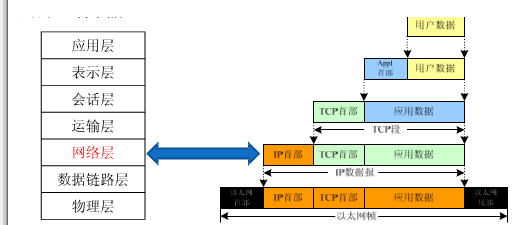

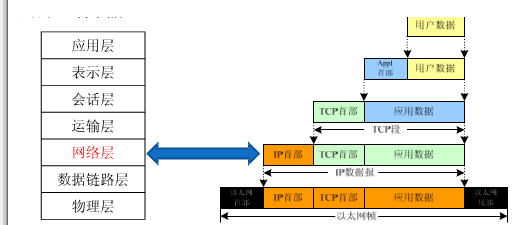

網(wǎng)絡(luò)子系統(tǒng)在鏈路層的收發(fā)過(guò)程剖析

2012-08-15 17:58:34

針對(duì)目前海事應(yīng)用中液位遙測(cè)系統(tǒng)的現(xiàn)狀,基于ARM9芯片的WinCE嵌入式開(kāi)發(fā)平臺(tái),開(kāi)發(fā)一套智能的液位遙測(cè)系統(tǒng)。該系統(tǒng)采用CAN總線,遵循CANopen協(xié)議,在EVC開(kāi)發(fā)環(huán)境下結(jié)合多線程技術(shù)和數(shù)據(jù)

2019-10-11 06:08:34

個(gè)指定網(wǎng)絡(luò)實(shí)例。NetManagersetupSpecificNet(NetSpecifier netSpecifier, NetStatusCallback callback)建立指定的數(shù)據(jù)網(wǎng)絡(luò)

2021-09-14 11:33:42

和其他設(shè)備互聯(lián)互通。HarmonyOS網(wǎng)絡(luò)管理模塊主要提供以下功能:數(shù)據(jù)連接管理:網(wǎng)卡綁定,打開(kāi)URL,數(shù)據(jù)鏈路參數(shù)查詢。數(shù)據(jù)網(wǎng)絡(luò)管理:指定數(shù)據(jù)網(wǎng)絡(luò)傳輸,獲取數(shù)據(jù)網(wǎng)絡(luò)狀態(tài)變更,數(shù)據(jù)網(wǎng)絡(luò)狀態(tài)查詢。流量統(tǒng)計(jì)

2020-09-21 14:19:40

SRv6是什么意思?SRv6是由哪幾部分組成的?SRv6的轉(zhuǎn)發(fā)流程是怎樣進(jìn)行的?

2021-10-19 08:46:50

SRv6的基本概念是什么?SRv6是由哪些部分組成的?SRv6的轉(zhuǎn)發(fā)流程是怎樣的?

2021-10-26 07:42:47

全國(guó)最詳細(xì)的數(shù)據(jù)通信行業(yè)資料查看復(fù)制粘貼地址:http://www.raysuo.com/company/company_list.jsp?keywords=數(shù)據(jù)通信全國(guó)最詳細(xì)的數(shù)據(jù)網(wǎng)絡(luò)行業(yè)資料查看

2009-06-03 10:20:27

主動(dòng)網(wǎng)絡(luò)的基本思想是將程序注入數(shù)據(jù)包,使程序和數(shù)據(jù)一起隨數(shù)據(jù)包在網(wǎng)絡(luò)上傳輸;網(wǎng)絡(luò)的中間節(jié)點(diǎn)運(yùn)行數(shù)據(jù)包中的程序,利用中間節(jié)點(diǎn)的計(jì)算能力,對(duì)數(shù)據(jù)包中的數(shù)據(jù)進(jìn)行一定的處理;從而將傳統(tǒng)網(wǎng)絡(luò)中“存儲(chǔ)——轉(zhuǎn)發(fā)”的處理模式改變?yōu)椤按鎯?chǔ)——計(jì)算——轉(zhuǎn)發(fā)”的處理模式。

2019-09-20 09:00:51

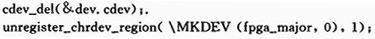

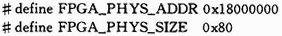

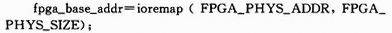

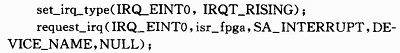

在數(shù)字系統(tǒng)的設(shè)計(jì)中,FPGA+ARM 的系統(tǒng)架構(gòu)得到了越來(lái)越廣泛的應(yīng)用,FPGA 主要實(shí)現(xiàn)高速數(shù)據(jù)的處理;ARM 主要實(shí)現(xiàn)系統(tǒng)的流程控制.人機(jī)交互.外部通信以及FPGA 控制等功能.I2C.SPI

2019-09-17 06:21:10

1、 應(yīng)用背景 市面上的FPGA開(kāi)發(fā)板和ARM開(kāi)發(fā)板很多,但是將兩者結(jié)合起來(lái)完成數(shù)據(jù)采集與網(wǎng)絡(luò)通訊的開(kāi)發(fā)板很少

2010-08-31 09:14:55

況進(jìn)行速率匹配。4 結(jié)語(yǔ) 本文介紹了基于ARM和FPGA的環(huán)形緩沖區(qū)的設(shè)計(jì)方法,實(shí)現(xiàn)簡(jiǎn)單并便于擴(kuò)展。測(cè)試結(jié)果表明此方法能實(shí)現(xiàn)ARM和FPGA之間數(shù)據(jù)的有效傳輸。對(duì)網(wǎng)絡(luò)協(xié)議的實(shí)現(xiàn)具有重要的參考價(jià)值。

2019-05-30 05:00:03

以太網(wǎng)接口通信速度快,傳輸可靠,使用和配置方便,對(duì)于20 Mb/s以下的碼速率,100 Mb/s的網(wǎng)卡可以進(jìn)行不丟包轉(zhuǎn)發(fā),采用TCP包格式還可使設(shè)備小型化,便于數(shù)據(jù)的轉(zhuǎn)發(fā),因此有必要擴(kuò)展設(shè)備的以太網(wǎng)功能。

2020-03-24 07:16:52

航空電子全雙工交換以太網(wǎng)(AFDX)是下一代航空數(shù)據(jù)網(wǎng)絡(luò)的最佳選擇,AFDX端系統(tǒng)保證了AFDX網(wǎng)絡(luò)航電系統(tǒng)之間數(shù)據(jù)交換的安全和可靠性;為了研制具有我國(guó)自主產(chǎn)權(quán)的新型機(jī)載數(shù)據(jù)網(wǎng)絡(luò)端系統(tǒng)協(xié)議芯片

2010-05-13 09:09:08

前言由于本人第一次嘗試開(kāi)發(fā)單片機(jī),要實(shí)現(xiàn)的功能是信息轉(zhuǎn)發(fā),需要調(diào)用HAL庫(kù)方法,中斷接受信息轉(zhuǎn)發(fā)給FPGA,這里沒(méi)有用到DMA方式所以不做贅述,特此記錄分享希望幫到你們。發(fā)送信息和中斷接受流程發(fā)送

2021-11-22 07:20:41

某人工神經(jīng)網(wǎng)絡(luò)的FPGA處理器能夠?qū)?b class="flag-6" style="color: red">數(shù)據(jù)進(jìn)行運(yùn)算處理,為了實(shí)現(xiàn)集數(shù)據(jù)通信、操作控制和數(shù)據(jù)處理于一體的便攜式神經(jīng)網(wǎng)絡(luò)處理器,需要設(shè)計(jì)一種基于嵌入式ARM內(nèi)核及現(xiàn)場(chǎng)可編程門(mén)陣列FPGA的主從結(jié)構(gòu)處理系統(tǒng)滿足要求。

2021-05-21 06:35:27

FPGA的嵌入式應(yīng)用。某人工神經(jīng)網(wǎng)絡(luò)的FPGA處理器能夠?qū)?b class="flag-6" style="color: red">數(shù)據(jù)進(jìn)行運(yùn)算處理,為了實(shí)現(xiàn)集數(shù)據(jù)通信、操作控制和數(shù)據(jù)處理于一體的便攜式神經(jīng)網(wǎng)絡(luò)處理器,需要設(shè)計(jì)一種基于嵌入式ARM內(nèi)核及現(xiàn)場(chǎng)可編程門(mén)陣列FPGA的主從結(jié)構(gòu)處理系統(tǒng)滿足要求。

2019-09-20 06:15:20

整車(chē)VCU技術(shù)和開(kāi)發(fā)流程剖析VCU作為車(chē)輛的核心,控制和監(jiān)測(cè)著車(chē)輛的每一個(gè)動(dòng)作。車(chē)輛的控制過(guò)程,就是針對(duì)不同的運(yùn)行模式,對(duì)關(guān)切的幾個(gè)參數(shù)進(jìn)行比較。參數(shù)屬于哪個(gè)范圍,汽車(chē)就執(zhí)行怎樣的運(yùn)行模式。車(chē)輛工作

2021-08-27 08:01:34

智能駕駛數(shù)據(jù)網(wǎng)絡(luò)時(shí)間同步(PTP時(shí)鐘服務(wù)器)分析隨著汽車(chē)電子的日益復(fù)雜化以及汽車(chē)電子電氣架構(gòu)(EEA)的升級(jí),人們對(duì)于聯(lián)網(wǎng)智能汽車(chē)的需求也在逐步上升,大量先進(jìn)技術(shù)往汽車(chē)上應(yīng)用,如高級(jí)駕駛輔助系統(tǒng)

2021-09-03 07:34:48

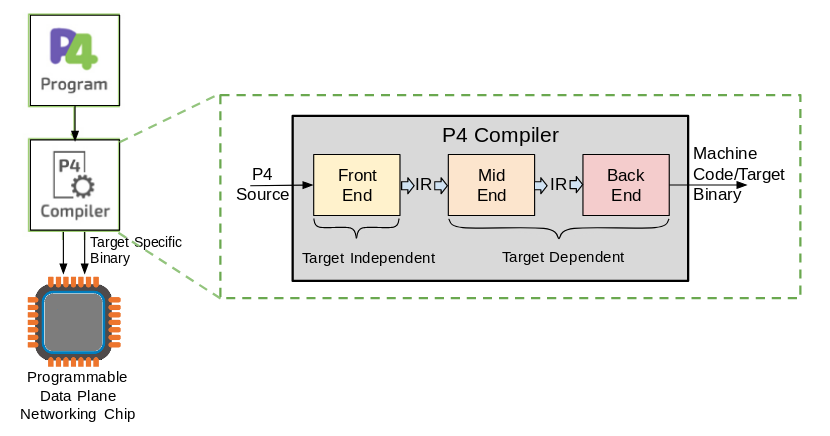

,讓硬件來(lái)執(zhí)行計(jì)算(加速的概念),今天就介紹兩個(gè)針對(duì)以上解決方案的開(kāi)源項(xiàng)目,這兩個(gè)項(xiàng)目是用FPGA進(jìn)行硬件加速的必備項(xiàng)目。 AI算法流程 在進(jìn)行項(xiàng)目介紹前,我們先介紹一下軟件架構(gòu)和工具集。這個(gè)后面會(huì)影響理解。 一個(gè)完整的深度學(xué)習(xí)框架中主要分為下面幾個(gè)流程:原作者:碎碎思·

2022-10-24 16:10:50

本帖最后由 fantek 于 2013-12-26 12:56 編輯

根據(jù)網(wǎng)上資料設(shè)計(jì)了一個(gè)股票行情實(shí)時(shí)數(shù)據(jù)采集小程序。程序主要實(shí)現(xiàn)了行情數(shù)據(jù)網(wǎng)絡(luò)采集接口、K線圖GIF文件讀取和顯示。如果大家

2013-12-26 12:49:22

AFE數(shù)據(jù)并控制衛(wèi)星中的遙測(cè)電路,可使用兩種器件:FPGA或微控制器(MCU)。典型的遙測(cè)電路使用FPGA來(lái)實(shí)現(xiàn)遙測(cè)數(shù)據(jù)的通信和處理,幾乎可以獨(dú)立運(yùn)行,而且不需要與系統(tǒng)的其他器件進(jìn)行通信。FPGA支持

2022-11-03 07:56:26

本帖最后由 一只耳朵怪 于 2018-6-4 09:11 編輯

您好,我目前想在網(wǎng)絡(luò)中加入路由器且需要了解路由器轉(zhuǎn)發(fā)訊息時(shí)詳細(xì)情況(為了能使用戶知道主機(jī)端收到的訊息是否有通過(guò)路由器),可否告知我是由何處的function進(jìn)行此項(xiàng)工作? P.S. 轉(zhuǎn)發(fā)的訊息為已配對(duì)之單播訊息

2018-06-01 02:02:51

請(qǐng)問(wèn)一下,stm32 407 能不能實(shí)現(xiàn)即作為網(wǎng)絡(luò)服務(wù)器又作為客戶端,來(lái)實(shí)現(xiàn)數(shù)據(jù)的轉(zhuǎn)發(fā)呢,在裸機(jī)的情況下,用Lwip

2020-03-13 01:10:36

你好, 我正在使用zc702 FPGA板。我想使用SPI在ARM和FPGA之間進(jìn)行通信。請(qǐng)問(wèn)有誰(shuí)幫我怎么做?

2020-04-27 06:03:35

分析并比較對(duì)稱加密算法DES, AES和非對(duì)稱加密算法RSA,結(jié)合地圖數(shù)據(jù)網(wǎng)絡(luò)分發(fā)的實(shí)際應(yīng)用,提出散列組合加密算法。該算法具有AES算法的高效性和RSA算法便于進(jìn)行密鑰管理的特點(diǎn),將

2009-04-16 09:48:46 32

32 LX914是LEVELONE公司生產(chǎn)的一種為混合媒體網(wǎng)絡(luò)設(shè)計(jì)的多端口集成轉(zhuǎn)發(fā)器,可用于在數(shù)據(jù)采集點(diǎn)和處理中心之間進(jìn)行接力轉(zhuǎn)發(fā).文中介紹LX914的結(jié)構(gòu)和引腳功能,并著重介紹一種設(shè)計(jì)靈活、

2009-04-24 14:01:48 18

18 LINUX UI界面;對(duì)標(biāo)ZYNQ 7010的FPGA資源,滿足高速數(shù)據(jù)采集需求;ARM與FPGA之間采用PCIE高速通信,支持200~300MB/S的通信能力;工業(yè)級(jí)-

2022-11-04 16:12:46

數(shù)據(jù)網(wǎng)絡(luò)基本原理:關(guān)鍵詞: 以太網(wǎng), TCP / IP, 數(shù)據(jù)網(wǎng)絡(luò)摘要:本教材主要介紹華為公司的數(shù)據(jù)通信原理和廣域網(wǎng)協(xié)議原理.

1 課程說(shuō)明.. 51.1 課程介紹.. 51.2 課程目標(biāo).. 5

2009-06-09 23:11:07 31

31 針對(duì)電力系統(tǒng)引進(jìn)的安全工具不能根據(jù)系統(tǒng)安全狀況靈活調(diào)整安全配置,系統(tǒng)各部間也不進(jìn)行通信協(xié)調(diào)工作的問(wèn)題,設(shè)計(jì)了基于簡(jiǎn)單網(wǎng)絡(luò)管理協(xié)議(89:()的電力數(shù)據(jù)網(wǎng)絡(luò)柔性安全體

2009-06-22 13:20:00 23

23 本文主要論述在設(shè)計(jì)某主板測(cè)試系統(tǒng)數(shù)據(jù)緩存和轉(zhuǎn)發(fā)過(guò)程中所遇到的問(wèn)題以及相應(yīng)的解決的方法。提出了分割較大的狀態(tài)機(jī)為若干個(gè)相對(duì)較小狀態(tài)機(jī)的方法,以簡(jiǎn)化狀態(tài)機(jī)個(gè)數(shù),使得狀

2010-07-17 17:53:01 25

25 摘要:目前,我國(guó)大部分地區(qū)的高速公路收費(fèi)系統(tǒng),乃至大中型企事業(yè)。都建立了局域網(wǎng)或者廣域網(wǎng)。在現(xiàn)有的高速公路聯(lián)網(wǎng)收費(fèi)數(shù)據(jù)網(wǎng)絡(luò)基礎(chǔ)上,利用Windows套接字和可視化編程技

2010-07-25 22:25:30 25

25 針對(duì)電子政務(wù)中大量業(yè)務(wù)數(shù)據(jù)網(wǎng)絡(luò)傳輸問(wèn)題,提出一種新的數(shù)據(jù)傳輸網(wǎng)絡(luò)架構(gòu),研究了即時(shí)數(shù)據(jù)傳輸與離線數(shù)據(jù)傳輸,設(shè)計(jì)和實(shí)現(xiàn)了數(shù)據(jù)傳輸組件原型系統(tǒng),實(shí)現(xiàn)了點(diǎn)對(duì)點(diǎn)數(shù)據(jù)傳

2010-12-01 17:25:50 21

21 什么是電纜(CATV)數(shù)據(jù)網(wǎng)絡(luò)

在有些國(guó)家,有線電視行業(yè)已經(jīng)成為通過(guò)升級(jí)的CATV(有線電視)網(wǎng)絡(luò)進(jìn)行數(shù)據(jù)傳送的主要服務(wù)提供商。有線電視行業(yè)有許多向

2010-04-06 11:38:01 2637

2637 網(wǎng)絡(luò)化配電載波通信(Network of Distribution Line Carrier)是配電網(wǎng)通信中的一種新形式,數(shù)據(jù)轉(zhuǎn)發(fā)是實(shí)現(xiàn)其中的核心內(nèi)容。本文探討了一種用軟件實(shí)現(xiàn)的數(shù)據(jù)轉(zhuǎn)發(fā)方案,并且給出了NDLC通信的數(shù)

2011-06-18 18:13:15 21

21 由于Ad Hoc網(wǎng)絡(luò)無(wú)中心、動(dòng)態(tài)拓?fù)涞忍攸c(diǎn),它需要各個(gè)節(jié)點(diǎn)都具有路由轉(zhuǎn)發(fā)功能。本文開(kāi)發(fā)的Ad Hoc網(wǎng)絡(luò)節(jié)點(diǎn)通過(guò)在ARM平臺(tái)上移植路由協(xié)議而實(shí)現(xiàn)了數(shù)據(jù)包轉(zhuǎn)發(fā)功能。

2011-08-25 11:27:55 1859

1859

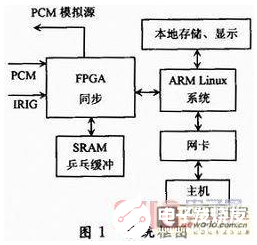

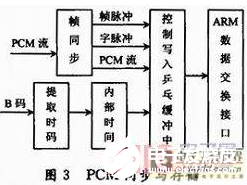

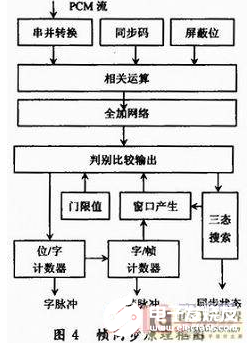

基于FPGA與ARM進(jìn)行遙測(cè)數(shù)據(jù)的幀同步遙測(cè)數(shù)據(jù)的網(wǎng)絡(luò)轉(zhuǎn)發(fā),充分地利用了FPGA與ARM各自的特點(diǎn),它可使FPGA+ARM在數(shù)據(jù)接收處理中得到廣泛應(yīng)用。

2011-11-15 14:57:26 1253

1253

EXFO Inc和RAD數(shù)據(jù)通信公司今天宣布推出一種新的集成解決方案,用于數(shù)據(jù)網(wǎng)絡(luò)的端到端監(jiān)測(cè)。該解決方案可將顯著縮短網(wǎng)絡(luò)部署時(shí)間——從數(shù)月縮短至數(shù)周乃至數(shù)日,從而降低運(yùn)營(yíng)商的資

2012-05-29 17:06:25 1022

1022 設(shè)計(jì)了一種新型的水情遙測(cè)終端,該終端能夠?qū)崟r(shí)采集雨量、水位、流量、溫度等多種水情數(shù)據(jù),對(duì)采集到的數(shù)據(jù)可以進(jìn)行顯示。同時(shí)能通過(guò)CDMA網(wǎng)絡(luò)或者備用的超短波網(wǎng)絡(luò)及時(shí)將數(shù)據(jù)上

2013-01-29 14:14:49 34

34 FPGA設(shè)計(jì)的流程,步驟,選型,仿真,軟硬件設(shè)計(jì),調(diào)試流程。

2016-05-11 14:33:02 29

29 物理基礎(chǔ)設(shè)施數(shù)據(jù)網(wǎng)絡(luò)構(gòu)建策略白皮書(shū)

2017-01-22 13:38:08 8

8 博主Greg Ferro在其Ethereal Mind網(wǎng)頁(yè)上發(fā)布了一則關(guān)于 Corsa Technology簡(jiǎn)短博客信息,提到Corsa公司制作了一對(duì)基于FPGA開(kāi)放流程的SDN轉(zhuǎn)發(fā)引擎。Ferro同時(shí)簡(jiǎn)單討論了此引擎是否適用于WANs網(wǎng)絡(luò)。

2017-02-09 14:06:10 973

973 有限遙測(cè)速率下衛(wèi)星遙測(cè)數(shù)據(jù)設(shè)計(jì)方法研究_劉洋

2017-03-19 11:45:57 1

1 基于FPGA的多通道遙測(cè)采編器設(shè)計(jì)_袁強(qiáng)

2017-03-19 19:07:17 1

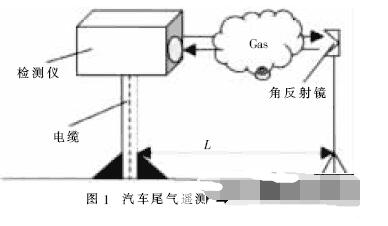

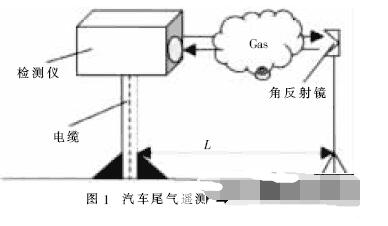

1 一種以ARM處理器為核心的汽車(chē)尾氣遙測(cè)儀的設(shè)計(jì)。對(duì)該遙測(cè)儀的工作原理、系統(tǒng)設(shè)計(jì)與嵌入式軟硬件實(shí)現(xiàn)作了較詳細(xì)的分析。實(shí)踐表明,該系統(tǒng)在性價(jià)比、響應(yīng)速度、可攜帶性及功耗等方面均有明顯優(yōu)勢(shì)。

2017-09-08 15:45:31 0

0 基于ARM處理器和FPGA在數(shù)據(jù)傳輸中的應(yīng)用與研究

2017-10-15 10:28:49 4

4 針對(duì)現(xiàn)有車(chē)聯(lián)網(wǎng)( VANET)中數(shù)據(jù)轉(zhuǎn)發(fā)效率低的問(wèn)題,提出了軟件定義網(wǎng)絡(luò)(SDN)的數(shù)據(jù)轉(zhuǎn)發(fā)機(jī)制。首先,設(shè)計(jì)了軟件定義車(chē)聯(lián)網(wǎng)的分層次網(wǎng)絡(luò)模型,該模型由局部控制器和車(chē)輛組成,實(shí)現(xiàn)控制與數(shù)據(jù)轉(zhuǎn)發(fā)分離

2017-12-07 15:06:12 0

0 車(chē)載自組織網(wǎng)絡(luò)( VANET)是一個(gè)高度動(dòng)態(tài)的通信網(wǎng)絡(luò),設(shè)計(jì)穩(wěn)定的數(shù)據(jù)分發(fā)機(jī)制是一個(gè)很大的挑戰(zhàn)。將關(guān)注數(shù)據(jù)內(nèi)容的命名數(shù)據(jù)網(wǎng)絡(luò)(NDN)應(yīng)用于車(chē)載自組織網(wǎng)絡(luò)中,能有效緩解網(wǎng)絡(luò)拓?fù)漕l繁變化所帶來(lái)

2017-12-07 16:19:22 0

0 物聯(lián)網(wǎng)子范疇的傳統(tǒng)無(wú)線傳感器網(wǎng)絡(luò)數(shù)據(jù)轉(zhuǎn)發(fā)模型已經(jīng)不能完全適應(yīng)這種時(shí)代需求,更加適合物聯(lián)網(wǎng)應(yīng)用的數(shù)據(jù)轉(zhuǎn)發(fā)模型成為物聯(lián)網(wǎng)連續(xù)性服務(wù)保障的基礎(chǔ)性問(wèn)題及研究熱點(diǎn)。本文首先對(duì)物聯(lián)網(wǎng)架構(gòu)及其應(yīng)用環(huán)境下的數(shù)據(jù)轉(zhuǎn)發(fā)關(guān)鍵問(wèn)題進(jìn)行

2017-12-19 16:09:51 1

1 針對(duì)雙向中繼網(wǎng)絡(luò)中傳統(tǒng)中繼轉(zhuǎn)發(fā)協(xié)議放大信號(hào)的同時(shí)放大了噪聲、可能轉(zhuǎn)發(fā)錯(cuò)誤的解碼信號(hào)、中繼判決結(jié)果不可靠等問(wèn)題,提出兩種基于互信息轉(zhuǎn)發(fā)(MIF)的網(wǎng)絡(luò)編碼中繼轉(zhuǎn)發(fā)方案。首先,中繼節(jié)點(diǎn)轉(zhuǎn)發(fā)來(lái)自兩個(gè)

2017-12-25 10:40:04 0

0 探究微博轉(zhuǎn)發(fā)網(wǎng)絡(luò)的構(gòu)建機(jī)制有助于深刻理解信息在微博平臺(tái)上的傳播過(guò)程,得出針對(duì)微博營(yíng)銷(xiāo)、輿論管控的有效策略和建議。針對(duì)這一問(wèn)題,提出了一種有向加權(quán)網(wǎng)絡(luò)模型。根據(jù)微博在轉(zhuǎn)發(fā)過(guò)程中被多次轉(zhuǎn)發(fā)的現(xiàn)象,在模型

2018-01-14 14:52:26 0

0 不斷 從賽靈思FPGA設(shè)計(jì)流程看懂FPGA設(shè)計(jì) 1.XILINX ISE傳統(tǒng)FPGA設(shè)計(jì)流程 利用XilinxISE軟件開(kāi)發(fā)FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合

2018-02-20 20:32:00 15820

15820

三層轉(zhuǎn)發(fā)就是通過(guò)路由器的在不同時(shí)間的轉(zhuǎn)發(fā)。它一般工作在TCP/IP網(wǎng)絡(luò)模型的第三層。 三層轉(zhuǎn)發(fā)可以很復(fù)雜,也可以很簡(jiǎn)單。今天我們就來(lái)講講網(wǎng)絡(luò)層的定義和 三層轉(zhuǎn)發(fā)的基本原理。

2018-02-23 12:44:00 22234

22234

遙測(cè)數(shù)據(jù)傳輸在飛行試驗(yàn)中發(fā)揮著重要的作用,連接著機(jī)載測(cè)試系統(tǒng)和地面監(jiān)控網(wǎng)絡(luò)。由于現(xiàn)行的遙測(cè)系統(tǒng)采用點(diǎn)對(duì)點(diǎn)單向傳輸?shù)哪J剑皶r(shí)關(guān)鍵測(cè)試數(shù)據(jù)出錯(cuò)也無(wú)法實(shí)現(xiàn)實(shí)時(shí)重傳,因此在風(fēng)險(xiǎn)科目的試飛中或需要跨空域試飛

2018-02-12 14:52:25 2

2 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的設(shè)計(jì)流程是怎么樣的?FPGA設(shè)計(jì)流程指南詳細(xì)資料免費(fèi)下載內(nèi)容包括了:1.基于HDL 的FPGA 設(shè)計(jì)流程概述2.Verilog HDL 設(shè)計(jì)3. 邏輯仿真4. 邏輯綜合

2018-10-17 17:50:41 29

29 本文提出了一種實(shí)現(xiàn)信號(hào)采集方案,介紹了由ARM 處理器S3C2410 和EP2C8 FPGA 組成的高速信號(hào)采集系統(tǒng)的系統(tǒng)設(shè)計(jì),并著重介紹前端硬件的設(shè)計(jì),并就ARM 處理器和FPGA 的互聯(lián)設(shè)計(jì)進(jìn)行探討。利用FPGA 硬件控制A/D 轉(zhuǎn)換,達(dá)到了較好的效果,實(shí)現(xiàn)了信號(hào)的采集與存儲(chǔ)。

2018-11-02 15:46:01 10

10 DxChain是一個(gè)致力于區(qū)塊鏈存儲(chǔ)和計(jì)算的大數(shù)據(jù)網(wǎng)絡(luò),按照DxChain的開(kāi)發(fā)路線,先開(kāi)發(fā)存儲(chǔ)功能,再開(kāi)發(fā)計(jì)算部分。在我們7月份發(fā)布了存儲(chǔ)功能的MVP之后,依據(jù)DxChain之前所計(jì)劃,在第三季度底發(fā)布測(cè)試鏈的Beta版本Andes,現(xiàn)在DxChain嚴(yán)格按照時(shí)間表交付了產(chǎn)品。

2018-12-14 09:46:53 1143

1143 一種以ARM處理器為核心的汽車(chē)尾氣遙測(cè)儀的設(shè)計(jì)。對(duì)該遙測(cè)儀的工作原理、系統(tǒng)設(shè)計(jì)與嵌入式軟硬件實(shí)現(xiàn)作了較詳細(xì)的分析。實(shí)踐表明,該系統(tǒng)在性價(jià)比、響應(yīng)速度、可攜帶性及功耗等方面均有明顯優(yōu)勢(shì)。

2019-01-01 13:08:00 1243

1243

緩存狀態(tài)的維護(hù);同時(shí)擴(kuò)展了協(xié)議無(wú)感知轉(zhuǎn)發(fā)指令,該指令直接查詢BF,依據(jù)所查詢結(jié)果,采用優(yōu)化的轉(zhuǎn)發(fā)流程轉(zhuǎn)發(fā)數(shù)據(jù)包,實(shí)現(xiàn)依據(jù)周邊緩存狀態(tài)的快速轉(zhuǎn)發(fā)。實(shí)驗(yàn)結(jié)果表明:依據(jù)控制器所維護(hù)狀態(tài)進(jìn)行轉(zhuǎn)發(fā)在輸入速率為80Kb/s即達(dá)到性能

2019-01-18 11:20:41 3

3 全世界正在快速進(jìn)入萬(wàn)物感知、萬(wàn)物智能、萬(wàn)物互聯(lián)的數(shù)字化智能社會(huì)形態(tài),數(shù)據(jù)網(wǎng)絡(luò)的服務(wù)邊界從互聯(lián)網(wǎng)業(yè)務(wù)逐漸擴(kuò)張到農(nóng)業(yè)生產(chǎn)、工業(yè)制造和交通運(yùn)輸?shù)葌鹘y(tǒng)行業(yè)。ITU-T Network 2030 Focus

2019-02-12 10:14:21 1900

1900 無(wú)人機(jī)機(jī)載數(shù)據(jù)鏈設(shè)備的系統(tǒng)架構(gòu)如圖1 所示。首先,FPGA 通過(guò)EMIF 接收DSP 的高清壓縮視頻、通過(guò)UART 接收飛控計(jì)算機(jī)的遙測(cè)數(shù)據(jù),壓縮后的視頻數(shù)據(jù)和遙測(cè)數(shù)據(jù)在FPGA 組幀編碼調(diào)制后通過(guò)LVDS 發(fā)送到AD9361,AD9361 對(duì)數(shù)據(jù)進(jìn)行上變頻后經(jīng)由天線發(fā)射出去;

2019-04-17 15:32:33 17026

17026 在數(shù)字系統(tǒng)的設(shè)計(jì)中,FPGA+ARM 的系統(tǒng)架構(gòu)得到了越來(lái)越廣泛的應(yīng)用,FPGA主要實(shí)現(xiàn)高速數(shù)據(jù)的處理;ARM 主要實(shí)現(xiàn)系統(tǒng)的流程控制.人機(jī)交互.外部通信以及FPGA 控制等功能.I2C.SPI

2019-08-08 15:37:50 5863

5863

FPGA的設(shè)計(jì)流程就是利用EDA開(kāi)發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開(kāi)發(fā)的過(guò)程。FPGA的開(kāi)發(fā)流程一般包括功能定義/器件選型、設(shè)計(jì)輸入、功能仿真、邏輯綜合、布局布線與實(shí)現(xiàn)、編程調(diào)試等主要步驟。

2019-11-06 15:17:28 2224

2224 FPGA的設(shè)計(jì)流程就是利用EDA開(kāi)發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開(kāi)發(fā)的過(guò)程。FPGA的開(kāi)發(fā)流程包括功能定義/器件選型、設(shè)計(jì)輸入、功能仿真、邏輯綜合、布局布線與實(shí)現(xiàn)、編程調(diào)試等主要步驟。

2019-11-20 15:06:28 1545

1545 最新才流行的嵌入式C程序。 FPGA的開(kāi)發(fā)流程即是利用EDA開(kāi)發(fā)軟件以及編程工具對(duì)FPGA芯片進(jìn)行開(kāi)發(fā)的過(guò)程。EDA ( Electronic Design Automation,電子設(shè)計(jì)自動(dòng)化

2020-11-12 18:22:28 5791

5791 延遲容忍網(wǎng)絡(luò)中的轉(zhuǎn)發(fā)機(jī)制因節(jié)點(diǎn)自私性行為會(huì)造成中繼節(jié)點(diǎn)拒絕轉(zhuǎn)發(fā),并導(dǎo)致消息投遞率降低、傳輸時(shí)延增長(zhǎng)等性能下降問(wèn)題。為此,基于節(jié)點(diǎn)行為分析,提出一種自私性延遲容忍網(wǎng)絡(luò)消息轉(zhuǎn)發(fā)機(jī)制。該機(jī)制以多副本傳輸

2021-03-26 11:56:41 23

23 實(shí)施導(dǎo)致的數(shù)據(jù)包被錯(cuò)誤轉(zhuǎn)發(fā)例如,SDN中轉(zhuǎn)發(fā)的數(shù)據(jù)包會(huì)被異常的規(guī)則或攻擊者丟棄、篡改或注入虛假數(shù)據(jù)包。此外,由于處于數(shù)據(jù)層的SDN交換機(jī)僅提供了簡(jiǎn)化的數(shù)據(jù)轉(zhuǎn)發(fā)功能,因此作者無(wú)法簡(jiǎn)單地部署傳統(tǒng)TP網(wǎng)絡(luò)中的數(shù)據(jù)轉(zhuǎn)發(fā)驗(yàn)證方案。因此,作者需要提出一個(gè)適用于SDN的有效數(shù)

2021-03-31 10:35:41 6

6 M7015核心板擁有ARM處理器的軟件可編程性與FPGA的硬件可編程性,不僅實(shí)現(xiàn)數(shù)據(jù)存儲(chǔ)分析、網(wǎng)絡(luò)通訊、多媒體顯示等功能,還支持數(shù)據(jù)并行采集,圖像高速采集,擴(kuò)展通訊接口等功能。 M7015核心板性能

2021-06-18 17:42:17 8569

8569 非連續(xù)數(shù)據(jù)網(wǎng)絡(luò)通信系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

2021-06-24 16:08:28 22

22 FPGA設(shè)計(jì)流程指南

2021-11-02 16:29:21 9

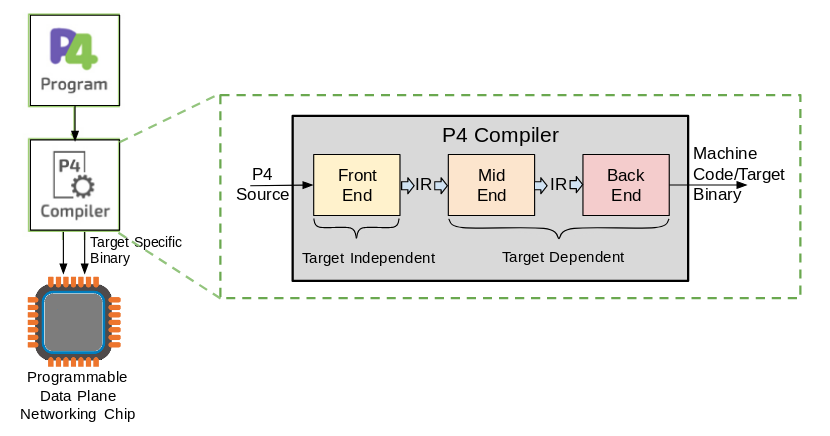

9 隨著物聯(lián)網(wǎng)設(shè)備的巨大增長(zhǎng)、數(shù)據(jù)流量的增加、新協(xié)議以及私有云和公共云的不斷增長(zhǎng),網(wǎng)絡(luò)世界的創(chuàng)新步伐正在加快。網(wǎng)絡(luò)的未來(lái)已經(jīng)超越了分離SDN的數(shù)據(jù)和控制平面,而是在ASIC深處對(duì)轉(zhuǎn)發(fā)邏輯進(jìn)行編程。

2022-12-08 16:41:41 1000

1000

1、 應(yīng)用背景 ? ? 市面上的FPGA開(kāi)發(fā)板和ARM開(kāi)發(fā)板很多,但是將兩者結(jié)合起來(lái)完成數(shù)據(jù)采集與網(wǎng)絡(luò)通訊的開(kāi)發(fā)板很少。大多數(shù)的勘探、觀測(cè)工作都是在嚴(yán)苛的環(huán)境中進(jìn)行的,對(duì)數(shù)據(jù)的準(zhǔn)確性、實(shí)時(shí)性都有

2023-02-10 17:50:01 1091

1091 ZYNQ擁有ARM+FPGA這個(gè)神奇的架構(gòu),那么ARM和FPGA究竟是如何進(jìn)行通信的呢?本章通過(guò)剖析AXI總線源碼,來(lái)一探其中的秘密。

2023-02-16 09:26:57 11450

11450 FPGA的設(shè)計(jì)流程主要包括HDL代碼編寫(xiě)、RTL綜合、布局布線、靜態(tài)時(shí)序分析、生成下載文件。下面將逐一介紹各部分。下面是FPGA設(shè)計(jì)的流程圖。

2023-07-04 12:06:08 795

795

??FPGA 的詳細(xì)開(kāi)發(fā)流程就是利用 EDA 開(kāi)發(fā)工具對(duì) FPGA 芯片進(jìn)行開(kāi)發(fā)的過(guò)程,所以 FPGA 芯片開(kāi)發(fā)流程講的并不是芯片的制造流程,區(qū)分于 IC 設(shè)計(jì)制造流程喲(芯片制造流程多麻煩,要好

2023-07-04 14:37:17 2387

2387

在數(shù)字化時(shí)代的推動(dòng)下,設(shè)備之間的數(shù)據(jù)互聯(lián)互通變得日益重要。對(duì)于工業(yè)生產(chǎn)而言,數(shù)據(jù)采集與轉(zhuǎn)發(fā)已經(jīng)成為了一個(gè)不可或缺的環(huán)節(jié)。傳統(tǒng)的數(shù)據(jù)采集方式往往只能將數(shù)據(jù)發(fā)送到一個(gè)特定的數(shù)據(jù)平臺(tái)進(jìn)行存儲(chǔ)和監(jiān)測(cè),而隨著

2023-09-04 15:40:15 348

348

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論