FPGA入門教程 FPGA 入門教程 1 .?dāng)?shù)字電路設(shè)計入門 2 .FPGA 簡介 3 .FPGA 開發(fā)流程 4 .RTL設(shè)計 5 .QuartusⅡ設(shè)計實例 6.ModelSim和Testbench

2012-08-11 11:40:44

完成了前面基本的設(shè)計輸入后,為了進(jìn)一步的驗證代碼所實現(xiàn)功能的正確性,我們還需要進(jìn)行仿真測試。關(guān)于仿真的一些深入的介紹大家可以參考筆者的《深入淺出玩轉(zhuǎn)FPGA》一書筆記10的相關(guān)內(nèi)容。為了讓大家更好

2015-03-03 14:12:09

上面介紹的是整個 FPGA 固件系統(tǒng)的實現(xiàn)方法,為了驗證設(shè)計的正確性,還需要編寫一個測試平臺對整個系統(tǒng)進(jìn)行仿真。由于實際情況下 FPGA 是和 PDIUSBD12 進(jìn)行通信,所以在測試平臺中需要虛擬

2018-11-28 15:22:56

測試腳本編寫本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt Testbench的編寫其實也沒有想象中那么

2015-08-25 21:30:23

/1bndF0bt完成了前面基本的設(shè)計輸入后,為了進(jìn)一步的驗證代碼所實現(xiàn)功能的正確性,我們還需要進(jìn)行仿真測試。關(guān)于仿真的一些深入的介紹大家可以參考筆者的《深入淺出玩轉(zhuǎn)FPGA》一書筆記10的相關(guān)內(nèi)容

2019-02-13 06:35:24

邏輯設(shè)計及構(gòu)建testbench的方法及技巧;針對FPGA器件的代碼優(yōu)化方案;第二階段 FPGA設(shè)計原則(面積與速度平衡互換原則、硬件可實現(xiàn)原則、同步設(shè)計原則等;FPGA的四種操作技巧(乒乓操作、串并轉(zhuǎn)

2012-09-13 20:07:24

SignalTap/ChipScope使用;FPGA設(shè)計技巧介紹;Verilog代碼規(guī)范; 基本實驗:基本開發(fā)流程實驗(LED控制實驗)語法練習(xí)實驗(數(shù)碼管實驗)Testbench實驗(I2C modelsim

2012-09-07 14:19:38

SignalTap/ChipScope使用;FPGA設(shè)計技巧介紹;Verilog代碼規(guī)范; 基本實驗:基本開發(fā)流程實驗(LED控制實驗)語法練習(xí)實驗(數(shù)碼管實驗)Testbench實驗(I2C modelsim

2012-10-12 09:29:00

仿真腳本設(shè)置圖2-10-2新建激勵點(diǎn)擊New會彈出如圖2-11所示的testbench設(shè)置文件對話框,找到已經(jīng)編寫好的激勵文件,單擊Add。在Test bench name中填寫對應(yīng)的激勵名稱。點(diǎn)擊OK

2019-01-24 01:54:24

本文主要講了Testbench_激勵、復(fù)位,的編寫方法

2012-05-23 19:26:17

給位大神,想問一下testbench中是否只是寫clk,reset等的變化?不是的話,里面究竟怎么寫才能等到自己的仿真?能否附一例子講解?謝謝

2015-04-11 16:03:08

testbench 設(shè)計教程

2013-09-12 12:06:30

如果輸入時鐘時差分時鐘信號,如何編寫testbench?

2014-09-15 19:37:38

testbench編寫基本結(jié)構(gòu)

2023-09-28 17:43:42

testbench教程,中英文兼?zhèn)洌瑵M足大家的需求,推薦觀看。

2016-01-12 17:55:20

testbench時鐘信號的編寫2011-01-13 11:07:38|分類: FPGA的分享 |標(biāo)簽:clockparameterreg占空比 time_period|舉報|字號訂閱

2014-05-10 00:51:58

本帖最后由 平漂流 于 2017-5-21 11:09 編輯

如圖,看Verilog仿真視頻教程里面,在testbench設(shè)置時候,直接復(fù)制“blocking_vlg_tst”到top

2017-05-21 11:04:04

如何在quartus ii 仿真測試時設(shè)置輸入變量的變換范圍,是在testbench中增加什么語句嗎?

2015-03-13 09:45:29

: /testbench File: I:/Work/FPGA/work/250/FPGA210_V1/stimulus/testbench.v# FATAL ERROR while loading

2012-07-05 10:40:42

自己編寫CPLD程序,想用modelsim進(jìn)行仿真,于是在Quartus里面編寫testbench文件,但是出現(xiàn)上圖錯誤,請高手解答一下。不勝感激!!!!!

2017-11-21 14:12:21

本帖最后由 jiaofengmin 于 2015-8-7 23:32 編輯

新手想請問一下有沒有高人指點(diǎn)一下testbench要怎么寫?

2015-08-07 23:14:30

ModelSim TestBench VHDL參考模板.vhdModelSim TestBench VHDL參考模板

2012-08-12 15:10:06

需要把在DSP中采集到的數(shù)據(jù)發(fā)送到FPGA中進(jìn)行處理,這部分語句(接受從DSP發(fā)送來的數(shù)據(jù))怎么用verilog語言編寫??是編寫個RAM模塊嗎??

2017-10-10 21:43:41

說明。在這里先要說明一下inout口在testbench中要定義為wire型變量。 先假設(shè)有一源代碼為: module xx(data_inout , ........); inout

2012-08-09 08:21:23

小白入門求教

書中的self-cheack testcase與testbench有什么區(qū)別么?

或者說這兩個之間有聯(lián)系么?

實際問題:我自己寫出來一個NICE的協(xié)處理器擴(kuò)展,在vivado中仿真成功,

現(xiàn)在想做指令擴(kuò)展測試,是要做testbench測試么?

先提前感謝大佬幫助了~

2023-08-12 06:59:08

`⑴ FPGA 開發(fā)中,是否需要進(jìn)行仿真驗證?為什么?有什么個人體會?⑵ 一般采用怎樣的仿真工具和仿真手段?了解 Testbench 嗎?⑶ 什么是前仿真和后仿真?能否根據(jù)自身經(jīng)歷,總結(jié)一下前仿真

2012-03-08 11:32:54

本帖最后由 蛙蛙蛙 于 2021-4-12 17:51 編輯

本視頻是Runber FPGA開發(fā)板的配套視頻課程,主要通過工程實例講解Modelsim的使用,課程首先介紹代碼源文件

2021-04-12 17:18:47

根據(jù)如下模塊,編寫對應(yīng)的testbench文件

2023-09-08 10:35:47

本文和設(shè)計代碼由FPGA愛好者小梅哥編寫,未經(jīng)作者許可,本文僅允許網(wǎng)絡(luò)論壇復(fù)制轉(zhuǎn)載,且轉(zhuǎn)載時請標(biāo)明原作者。TestBench中端口reg和wire定義解惑很多學(xué)員在學(xué)習(xí)TestBench的編寫的時候

2020-02-22 14:37:29

1. 測試文件編寫技巧2. 測試文件模板3. 測試文件編寫練習(xí)14. 測試文件編寫練習(xí)1答案5. 包文的概念6. 測試文件編寫練習(xí)27. 測試文件編寫練習(xí)2答案8. 測試文件編寫練習(xí)39. 測試文件

2015-10-27 09:46:14

,手把手演示工程創(chuàng)建,IP核調(diào)用、Testbench編寫以及仿真驗證,讓每一個0基礎(chǔ)的朋友都能快速跟上節(jié)奏。另外,有一定基礎(chǔ)的朋友,其實也可以觀看,因為在設(shè)計中,我已經(jīng)將很多的設(shè)計小技巧穿插在視頻中了。請

2015-09-22 14:06:56

我在電子發(fā)燒友上看了小梅哥的fpga學(xué)習(xí)視頻。看到rom那一節(jié)時,我按照視頻講解的方式調(diào)用了一個rom的ip核,編寫了testbench文件。但是,得到的仿真結(jié)果rom中的數(shù)據(jù)全是0,mif文件沒有問題,已經(jīng)設(shè)置好了,請問問題出在哪里?求各位大神指教

2018-03-07 11:31:24

這個論壇感覺說testbench的略少,分享一些testbench的文檔。。。。。

2016-09-08 18:03:13

在FPGA的應(yīng)用中,很多時候就是CPU+FPGA+一些常見外設(shè)(FLASH、SRAM等),FPGA的功能差別其實不大,那么它的測試文件差別應(yīng)該也不是這么大,為了簡化仿真,是不是可以寫些文件,通過修改

2013-08-29 20:42:31

嗨,當(dāng)我為PCIe設(shè)計編寫VHDL測試平臺時,我遇到了這個奇怪的錯誤:錯誤:HDLCompiler:1731- “C:/Projects/FPGA/SP605/PCIE/Sim_CS/tests

2019-04-10 11:42:27

設(shè)計構(gòu)想的過程,是否存在時序違規(guī)。其輸入文件為從布局布線結(jié)果中抽象出來的門級網(wǎng)表、Testbench和擴(kuò)展名為SDO或SDF的標(biāo)準(zhǔn)時延文件。SDO或SDF的標(biāo)準(zhǔn)時延文件不僅包含門延遲,還包括實際布線

2015-11-29 21:35:23

:基本FPGA開發(fā)流程(理論介紹);二選一數(shù)據(jù)選擇器(實現(xiàn)點(diǎn)亮LED燈)(需求分析->建立工程->設(shè)計輸入->分析綜合->testbench編寫->功能仿真->布局布線

2015-06-15 22:01:45

想問下,quartus在綜合的時候可以設(shè)置顯示錯誤嗎,因為很多時候quartus綜合通過以后調(diào)用modelsim就好提示testbench出錯。還有就是誰能給個vhdl的testbench指導(dǎo)文件

2015-10-09 09:38:17

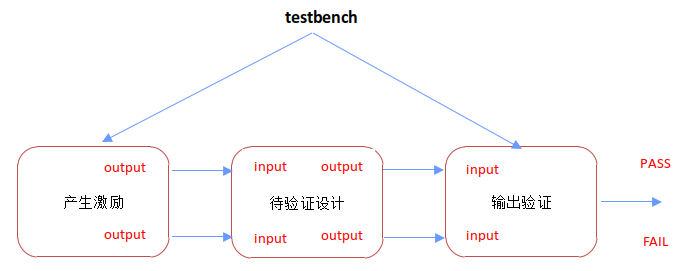

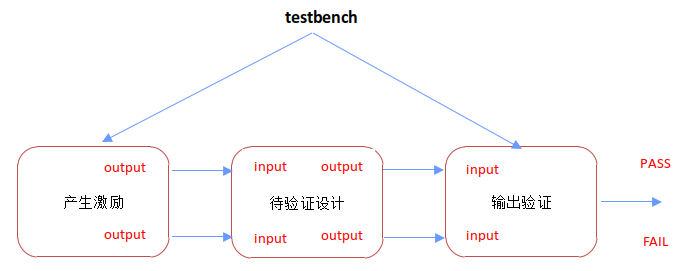

Testbench 不僅要產(chǎn)生激勵也就是輸入,還要驗證響應(yīng)也就是輸出。當(dāng)然也可以只產(chǎn)生激勵,然后通過波形窗口通過人工的方法去驗證波形,這種方法只能適用于小規(guī)模的設(shè)計。在 ISE 環(huán)境中,當(dāng)前資源操作

2017-11-28 11:19:34

用modelsim進(jìn)行仿真時,編寫testbench,inout信號應(yīng)該如何處理。

2019-03-20 16:39:12

1.quartusii 9.1 生成的testbench 后用VHDL 編寫后續(xù)程序的格式, 方法2如何用modelsim 關(guān)聯(lián)quartusii仿真3是不是testbench 沒有問題了在quartusii 執(zhí)行 RTL simulation 就可以從modelsim得到 波形

2013-05-17 21:36:56

仿真腳本設(shè)置圖2-10-2新建激勵點(diǎn)擊New會彈出如圖2-11所示的testbench設(shè)置文件對話框,找到已經(jīng)編寫好的激勵文件,單擊Add。在Test bench name中填寫對應(yīng)的激勵名稱。點(diǎn)擊OK

2016-12-19 22:33:24

請問testbench是這么搭建的嗎?實際放在adc前端是用電阻1:1拉回去做反饋嗎?

2021-06-22 08:09:59

請問modelsim的testbench用VHDL如何編寫

2013-12-15 15:28:31

我們可以通過編寫代碼來實現(xiàn)FPGA中的監(jiān)控嗎?以上來自于谷歌翻譯以下為原文can we implement supervisory control in FPGAs just by writing a code?

2019-06-24 09:20:43

LFSR testbench

The LFSR testbench can help you understand the LFSR basics:

1. Change

2009-05-14 11:18:18 50

50 Writing Testbench:The Quebec Bridge Company was formed in 1887 and for the nextthirteen years, very

2009-07-10 17:30:15 0

0 怎樣寫testbench-xilinx

在ISE 環(huán)境中, 當(dāng)前資源操作窗顯示了資源管理窗口中選中的資源文件能進(jìn)行的相關(guān)操作。在資源管理窗口選中了 testbench 文件后

2010-02-09 13:46:12 64

64 1. FPGA技術(shù)基礎(chǔ);2. FPGA基本設(shè)計流程及工具;3. FPGA設(shè)計指導(dǎo)原則與設(shè)計技巧;4. FPGA設(shè)計約束;5. TestBench設(shè)計與ModelSim仿真;6. FPGA配置及片內(nèi)調(diào)試技術(shù);7. 基于ISE、EDK的FPGA設(shè)計實例

2012-05-22 14:52:14 283

283 2014-05-28 15:39:59 55

55 編寫高效率的testbench,學(xué)習(xí)編寫測試文件的小伙伴們。

2016-05-11 16:40:55 16

16 Xilinx FPGA工程例子源碼:Verilog編寫的信道估計

2016-06-07 14:54:57 36

36 一篇文章叫你學(xué)會用VHDL寫TESTBENCH

2016-11-23 11:52:46 11

11 verilog Testbench

2016-12-13 22:20:48 3

3 層函數(shù)作為輸出RTL模塊的頂層,其它和這個函數(shù)層次平行,不需要被綜合的函數(shù)都可以作為testbench來使用。

2017-11-22 14:22:26 7672

7672 testbench是一種驗證的手段。首先,任何設(shè)計都是會有輸入輸出的。但是在軟環(huán)境中沒有激勵輸入,也不會對你設(shè)計的輸出正確性進(jìn)行評估。那么此時便有一種,模擬實際環(huán)境的輸入激勵和輸出校驗的一種“虛擬

2017-12-01 17:22:54 54578

54578

本文主要詳細(xì)介紹了使用QuartusⅡ軟件來編寫FPGA的方法及步驟,另外還介紹了Quartus II仿真的入門詳細(xì)教程分享。

2018-05-18 10:11:53 13212

13212 首先編寫相應(yīng)的C/C++語言程序,加入到Vivado HLS工程中,再編寫相應(yīng)的testbench代碼進(jìn)行編譯測試。

2018-07-14 08:56:00 18425

18425

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA控制多軸電機(jī),實現(xiàn)圓弧,直線插補(bǔ)功能,利用verilog語言編寫。

2018-09-26 08:00:00 78

78 跟大家解釋一點(diǎn),所有testbench本質(zhì)上都是串行執(zhí)行,因為在CPU環(huán)境下,沒有可靠并行執(zhí)行的能力。所有并行的語句,比如兩個always模塊,fork join語句塊,都是軟件模擬并行執(zhí)行的。所以

2018-10-10 16:14:15 9147

9147

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA教程之簡單的Testbench設(shè)計的詳細(xì)資料說明免費(fèi)下載。

2019-03-01 16:52:00 15

15 testbench是一種驗證的手段。首先,任何設(shè)計都是會有輸入輸出的。但是在軟環(huán)境中沒有激勵輸入,也不會對你設(shè)計的輸出正確性進(jìn)行評估。那么此時便有一種,模擬實際環(huán)境的輸入激勵和輸出校驗的一種“虛擬

2019-03-08 14:35:50 1950

1950 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA視頻教程之Verilog模塊的編寫和驗證詳細(xì)資料說明資料免費(fèi)下載。

2019-03-26 16:23:48 16

16 testbench是一個平臺,幫助你從軟件方面驗證的。但是在軟環(huán)境中沒有激勵輸入,也不會對你設(shè)計的輸出正確性進(jìn)行評估。那么此時便有一種,模擬實際環(huán)境的輸入激勵和輸出校驗的一種“虛擬平臺”的產(chǎn)生。在這個平臺上你可以對你的設(shè)計從軟件層面上進(jìn)行分析和校驗。

2019-12-17 07:02:00 1826

1826

testbench是一種驗證的手段。首先,任何設(shè)計都是會有輸入輸出的。但是在軟環(huán)境中沒有激勵輸入,也不會對你設(shè)計的輸出正確性進(jìn)行評估。那么此時便有一種,模擬實際環(huán)境的輸入激勵和輸出校驗的一種“虛擬平臺”的產(chǎn)生。在這個平臺上你可以對你的設(shè)計從軟件層面上進(jìn)行分析和校驗。

2019-12-11 07:09:00 1933

1933

定義信號類型:原來模塊中的輸入信號,定義成reg 類型,原來模塊中的輸出信號,定義為wire類型,但這里有個問題,如果在testbench中本身有一個模塊需要,如用來產(chǎn)生時鐘,送給要仿真的模塊,那怎么定義信號類型呢?

2019-07-31 17:52:43 891

891 自我檢查testbench設(shè)計:與前兩種方法不同,該方法實時檢查預(yù)期結(jié)果和實際結(jié)果,而不是仿真結(jié)束后才檢查。在testbench中插入錯誤追蹤信息可以顯示設(shè)計在哪里失敗,從而縮短調(diào)試時間。

2020-11-20 11:26:03 3282

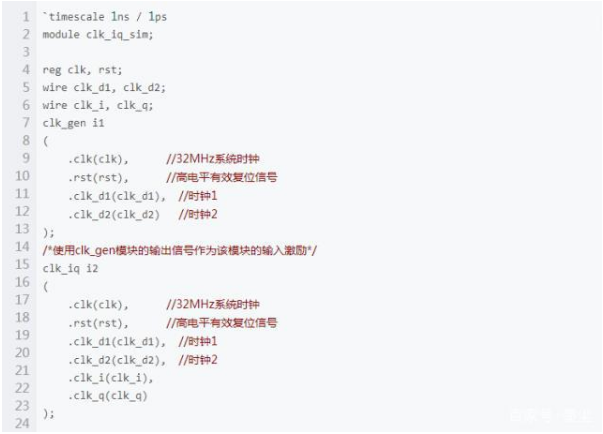

3282 在開始設(shè)計前,根據(jù)設(shè)計劃分好各功能模塊(為了敘述方便,這里以對“FPGA數(shù)字信號處理(十三)鎖相環(huán)位同步技術(shù)的實現(xiàn)”中設(shè)計的系統(tǒng)仿真為例)。編寫好第一個子模塊(本例中為雙相時鐘生成模塊),在Vivado中添加仿真sim文件,編寫testbench:

2020-11-20 11:29:30 3482

3482 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA仿真的學(xué)習(xí)課件和工程文件免費(fèi)下載包括了:1、testbench編寫,2、仿真工具使用,2、仿真工具使用,4、Vivado與Modelsim聯(lián)合仿真。

2020-12-10 15:28:18 30

30 大多數(shù)硬件設(shè)計人員對 verilog 的 testbench 比較熟悉,那是因為 verilog 被設(shè)計出來的目的就是為了用于測試使用,也正是因為這樣 verilog 的語法規(guī)則才被設(shè)計得更像

2020-12-14 08:00:00 17

17 本文檔的主要內(nèi)容詳細(xì)介紹的是在FPGA上編寫通過SPI總線配置外部PLL芯片AD9518和ADC9268的程序免費(fèi)下載。

2021-03-10 15:50:00 50

50 大家好,又到了每日學(xué)習(xí)的時間了,今天我們來聊一聊FPGA中測試文件編寫的相關(guān)知識,聊一聊激勵仿真。 ? 1. 激勵的產(chǎn)生 對于testbench而言,端口應(yīng)當(dāng)和被測試的module一一對應(yīng)。端口分為

2021-04-02 18:27:02 6010

6010 、Johnson計數(shù)器、PN碼發(fā)生器、頻率計等,這些例子是經(jīng)驗豐富的工程師寫的,我們可以學(xué)到編程思想、代碼風(fēng)格等方面的知識和經(jīng)驗,這些東西可能從學(xué)校老師或一般書籍都學(xué)習(xí)不到。 如果你用的不是Xilinx的FPGA,也就是說不使用ISE,那也沒關(guān)系,HDL代碼和testbench的設(shè)計思想和方法是一樣的,你照

2021-04-11 10:46:53 2793

2793

本講使用matlab產(chǎn)生待濾波信號,并編寫testbench進(jìn)行仿真分析,在Vivado中調(diào)用FIR濾波器的IP核進(jìn)行濾波測試,下一講使用兩個DDS產(chǎn)生待濾波的信號,第五講或第六講開始編寫verilog代碼設(shè)計FIR濾波器,不再調(diào)用IP核。

2021-04-27 18:18:51 3892

3892

使用Matlab和Verilog實現(xiàn)fibonacci序列包括源代碼和testbench(電源技術(shù)論壇app)-使用Matlab和Verilog實現(xiàn)fibonacci序列,包括源代碼和testbench,適合感興趣的學(xué)習(xí)者學(xué)習(xí),可以提高自己的能力,大家可以多交流哈

2021-09-16 14:41:53 13

13 Testbench是幾乎所有做動態(tài)仿真驗證的工程師都要面對的問題,可能是需要設(shè)計,或者開發(fā),又或者是維護(hù),總有很多事情要在這上面折騰。

2023-05-08 10:16:09 562

562 UVM類庫提供了通用的代碼功能,如component hierarchy、transaction level model(TLM),configuration database等等,使用戶能夠創(chuàng)建任何類型的Testbench架構(gòu)。

2023-05-22 10:14:28 1118

1118

設(shè)計規(guī)劃--波形繪制--編寫代碼--代碼編譯--編寫testbench--對比波形--綁定管腳--全編譯--上板驗證

2023-05-22 15:07:57 785

785

廢話不多說直接上干貨,testbench就是對寫的FPGA文件進(jìn)行測試的文件,可以是verilog也可以是VHDL。

2023-06-28 16:44:18 1939

1939

之前在使用Verilog做FPGA項目中、以及其他一些不同的場合下,零散的寫過一些練手性質(zhì)的testbench文件,開始幾次寫的時候,每次都會因為一些基本的東西沒記住、寫的很不熟練,后面寫的時候稍微

2023-08-01 12:44:27 1285

1285

??對于小型設(shè)計來說,最好的測試方式便是使用TestBench和HDL仿真器來驗證其正確性。一般TestBench需要包含這些部分:實例化待測試設(shè)計、使用測試向量激勵設(shè)計、將結(jié)果輸出到終端或波形窗口便于可視化觀察、比較實際結(jié)果和預(yù)期結(jié)果。

2023-09-01 09:57:31 463

463

自動化驗證testbench結(jié)果可以減少人工檢查的時間和可能犯的失誤,尤其對于比較大的設(shè)計。

2023-09-04 09:15:17 454

454 ?在開始設(shè)計前,根據(jù)設(shè)計劃分好各功能模塊(為了敘述方便,這里以對“FPGA數(shù)字信號處理(十三)鎖相環(huán)位同步技術(shù)的實現(xiàn)”中設(shè)計的系統(tǒng)仿真為例)。

2023-09-04 09:54:54 1054

1054

小的設(shè)計中,用TestBench來進(jìn)行仿真是一個很不錯的選擇。VHDL與Verilog語言的語法規(guī)則不同,它們的TestBench的具體寫法也不同,但是應(yīng)包含的基本結(jié)構(gòu)大體相似,在VHDL的仿真文件中應(yīng)包含以下幾點(diǎn):實體和結(jié)構(gòu)

2023-09-09 10:16:56 721

721

電子發(fā)燒友App

電子發(fā)燒友App

評論