速度和面積一直都是FPGA設(shè)計(jì)中非常重要的兩個(gè)指標(biāo)。所謂速度,是指整個(gè)工程穩(wěn)定運(yùn)行所能夠達(dá)到的最高時(shí)鐘頻率,它不僅和FPGA內(nèi)部各個(gè)寄存器的建立時(shí)間余量

2023-04-10 11:07:32 1064

1064 的多通道流量,那么單純基于DSP的硬件系統(tǒng)就可能需要更大的面積,成本或功耗。一個(gè)FPGA僅在一個(gè)器件上就能高提供多達(dá)550個(gè)并行乘法和累加運(yùn)算,從而以較少的器件和較低的功耗提供同樣的性能。但對于定期系數(shù)更新,決策控制任務(wù)或者高速串行處理任務(wù),FPGA的優(yōu)化程度遠(yuǎn)不如DSP。

2019-08-30 06:31:29

`在FPGA中,實(shí)現(xiàn)邏輯的基本單元是查找表(LUT)而非基本門電路。目前的FPGA中,單一LE或者Cell通常能實(shí)現(xiàn)至少4輸入查找表的邏輯功能。4輸入查找表可以看成是具有4位地址1位數(shù)據(jù)的存儲(chǔ)器

2018-07-30 18:11:19

`FPGA面積優(yōu)化1.對于速度要求不是很高的情況下,我們可以把流水線設(shè)計(jì)成迭代的形式,從而重復(fù)利用FPGA功能相同的資源。2.對于控制邏輯小于共享邏輯時(shí),控制邏輯資源可以用來復(fù)用,例如FIR濾波器

2014-12-04 13:52:40

的復(fù)用。 2.面積換速度 在這種方法中面積的復(fù)制可以換取速度的提高。支持的速度越高,就意味著可以實(shí)現(xiàn)更高的產(chǎn)品性能。一些注重產(chǎn)品性能的應(yīng)用領(lǐng)域可以采用并行處理技術(shù),實(shí)現(xiàn)面積換速度。二硬件可實(shí)現(xiàn)原則

2016-09-28 16:14:51

想為cyclone V 系列的5CEFA7F27這款FPGA設(shè)計(jì)去耦電容電路,但是不知道該如何下手。參考了altera公司的一塊開發(fā)板,給出的FPGA的去耦電容電路如下所示,但是感覺這個(gè)去耦電容電路

2016-07-09 10:11:21

面積換速度在這種方法中面積的復(fù)制可以換取速度的提高。支持的速度越高,就意味著可以實(shí)現(xiàn)更高的產(chǎn)品性能。一些注重產(chǎn)品性能的應(yīng)用領(lǐng)域可以采用并行處理技術(shù),實(shí)現(xiàn)面積換速度。二硬件可實(shí)現(xiàn)原則FPGA設(shè)計(jì)通常會(huì)

2015-12-03 16:41:21

的復(fù)用。 2.面積換速度 在這種方法中面積的復(fù)制可以換取速度的提高。支持的速度越高,就意味著可以實(shí)現(xiàn)更高的產(chǎn)品性能。一些注重產(chǎn)品性能的應(yīng)用領(lǐng)域可以采用并行處理技術(shù),實(shí)現(xiàn)面積換速度。二硬件可實(shí)現(xiàn)原則

2017-06-01 10:31:59

流水線技術(shù)插入觸發(fā)器后,可用N個(gè)時(shí)鐘周期實(shí)現(xiàn),因此系統(tǒng)的工作速度可以加快,吞吐量加大。注意,流水線設(shè)計(jì)會(huì)在原數(shù)據(jù)通路上加入延時(shí),另外硬件面積也會(huì)稍有增加。

2023-04-23 14:58:18

誰能告訴我CYUB3014的最大GPIO切換速度? 以上來自于百度翻譯 以下為原文anyone can tell me the maximum gpio's toggle speed of the cyu***3014?

2019-01-24 06:27:51

消息隊(duì)列是什么?消息隊(duì)列有何作用?FreeRtos中消息隊(duì)列API的調(diào)用該怎樣去實(shí)現(xiàn)呢?

2022-01-20 07:04:33

PA_IK代碼該如何去實(shí)現(xiàn)?PA_VMC算法的原理是什么?

2021-10-14 09:00:19

F407的規(guī)則同步ADC采集如何 實(shí)現(xiàn)256k采樣+轉(zhuǎn)換速度?

2024-03-07 07:51:02

串口屏和單片機(jī)之間的通信過程是怎樣的?STM32單片機(jī)和中顯串口屏之間的通信該如何去實(shí)現(xiàn)呢?

2021-12-07 07:06:58

請問STM32的DAC轉(zhuǎn)換精度和轉(zhuǎn)換速度是多少

2023-11-08 06:16:55

STM32的串口通信方式有哪幾種?STM32串口應(yīng)該怎么去使用?STM32的串口功能該如何去實(shí)現(xiàn)?

2021-08-11 07:09:58

STM32的串口發(fā)送和接收代碼該如何去實(shí)現(xiàn)呢?QT上位機(jī)的源碼該如何去實(shí)現(xiàn)呢?

2021-12-09 06:01:53

socket通信該怎樣去實(shí)現(xiàn)呢?怎樣去實(shí)現(xiàn)socket AES-CBC加密呢?

2022-01-20 07:41:55

本帖最后由 eehome 于 2013-1-5 10:10 編輯

本節(jié)將重點(diǎn)講解,用FPGA實(shí)現(xiàn)按鍵去抖的方法,在以往的按鍵去抖中,大部分采用的是單片機(jī)去抖方法。這里我們將介紹FPGA的實(shí)現(xiàn)

2012-03-19 14:48:40

的復(fù)用。 2.面積換速度 在這種方法中面積的復(fù)制可以換取速度的提高。支持的速度越高,就意味著可以實(shí)現(xiàn)更高的產(chǎn)品性能。一些注重產(chǎn)品性能的應(yīng)用領(lǐng)域可以采用并行處理技術(shù),實(shí)現(xiàn)面積換速度。二硬件可實(shí)現(xiàn)原則

2015-11-30 10:45:48

下位機(jī)中的μC/OS-II多任務(wù)該怎樣去實(shí)現(xiàn)呢?如何對下位機(jī)中的串口數(shù)據(jù)進(jìn)行讀取并解析呢?

2021-12-21 06:40:38

什么是倒立擺?倒立擺該如何去實(shí)現(xiàn)呢?

2021-12-23 06:18:33

的總速率達(dá)到600 Mbps。就在ADC之后,在FPGA中,我必須使用存儲(chǔ)器(RAM)為每個(gè)ADC(500位)存儲(chǔ)aprox 50個(gè)采樣并延遲它們。這是我的問題,我必須以同樣的速度同時(shí)讀寫不同的記憶位置

2020-03-26 09:31:54

親愛的用戶,我通過SPI在FPGA中寫入一些數(shù)據(jù)。我正在使用XC3S50。我制作了一個(gè)內(nèi)存數(shù)組,并將數(shù)據(jù)讀取和寫入相同的數(shù)據(jù)。這部分在硬件中正常工作。存儲(chǔ)器中的所有寄存器都是8位寬。然而,當(dāng)我

2019-01-23 10:40:59

請問在FPGA中怎樣去實(shí)現(xiàn)4G無線球形檢測器?

2021-04-29 07:20:13

基于FPGA和AD1836的I2S接口該如何去設(shè)計(jì)?

2021-05-26 06:45:37

什么是IBIS5-B-1300圖像傳感器?基于FPGA的CMOS控制時(shí)序該如何去設(shè)計(jì)?

2021-06-03 06:35:43

DDC是由哪幾部分組成的?基于FPGA的DDC該怎樣去設(shè)計(jì)?如何對DDC進(jìn)行仿真測試?

2021-05-27 07:16:24

它們在高速和實(shí)時(shí)系統(tǒng)中的應(yīng)用。隨著深亞微米半導(dǎo)體制造工藝的不斷創(chuàng)新,百萬門可編程器件的不斷推出,為DSP提供了第3種有效的解決方案,即利用FPGA實(shí)現(xiàn)DSP運(yùn)算硬件化。它能夠在集成度、速度和系統(tǒng)功能

2019-08-02 06:03:48

UART的實(shí)現(xiàn)原理是什么?基于FPGA的UART接口怎樣去設(shè)計(jì)?

2021-04-28 07:00:46

基于FPGA的圖形式AMLCD控制器該如何去設(shè)計(jì)?怎樣去設(shè)計(jì)一種VGA視頻接口電路?

2021-06-08 06:57:57

在FPGA 上設(shè)計(jì)一個(gè)高性能、靈活的、面積小的通信體系結(jié)構(gòu)是一項(xiàng)巨大的挑戰(zhàn)。大多數(shù)基于FPGA 的片上網(wǎng)絡(luò)都是運(yùn)行在一個(gè)單一時(shí)鐘下。隨著FPGA 技術(shù)的發(fā)展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

基于FPGA的機(jī)載顯示系統(tǒng)該如何去設(shè)計(jì)?如何對機(jī)載顯示系統(tǒng)進(jìn)行優(yōu)化?

2021-06-01 06:04:12

請教各位,基于FPGA的硬件控制系統(tǒng)該如何去設(shè)計(jì)?

2021-04-28 07:01:25

; P33在HDL中,為了通過面積去換速度,我們將上式改變?nèi)缦拢?P1 = P11 & P12 &P13P2 = P21 & P22 & P23P3 = P31 &

2017-09-22 13:20:55

硬件是用DSP來實(shí)現(xiàn)的;FPGA技術(shù)近兩年才達(dá)到可以實(shí)現(xiàn)大點(diǎn)數(shù)FFT的水平,并且體積、速度、靈活性等各種性能都優(yōu)于DSP,但開發(fā)難度大,研制費(fèi)用高。本文將討論基于FPGA的大點(diǎn)數(shù)超高速FFT算法。

2009-06-14 00:19:55

請教一下,基于DSP和FPGA的嵌入式控制器該如何去設(shè)計(jì)?

2021-05-06 09:16:19

基于HAL庫中的串口中斷接收函數(shù)該如何去實(shí)現(xiàn)呢?有什么方法嗎?

2021-12-06 06:56:44

PCIe是什么?有什么核心優(yōu)勢?Xilinx的PCIe端點(diǎn)模塊的顯著優(yōu)勢包括哪些?基于Virtex-5 LXT FPGA的PCIe端點(diǎn)該怎樣去設(shè)計(jì)?

2021-05-26 06:39:11

DS18B20是什么?如何去實(shí)現(xiàn)FPGA與DS18B20之間的通信?

2021-05-07 06:48:43

如何去實(shí)現(xiàn)FPGA中的各個(gè)模塊?如何去實(shí)現(xiàn)FPGA與PC的串行通信?

2021-05-26 07:25:13

FPGA配置原理簡介基于模塊化動(dòng)態(tài)部分重構(gòu)FPGA的設(shè)計(jì)方法如何去實(shí)現(xiàn)FPGA動(dòng)態(tài)部分的重構(gòu)?

2021-04-29 06:33:12

的柵極引線即可實(shí)現(xiàn)該功能;參見圖3。第二步是在開關(guān)節(jié)點(diǎn)與接地之間加裝一個(gè)緩沖器(RSUB與CSUB)。緩沖器電路可以在轉(zhuǎn)換過渡期間抑制寄生電感和電容。

圖3:接通和關(guān)閉電路

除利用上述方法來降低開關(guān)

2018-08-31 19:55:41

嵌入式測試是什么?如何用FPGA技術(shù)去實(shí)現(xiàn)嵌入式設(shè)計(jì)?如何測試FPGA中的高速串行I/O?

2021-04-13 07:03:58

中頻調(diào)制解調(diào)系統(tǒng)具有哪些特點(diǎn)?如何利用FPGA去實(shí)現(xiàn)中頻調(diào)制解調(diào)系統(tǒng)?

2021-04-28 07:21:00

interconnect模塊,同時(shí)需要有跨時(shí)鐘域的邏輯去將每個(gè)GDDR6用戶接口時(shí)鐘轉(zhuǎn)換到邏輯主時(shí)鐘。除了圖1中的8個(gè)讀寫模塊外,紅色區(qū)域的邏輯都需要用FPGA的可編程邏輯去實(shí)現(xiàn)。 圖1 傳統(tǒng)FPGA實(shí)現(xiàn)架構(gòu)對于AXI

2020-10-20 09:54:00

運(yùn)算平臺之間是如何連接的?SRIO系統(tǒng)的應(yīng)用實(shí)例有哪些?如何利用串行RapidIO去實(shí)現(xiàn)FPGA協(xié)處理?

2021-04-29 06:17:59

在FPGA中,動(dòng)態(tài)相位調(diào)整(DPA)主要是實(shí)現(xiàn)LVDS接口接收時(shí)對時(shí)鐘和數(shù)據(jù)通道的相位補(bǔ)償,以達(dá)到正確接收的目的。那么該如何在低端FPGA中實(shí)現(xiàn)DPA的功能呢?

2021-04-08 06:47:08

對于設(shè)計(jì)者來說,當(dāng)然希望我們設(shè)計(jì)的電路的工作頻率(在這里如無特別說明,工作頻率指FPGA片內(nèi)的工作頻率)盡量高。我們也經(jīng)常聽說用資源換速度,用流水的方式可以提高工作頻率,這確實(shí)是一個(gè)很重要的方法

2018-08-08 11:16:37

下行擾碼的生成過程是怎樣的?如何用FPGA去實(shí)現(xiàn)下行擾碼?

2021-04-30 07:24:05

(SPRAM) 、 FIFO 等。6. 串并轉(zhuǎn)換設(shè)計(jì)技巧串并轉(zhuǎn)換是 FPGA 設(shè)計(jì)的一個(gè)重要技巧,它是數(shù)據(jù)流處理的常用手段,也是面積與速度互換思想的直接體現(xiàn)。串并轉(zhuǎn)換的實(shí)現(xiàn)方法多種多樣,根據(jù)數(shù)據(jù)的排序

2020-09-18 10:32:44

語音識別技術(shù)有哪些應(yīng)用?嵌入式語音識別技術(shù)在80251內(nèi)核中該如何去實(shí)現(xiàn)呢?

2021-12-23 07:42:08

Flash的性能參數(shù)和操作時(shí)序是什么?怎樣利用FPGA去實(shí)現(xiàn)Flash編程器?

2021-05-07 07:27:57

最近開始學(xué)習(xí)使用dspf28335,想要將以前開發(fā)的一個(gè)算法在dsp中應(yīng)用,該算法中涉及到了車體的振動(dòng)加速度,需要對振動(dòng)加速度進(jìn)行積分后獲得速度,然后進(jìn)行運(yùn)算,我在網(wǎng)上查資料沒有找到關(guān)于用c語言實(shí)現(xiàn)積分的,不知道該功能應(yīng)該怎樣實(shí)現(xiàn)?

2019-10-08 09:32:15

轉(zhuǎn)換速率SR (Slew Rate)轉(zhuǎn)換速率是表示運(yùn)算放大器的工作速度的參數(shù)。表示輸出電壓在規(guī)定的單位時(shí)間可變化的比例。例如,1[V/μs]表示在1[μs]內(nèi)可使電壓發(fā)生1[V]的波動(dòng)。理想

2019-04-15 06:20:31

只要速度具有優(yōu)勢,那么增加的這部分邏輯依然能夠實(shí)現(xiàn)降低面積提高速度的目的。 可以看到,速度換面積的關(guān)鍵是高速基本單元的復(fù)用。 2.面積換速度 在這種方法中面積的復(fù)制可以換取速度的提高。支持的速度

2016-12-07 15:51:20

28335 FLASH 中的程序在 RAM中 執(zhí)行,有之前做過的么?具體方法該怎么去實(shí)現(xiàn)呢?

2018-11-16 14:19:50

DSP內(nèi)的計(jì)算速度是快的,但是它的I/O口的交換速度有多快呢?

2019-08-21 04:24:37

我想使用外部多路復(fù)用器來增加 ADC 的數(shù)量,但開關(guān)速度是一個(gè)問題。幸運(yùn)的是,一些多路復(fù)用器具有 13 ns 的切換速度(~100 MHz),我打算使用 GPIO 信號對其進(jìn)行切換。然而,它也引起了對 GPIO 引腳的切換速度的關(guān)注。STM32WB55 微控制器的 GPIO 引腳的切換速度是多少?

2022-12-02 06:04:35

請問一下STM32中的位變量該如何去實(shí)現(xiàn)呢?

2021-12-15 07:34:56

DDFS技術(shù)原理是什么?DDFS的FPGA實(shí)現(xiàn)的參數(shù)怎樣去計(jì)算?如何利用FPGA去實(shí)現(xiàn)DDFS?

2021-04-28 07:01:29

請問怎樣去實(shí)現(xiàn)一種基于FPGA的矩陣運(yùn)算?

2021-06-22 07:00:19

轉(zhuǎn)換速率SR (Slew Rate)轉(zhuǎn)換速率是表示運(yùn)算放大器的工作速度的參數(shù)。表示輸出電壓在規(guī)定的單位時(shí)間可變化的比例。例如,1[V/μs]表示在1[μs]內(nèi)可使電壓發(fā)生1[V]的波動(dòng)。理想

2019-06-11 04:20:34

磁帶庫的機(jī)械手交換速度 機(jī)械手是磁帶庫產(chǎn)品里面成本很高的一個(gè)部件,它負(fù)責(zé)磁帶的加載和卸載工作

2010-01-09 10:00:16 911

911 轉(zhuǎn)換速率,轉(zhuǎn)換速率是什么意思

運(yùn)放的轉(zhuǎn)換速率轉(zhuǎn)換速率(SR)是運(yùn)放的一個(gè)重要指標(biāo),單位是V/μs。該指標(biāo)越高,對信號的細(xì)

2010-03-22 13:38:44 8115

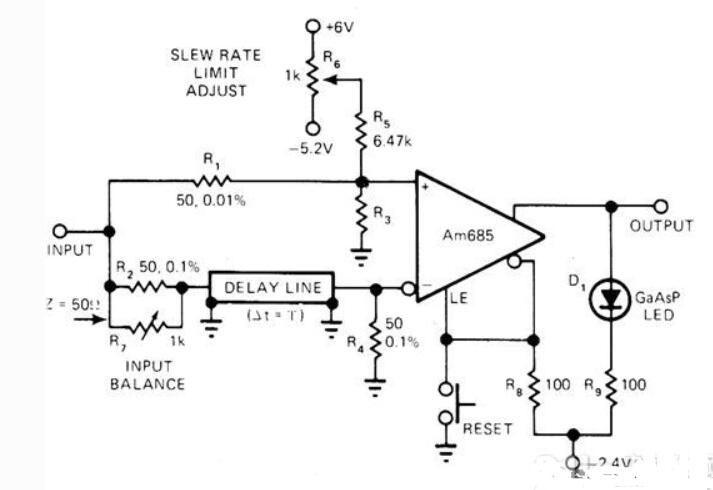

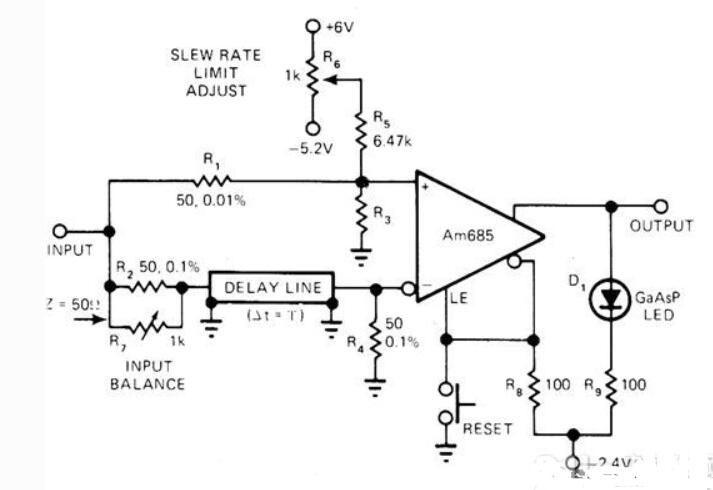

8115 轉(zhuǎn)換速度可以隨意改變的變化率控制電路

電路的功能

這類電路是

2010-05-11 15:25:11 774

774

在使用6MHz 或12MHz 晶振頻率的MCS251 系統(tǒng)中, 測試DAC0832 電路的數(shù)模轉(zhuǎn)換速度和可靠的操作頻率. 實(shí)驗(yàn)結(jié)果表明: 數(shù)字量的切換幅度是影響數(shù)模轉(zhuǎn)換速度的主要因素, 較為可靠的最高數(shù)模轉(zhuǎn)換

2011-05-17 17:45:59 126

126 針對增量式光電編碼器經(jīng)典速度測量算法M/T法低速采樣時(shí)間過長和位置測量算法精度不高的問題,本文基于定采樣周期M/T法設(shè)計(jì)實(shí)現(xiàn)了速度和位置測量板卡。采用Xilinx公司的XC3S400 FPGA為核心

2017-11-17 15:54:51 1934

1934 在FPGA中,如果要將一個(gè)采樣率為480MHz,中頻頻率為302.5MHz的信號變頻到零中頻的基帶信號,要怎么做呢?

2019-06-14 17:41:41 1783

1783 在FPGA中,如果要將一個(gè)采樣率為480MHz,中頻頻率為302.5MHz的信號變頻到零中頻的基帶信號,要怎么做呢?

2019-08-07 17:50:52 844

844 數(shù)字信號處理。包括圖像處理,雷達(dá)信號處理,醫(yī)學(xué)信號處理等。優(yōu)勢是實(shí)時(shí)性好,用面積換速度,比CPU快的多。

2019-09-04 15:12:17 14019

14019 電路低于10ns的延緩線長度條件下利用Am685比較器測試輸入信號的轉(zhuǎn)換速率。當(dāng)轉(zhuǎn)換速率超過由R6設(shè)定的預(yù)定限,比較器轉(zhuǎn)換狀態(tài)和壓接頭,打開LED。推復(fù)位開關(guān)恢復(fù)正常運(yùn)行。基于輸入信號和時(shí)間延遲對應(yīng)的對比。輸入信號的導(dǎo)數(shù)等于其瞬時(shí)轉(zhuǎn)換率。

2019-12-08 03:53:00 3248

3248

在這種方法中面積的復(fù)制可以換取速度的提高。支持的速度越高,就意味著可以實(shí)現(xiàn)更高的產(chǎn)品性能。一些注重產(chǎn)品性能的應(yīng)用領(lǐng)域可以采用并行處理技術(shù),實(shí)現(xiàn)面積換速度。

2020-07-10 09:51:29 1212

1212 一、面積與速度的平衡互換原則 這里的面積指的是 FPGA 的芯片資源,包括邏輯資源和 I/O 資源等;這里的速度指的是 FPGA 工作的最高頻率(和 DSP 或者 ARM 不同,FPGA 設(shè)計(jì)的工作

2023-02-03 15:30:30 389

389 速度-面積互換原則是貫穿FPGA設(shè)計(jì)的重要原則:速度是指工程穩(wěn)定運(yùn)行所能達(dá)到的最高時(shí)鐘頻率,通常決定了FPGA內(nèi)部寄存器的運(yùn)行時(shí)序;面積是指工程運(yùn)行所消耗的資源數(shù)量,通常包括觸發(fā)器

2023-06-09 09:36:37 798

798

電子發(fā)燒友網(wǎng)站提供《基于FPGA的速度和位置測量板卡設(shè)計(jì)實(shí)現(xiàn).pdf》資料免費(fèi)下載

2023-11-08 09:49:28 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論