1 、引言

數字鎖相環頻率合成器已經廣泛的運用在軍事和民用無線通信領域,而用CPU控制的可編程大規模數字鎖相環頻率合成器則是其中的關鍵技術。當前,可編程邏輯電路在數字系統設計中飛速發展,很多中規模,甚至大規模的數字系統已經可以通過可編程邏輯電路來實現單片集成,即用一個芯片完成整個數字系統的設計。因此將CPU控制的數字鎖相環頻率合成系統集成在一塊可編程邏輯芯片中實現已經成為可能。本系統由多個可編程的數字分頻器、數字鑒頻-鑒相器以及協調控制工作的CPU組成。

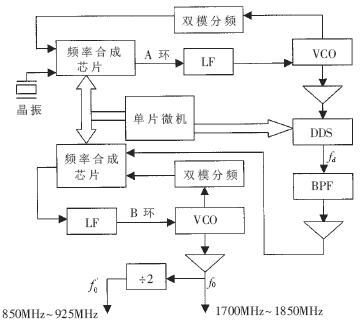

2 、系統結構

數字鎖相環頻率合成系統的工作原理是:鎖相環對高穩定度的基準頻率(通常由晶體振蕩器直接或經分頻后提供)進行精確鎖定,環內串接可編程的分頻器,通過編程改變分頻器的分頻比,使環路總的分頻比為N(可通過編程改變),從而環路穩定的輸出 N倍的基準頻率,而整個程序和系統的控制是要由CPU來完成的。

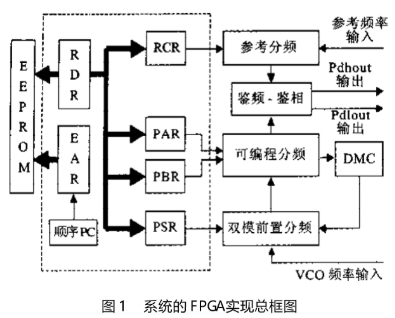

圖1為CPU控制的數字鎖相環頻率合成系統的 FPGA實現方案。

圖1中虛線部分為CPU模塊,CPU通過讀取 ROM和對相應的寄存器置數來完成系統的控制;EEPROM為外接ROM,保存系統設置和預置頻點的數據;參考分頻模塊對輸入的參考頻率進行預分頻,形成鑒頻和鑒相的基準頻率;鑒頻-鑒相模塊完成環路的鑒頻和鑒相功能;可編程分頻模塊和雙模前置分頻模塊共同組成環路內串接的可改變分頻比的分頻器;Pdhout和Pdlout是鑒頻和鑒相輸出的誤差信號。誤差信號再通過環路濾波器產生誤差電壓控制VCO,VCO的輸出反饋至系統,經過分頻和鎖相過程,直到環路達到鎖定狀態,此時 VCO的輸出即為所要求的穩定頻率。

3、 參考分頻模塊

參考分頻模塊主要完成對參考頻率(通常由外接晶體振蕩器輸入)進行預分頻,從而輸出鑒頻和鑒相的基準頻率。

為了擴展基準頻率的范圍,在模塊內采用4位的參考分頻寄存器(RCR),參考頻率的分頻比可在2~15之間自由選擇。實現過程就是采用4位的加法計數器對參考頻率進行記數,記數器的預置值為RCR中設置的參考分頻值,經過分頻后,模塊輸出的頻率送入鑒頻-鑒相模塊中作為鑒頻-鑒相的基準頻率。

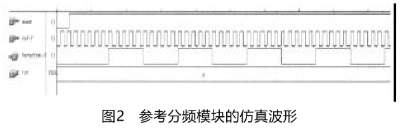

圖2是參考分頻模塊的仿真波形。圖中reset為復位信號,低電平有效;ref_f為輸入模塊的參考頻率;benchm_f為經過分頻以后模塊輸出的基準頻率;RCR中預置的值為HA,即10分頻。

4、 雙模前置分頻模塊

雙模前置分頻模塊主要完成對VCO輸出反饋到系統的頻率進行前置分頻,前置分頻后的頻率再輸入可編程分頻器再分頻。

為了擴展頻率合成器的輸出頻率范圍,在結構較為簡單的頻率合成系統中,VCO輸出反饋到系統的頻率是通過一個單模的前置分頻器,分頻后送入可編程分頻器再分頻,這樣雖然結構較為簡單,但是卻降低了頻率合成器的性能。如果要求提高頻率合成器的輸出頻率,則要加大前置分頻比,從而降低了輸出頻率的分辨率。為了保持穩定的輸出頻率分辨率,同時提高頻率合成器的輸出頻率,系統采用了雙模前置分頻。雙模前置分頻具有兩種分頻模式,分別對應兩種分頻比,模式由雙模控制邏輯(DMC)進行控制。當DMC為1時,前置分頻工作在M分頻模式,其中M為4位的前置分頻寄存器(PSR)中預置的前置分頻值。當DMC為0 時,前置分頻工作在M+1分頻模式。M的范圍是 2~15。其分頻功能的實現也采用4位加法計數器的方式。

圖3是雙模前置分頻模塊的仿真波形。圖中 reset為復位信號;dmc為雙模控制邏輯;vco_f為VCO輸出反饋到系統的頻率;prescaler_f為雙模前置分頻后輸出的頻率;PSR中預置的值為H8,即采用8/9雙模分頻。

5 、可編程分頻模塊

可編程分頻模塊主要完成對前置分頻模塊輸出的頻率進行再次分頻,并且通過DMC的控制和雙模前置分頻模塊配合完成所要求的分頻功能。

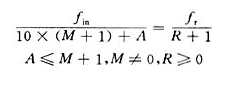

可編程分頻模塊由兩個可編程分頻器和雙模控制邏輯DMC組成。兩個可編程分頻器的分頻比分別由可編程分頻寄存器A(PAR)和可編程分頻寄存器B(PBR)中的分頻值決定。DMC的工作原理為:分頻器A和分頻器B分別由兩個4位的加法計數器A、B組成,預置的值分別為PAR和PBR中的分頻值,加法記數開始后,在兩個記數器都未記數到預置值時,DMC輸出0,此時雙模前置分頻模塊工作在M+1分頻模式;當計數器B記數到預置值時,DMC輸出1,此時雙模前置分頻模塊工作在M分頻模式,同時計數器B停止工作,計數器A繼續工作,一直記數到預置值,然后計數器 A、B又同時開始新的記數工作。假設PAR=A,PBR=B,則當計數器B記數到預置值時,包括前置分頻的記數,共記數(M+1)×B,此后計數器B停止工作,計數器A繼續完成剩余的(A-B )次記數,此階段包括前置分頻記數共記數M×( A-B),所以當兩個計數器都完成依次記數時,包括前置分頻記數總的記數為:

N=(M+1)×B+ M×(A-B)=MA+B ,即環路進行了N分頻。

由以上分析可以看出來,PAR中的值必須要大于PBR中的值,否則模塊將運行不正常。

圖4是可編程分頻模塊的仿真波形。圖中re set 為復位信號;prescaler_f為雙模前置分頻后輸出的頻率;prog_f為經過兩個可編程分頻器分頻后模塊輸出的頻率;PAR預置的值為HC,即A=12分頻;PBR預置的值為H4,即 B=4分頻;dmc為雙模控制邏輯。

6、 鑒頻-鑒相模塊

鑒頻-鑒相模塊主要完成對經過分頻后輸入模塊的頻率和基準頻率進行鑒頻-鑒相,并且輸出誤差結果。

此模塊采用超前與滯后雙輸出方式:如果輸入頻率高于基準頻率或相位超前,則Pdhout輸出負脈沖,而Pdlout輸出高電平;如果輸入頻率低于基準頻率或相位滯后,則Pdhout輸出高電平,而Pdlout輸出負脈沖;當輸入頻率和基準頻率同相后,Pdlout和Pdhout都輸出高電平。

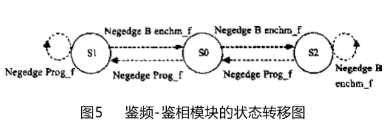

鑒頻-鑒相模塊的工作原理為:當輸入頻率和基準頻率不同頻時,模塊工作在鑒頻方式;當輸入頻率和基準頻率同頻但不同相時,模塊工作在鑒相方式,從而擴展環路的快捕帶,使環路較快的進行相位鎖定,進而達到閉環鎖定狀態。數字鑒頻—鑒相模塊采用自底向上的設計方法,其輸出方式與功能符合圖5所示的狀態轉移圖。

圖中Negedge Benchm_f為基準頻率波形的下降沿;Negedge Prog_f為輸入頻率波形的下降沿;S0狀態,模塊輸出Pdhout=1,Pdlout=1,此時處于同頻同相;S1狀態,模塊輸出Pdhout=0,Pdlout=1,此時輸入頻率高于基準頻率或者輸入頻率比基準頻率相位超前;S2狀態,模塊輸出Pdhout=1,Pdlout=0,此時輸入頻率低于基準頻率或者輸入頻率比基準頻率相位滯后。

圖6、7、8、9是不同輸入頻率時的仿真圖。

圖中reset為復位信號;benchm_f為基準頻率;prog_f為輸入頻率;pdhout和pdlout為鑒頻-鑒相模塊的輸出。

7 、CPU模塊

CPU模塊主要完成對整個系統的控制。CPU包括一個8位的讀數據寄存器(RDR);一個10位的外部EEPROM地址寄存器(EAR),尋址空間為1024×8bit,支持1023個頻點的頻率合成;4個4位的分頻寄存器,包括參考分頻寄存器(RCR),前置分頻寄存器(PSR),可編程分頻寄存器A(PAR)和可編程分頻寄存器B (PBR)。

CPU內的控制包括:讀外部程序存儲器(EEPROM)控制、程序執行控制、可編程分頻器置數控制等。其工作過程如下:CPU的程序計數器采用順序遞增記數方式,從000H地址開始順序執行,外部ROM中的指令也從000H地址順序存放,而指令也不需要譯碼,是按照指令與存儲地址相對應的方式:地址000H,執行RCR=(000H)h,PSR=(000H)l;地址001H到400H,存放預設的頻點值表,執行PAR=(abcH)h,PBR=(abcH)l,其中(xxxH)h和(xxxH)l分別表示xxxH中存儲數據的高4位和低4位,abcH表示當前執行的001H到3FFH中的某個地址。程序順序執行到3FFH后,自動返回到001H地址循環執行。如果沒有1023個頻點,在最后一個頻點以后的地址全存入FFH即可,當程序運行到內容為FFH的地址時就不進行任何操作而立即返回到001H地址繼續循環執行。

讀外部程序存儲器控制部分采用一個10位的加法計數器,形成順序遞增的10位地址。同時還應有讀使能read,并即時處理程序運行控制信號即鎖定信號stop,當stop信號有效(低電平)時,頻率合成器的輸出鎖定在當前的頻點。模塊還包括 10根地址總線,8根數據總線。程序執行控制部分通過當前地址給相應的寄存器賦值,產生不同的分頻值。

仿真時采用Verilog HDL編寫了一個預存數據的外部ROM仿真模塊,用來對CPU進行仿真,程序如下:

module rom(_read,address,data);

input _read;

input [9:0] address;

output [7:0] data;

reg [7:0] data;

always @ (_read or address)

if(_read)

data《=8‘bzzzzzzzz;

else

case(address)

10’h000:data《=8‘ha8;

10’h001:data《=8‘h91;

…………………

10’h3fe:data《=8‘h87;

10’h3ff:data《=8‘h65;

endcase

endmodule

圖10、11是其仿真波形。圖中reset為復位信號;stop為鎖定信號;clk為CPU的外部時鐘;clk1是clk的2分頻信號為CPU讀取數據,產生地址等提供時鐘;read也是clk的2分頻信號(相位和clk1相差π/2),為外部ROM提供讀使能,同時為CPU提供寄存器控制的時鐘;address為外部ROM地址總線;rom.data[7..0]為外部ROM送出的數據。

責任編輯:gt

電子發燒友App

電子發燒友App

評論