眾所周知,以太網已經深入我們的生活無處不在,企業、校園、大數據中心和家庭等都離不開網絡,否則我們的生活將受到嚴重的影響。

以太網的接口速率也是迅速發展:10M、100M、GE、10GE、40GE、100GE,到目前逐步成熟的2.5GE、5GE、25GE、50GE甚至400GE,基本是每10年速率10倍增長的發展趨勢。

很多數據中心和運營商也已準備將其網絡從100GE擴展到400GE,以支持第五代無線技術(5G)、人工智能(AI)、虛擬現實(VR)、物聯網(IoT)、自動駕駛汽車等新興技術所需的帶寬和響應時間。

然而任何新型網絡接口速率、網絡設備的研發至形成最終產品及網絡新技術從研究到落地,每個階段都離不開測試驗證,而且已經給測試帶來了極大的挑戰。同時,高性能的穩定的高速率網絡測試儀的發展,卻有點跟不上網絡設備的研發需求。

所以高速率、穩定的網絡測試儀的發展刻不容緩,尤其是掌握核心技術的國產化網絡測試儀產品。

國內電信運營商進行的大規模的數據中心交換機或是核心路由器的測試場景對測試儀提出了極高的要求。

1、穩定性

具備長時間穩定打流、統計及協議仿真的能力,如7x24小時長時間穩定運行;

2、可重復性

同樣的物理環境及網絡條件,多次測試結果必須一致;

3、準確性

測試結果必須能準確的反映被測設備或系統的真實指標情況,如吞吐量指標、時延和抖動的精確性、流量調度的精確性、流量統計的精確性;

4、高性能

支持所有包長(如64-16000字節或IMIX混合包長)線速發流及統計的能力、超高的路由交換協議仿真能力(如多session數的BGP/OSPF/ISIS/PPPOE/IPOE/EVPN等)、多端口(如上百個以上的100GE/10GE)多業務(如IPV4/IPV6/MPLS/Multicast)流量場景仿真能力;

5、標準性

具備符合國際測試標準RFC-2544,RFC-2889、RFC3511、RFC3918等;

6、豐富的接口類型

支持1GE/2.5GE/5GE/10GE/25GE/40GE/50GE/100GE/400GE等多種接口類型,支持多機框級聯搭建大規模的測試場景。

而目前市面上存在的網絡測試儀主要有兩種架構。

1、基于x86+DPDK+網卡的測試儀

X86的編程相對容易,調試手段更加豐富,成本有一定的優勢,在要求不高的功能性測試方面,是一個不錯的選擇。

2、基于FPGA+x86混合的測試儀

FPGA+x86這樣的軟硬集合的測試系統,則適用于高性能、全覆蓋、測試場景規模大、測試業務復雜的測試場景。

FPGA+x86的混合架構,一方面利用了FPGA越來越強大的數據層面硬件的并行性,另一方面也結合了CPU在控制層面的處理靈活性,同時由于FPGA和CPU本質上都是可編程的系統,根據業務處理的需要,可以在FPGA硬件和CPU軟件之間靈活地移動業務劃分邊界,實現整個業務流程的全面優化。

我們按照前面所說的電信運營商的復雜測試場景要求,對兩種架構的測試儀進行一個全面的對比分析如下:

1、64-16000字節包長的線速發流及統計能力

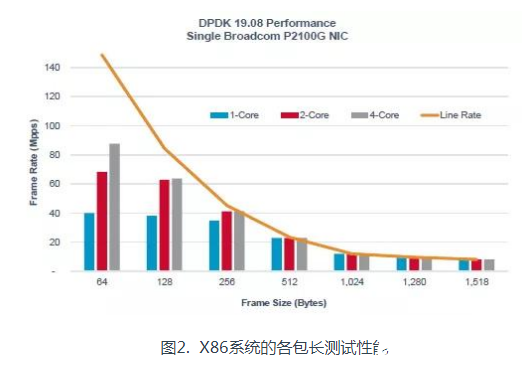

x86+DPDK+網卡:以圖示的100G網絡為例,在64字節包長的情況下,大概每秒會收發150M個數據包,以目前的CPU的計算和存儲存取能力是無法處理的,而基于FPGA架構的測試儀沒有此限制。根據DPDK官網公開發布的最新數據(2019.10.9)【數據來源,DPDK官網 www.dpdk.org】,采用圖1的系統配置,可以明顯看出在64,128,256等小字節情況下無法做到100G線速收發包;

FPGA+x86:所有字節可以做到線速發包與統計。

所能達到的小字節包長線速性能如圖2所示。

2、時延和抖動的精確性

時延測試的精度在網絡測試中是非常重要的指標。

x86+DPDK+網卡:X86系統是面向通用計算的系統,它本身的基準時鐘精度就不高,同時OS的調度誤差至少在us量級;如果x86系統的NIC不支持在物理層插入時間戳的話,需要由軟件系統來處理網絡時延,這將帶來進一步的誤差;所以通常網絡測試需要的精確至10ns量級的時延難以在面向計算的通用x86平臺上實現;

FPGA+x86:在FPGA平臺上,通過0.1~0.001PPM精度的晶振,產生高達400M的時鐘,可以將時延的精度控制在2.5ns數量級別。

3、存儲系統靈活性

x86+DPDK+網卡:x86系統面向通用計算,目前主流的內存系統是DDR4內存,帶寬大但是訪問延遲也大,根據讀寫訪問模式的不同,可能會帶有延遲抖動;

FPGA+x86:FPGA的內存,可以根據需要組合片上RAM(可以實現cache功能)+DDR+QDR+RLDRAM等各種內存技術,優化帶寬需求型和延遲需求型訪問。

4、協議加速的能力

x86+DPDK+網卡:無額外資源來實現TCP offloading等協議加速功能;

FPGA+x86:FPGA是硬件的可編程系統,可以根據硬件資源的多少,以及業務處理的需要,在協議處理方面和x86系統靈活地劃分接口界限,實現TCP offloading等協議加速功能,把協議處理中的計算密集型的無狀態任務在硬件層面并行化,可以大大增強整個系統的處理能力。

5、2-3層流量調度的精確性

x86+DPDK+網卡:x86系統在高速端口上無法實現小字節包長線速發流,更談不上精準的流量調度了;

FPGA+x86:面對測試業務流量越來越復雜和規模越來越大的交換機、路由器,FPGA系統架構下支持產生成千上萬條流(比如高端測試儀中典型的64K條流),并且可以對每條流之間的帶寬比例、發送調度模式做到精確控制,甚至精確到小數點后面5位。

6、統計的實時性能和準確性

x86+DPDK+網卡:CPU的測試功能軟件實現本質上是一個串行的指令集合,隨著多核的超線程等新技術的實現,在指令級別可以實現部分的并行,但是對于一些統計數據,比如實時的每秒收發幀數等,至少是由兩個參數來定義的(一定的時間間隔delta和該間隔內的收發包數),若是這兩個參數的讀取是在一個CPU內核上實現的,則指令的串行特性必然帶來很大的誤差;若是這兩個參數的讀取是在兩個內核上實現的,則目前的CPU技術難以實現內核之間ns級別的同步,同樣帶來統計值的不精確;

FPGA+x86: FPGA內部,通過硬件編程技術,可以很輕松地實現統計值快照功能,嚴格保證上述兩個參數的讀取是精確對應的。

7、系統可擴展性

x86+DPDK+網卡:對于大規模的被測系統,無論是x86的軟件實現還是FPGA+X86這樣的混合系統,單機都無法完成測試任務,系統級聯并且在10ns級別實現同步是必然的選項。x86系統面向通用計算,可以通過運行NTP的協議可以實現多機同步,但是NTP的同步精度無法達到時延測試業務的要求;

FPGA+x86:在FPGA+x86的混合系統中,通過FPGA可以實現本地線纜級聯/GPS/1588v2等高精度同步技術,保證時間測試精度。

另外,在FPGA+x86混合系統的實現中,2-3層的流量處理在FPGA內實現,不需要經過CPU的協議棧或者上層應用,CPU只需實現輕量級的配置下發、界面呈現等運算,避免了CPU在線速收發流處理方面的天然缺陷;在X86一側,也可以靈活部署DPDK技術,由X86系統實現經過加速后的純協議處理部分,將FPGA和x86的優勢組合起來,實現高效的業務處理。

顯而易見,采用FPGA+x86混合系統是構建高性能網絡測試儀的最佳選擇。

近年來,國外以太網測試技術發展迅速,新產品層出不窮,高速率高性能測試軟硬件平臺憑借多年的技術積累,美國的Spirent、keysight兩家公司在以太網測試領域長期占據全球主導地位,在本行業內走在世界前列。

國內對以太網測試技術的研究始于21世紀初,經過十幾年的努力,相關測試產品的自主設計開發能力也取得了長足進步。

信而泰自2007年成立以來,作為國內始終專注于通信網絡測試領域的儀表廠商,堅持國產自主研發的創新機制,研發覆蓋了高中低端市場的多款網絡測試設備產品,客戶已經覆蓋電信運營商、通信制造企業、科研院所、高等院校、電力、交通等眾多領域。信而泰網絡測試儀采用的是機箱式結構+可插拔板卡的形式,硬件總體方案采用分布式計算架構,在邏輯上分為數據平面和管理平面,在物理單元上將測試模塊和主控模塊獨立設計,使用FPGA+x86混合系統的架構來實現高性能網絡測試儀的目標。

電子發燒友App

電子發燒友App

評論