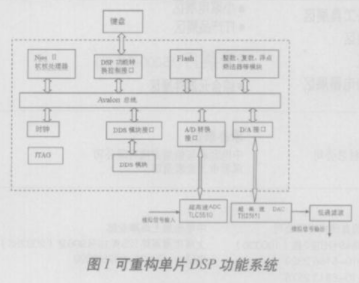

本文主要搭建一個(gè)多生理參數(shù)測(cè)量系統(tǒng)的數(shù)據(jù)處理平臺(tái),在FPGA中嵌入一個(gè)32位Nios II軟核處理器,用于控制數(shù)據(jù)的傳輸、存儲(chǔ)及顯示。主要完成了此數(shù)據(jù)處理平臺(tái)硬件系統(tǒng)的定

2010-08-18 12:10:44 933

933

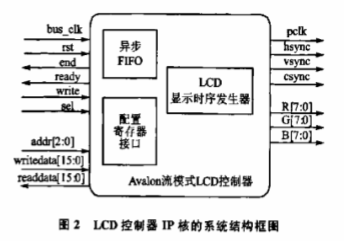

本文介紹了一種基于NIOS II軟核處理器實(shí)現(xiàn)對(duì)LCD-LQ057Q3DC02控制的新方法。在設(shè)計(jì)中利用FPGA的Altera的SOPC Builder定制NIOS II軟核處理器及其與顯示功能相關(guān)的“軟” 硬件模塊來協(xié)同實(shí)現(xiàn)顯示控

2011-11-09 11:30:07 2000

2000

儀器、儀表和低功耗電子產(chǎn)品中。本文介紹一種基于NIOSⅡ的LCD的控制方法。利用SoPC技術(shù),在NIOSⅡ系統(tǒng)中添加相應(yīng)的I/O端口實(shí)現(xiàn)對(duì)液晶顯示器的控制。

2018-10-31 08:04:00 3719

3719

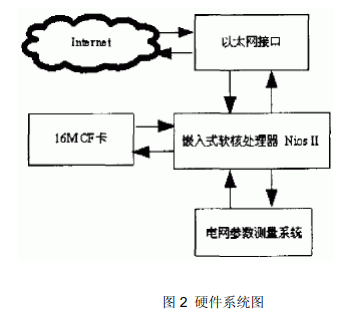

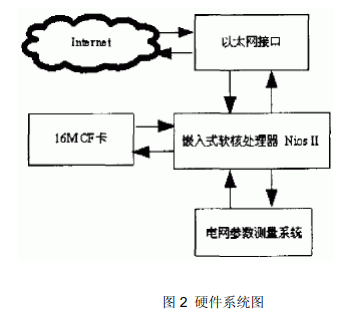

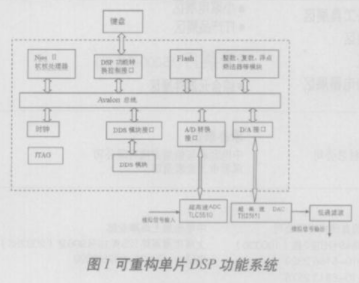

系統(tǒng)的硬件結(jié)構(gòu)如圖2所示。硬件系統(tǒng)的核心是構(gòu)建于Ahera Cyclone FPGA中的Nios II嵌入式軟核處理器。Nios II系列嵌入式處理器是一款通用的RISC結(jié)構(gòu)的CPU,它定位于廣泛

2020-06-28 14:49:45 540

540

基于μC/OS-II實(shí)時(shí)操作系統(tǒng)實(shí)現(xiàn)多任務(wù)管理運(yùn)行模式,采用Nios II 32位處理器作為LED顯示屏控制系統(tǒng)的核心,控制單屏幕多窗口任意顯示。整個(gè)控制系統(tǒng)在一片F(xiàn)PGA上實(shí)現(xiàn),使用SOPC Builder軟

2011-10-02 16:00:21 2366

2366 。 基于NIOSⅡ的矩陣鍵盤和液晶顯示外設(shè)組件的設(shè)計(jì) 本文提出了一種針對(duì)LCD控制器和矩陣鍵盤的IP核的設(shè)計(jì)方法。該方法利用SOPC Builder中元件編輯器Create New

2015-01-16 22:10:42

,國際上只有I-Shou大學(xué)的Yu-Jung Huang等人設(shè)計(jì)了可驅(qū)動(dòng)不同規(guī)模LCD的驅(qū)動(dòng)電路IP核,通過在系統(tǒng)中植入嵌入式微處理器來實(shí)現(xiàn)這一功能。但是,這種嵌入式微處理器使系統(tǒng)更復(fù)雜,而且成本更高

2012-08-12 12:28:42

NIOS II 軟核中EPCS配置芯片的存儲(chǔ)操作 最近用CYCLONE FPGA做的視頻圖像疊加板需要存儲(chǔ)一些用戶配置信息,而EPCS4配置芯片除了存儲(chǔ)FPGA配置信息和NIOS II程序外,還有

2018-07-05 05:58:25

表1 Nios II處理器系統(tǒng)的最大時(shí)鐘頻率(tMAX)(MHz)表2 Nios II處理器系統(tǒng)的MIPS(每秒鐘一百萬個(gè)指令) 表3 在不同設(shè)備家族上的Nios II處理器系統(tǒng)的MIPS/MHz比

2018-07-03 02:30:47

問一個(gè)問題,為什么配置的PLL的IP核,如圖,紅框的那個(gè)接了輸入,在NIOS II中就會(huì)出現(xiàn) [Target Connection]: Connected system ID hash

2016-10-04 21:05:25

,浪費(fèi)生命。NIOS內(nèi)核的裁剪問題,編譯出來的文件過大,導(dǎo)致Quartus_II軟件構(gòu)造好的on chip memory下載不進(jìn)去,顯示下載elf文件失敗elf文件下載失敗還有可能與你使用的IP核有關(guān)

2017-05-30 14:03:44

個(gè)最小系統(tǒng)僅僅需要:1、NIOS II f 或者s 處理器,帶硬件乘法器(建議使用NIOS II /f,使用NIOS II/s很慢)2、最小8M的SDRAM3、一個(gè)全功能的定時(shí)器4、JTAG/UART

2012-02-21 15:55:21

如何與AD采集融合。 查詢了一下,發(fā)現(xiàn)可以使用Avalon總線,將AD的verilog功能描述封裝成一個(gè)IP核,掛到Avalon總線,實(shí)現(xiàn)verilog與NIOS II的通訊。 但是不知道這種方法速度夠不夠

2017-11-21 10:11:22

nios ii雙核例子nios ii雙核例子NIOS II 雙核構(gòu)建的簡(jiǎn)單例子,希望對(duì)大家有所幫助。 1、 實(shí)現(xiàn)簡(jiǎn)易功能 Cpu_0控制pio_cpu_0(輸出),令其輸出為1。此輸出和cpu_1

2012-08-12 15:18:48

可以移植到不同的半導(dǎo)體工藝中去生產(chǎn)集成電路芯片。隨著CPLD/FPGA的規(guī)模越來越大,設(shè)計(jì)越來越復(fù)雜,使用IP核是一個(gè)趨勢(shì)。 本文研究了ATM流量控制的原理,并給出了一種IP核的實(shí)現(xiàn)方法,該IP核不僅可以用于獨(dú)立芯片,還可以作為系統(tǒng)的一個(gè)子模塊直接調(diào)用。

2011-09-27 11:54:25

用Quartus II 調(diào)用IP核時(shí),在哪可以查看IP核的例程

2014-07-27 20:28:04

CAN控制器IP核(可直接在Nios II中使用)

2016-08-24 16:54:21

在其業(yè)內(nèi)領(lǐng)先的低成本Cyclone TM FPGA系列和Nios軟核嵌入式處理器成功的基礎(chǔ)上,Altera現(xiàn)在推出了第二代產(chǎn)品系列。Cyclone II器件為用戶提供更高的邏輯密度和新增硬件性能,比

2019-07-18 07:43:25

FPGA是現(xiàn)場(chǎng)可編程門陣列,是可編程邏輯器件(PLD)的一種。 NIOS II是一種知識(shí)產(chǎn)權(quán)核(IP Core),是嵌在FPGA內(nèi)部的處理器軟核,相當(dāng)于在FPGA內(nèi)部設(shè)計(jì)了一個(gè)微處理器

2018-08-17 09:59:27

的SOPC系統(tǒng)中設(shè)計(jì)了LCD顯示驅(qū)動(dòng)IP核,并下載到Cyclone系列的FPGA中,實(shí)現(xiàn)了對(duì)LCD的顯示驅(qū)動(dòng)。

2019-08-06 08:29:14

很多人都說QUARYUSII中的IP核是收費(fèi)的,不可以直接用的,其實(shí)不然,下面我以FIR濾波器的核的使用來給大家介紹IP核的使用,希望對(duì)大家有點(diǎn)幫助。 1.使用 (1)首先建立工程,這個(gè)就不

2019-06-03 09:09:51

如題:我之前用Quartus ii 13創(chuàng)建的工程。現(xiàn)在改用17了。想編輯以前的IP核但是找不到MegaWizard Plug-In Manager 了

2017-09-24 21:06:09

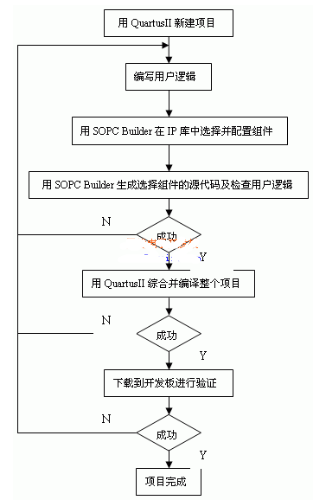

關(guān)于QuartusⅡ10.1中NIOS2軟核的構(gòu)建、軟件編譯及程序固化 一、硬件開發(fā)1、構(gòu)建CPU模塊2、構(gòu)建EPCS控制器,SYSTEM ID模塊,JTAG UART模塊3、構(gòu)建RAM模塊(1

2022-01-25 07:58:08

LCD上顯示,并可通過USB接口將信息拷貝,或通過RS-232接口將信息上傳給PC機(jī),也可以通過GPRS將獲得的信息方便快捷地發(fā)往數(shù)據(jù)中心作驗(yàn)證。 整個(gè)系統(tǒng)的核心部分是內(nèi)嵌Nios II軟核

2018-10-31 16:54:52

用戶是可自定制的,具有靈活性和可裁減性等優(yōu)點(diǎn)。結(jié)合內(nèi)河航道航標(biāo)管理的實(shí)際情況,介紹了一種新的基于Nios II軟核的航標(biāo)監(jiān)控系統(tǒng)的設(shè)計(jì)方案。根據(jù)系統(tǒng)的運(yùn)行結(jié)果顯示,設(shè)計(jì)實(shí)現(xiàn)了系統(tǒng)預(yù)期功能,為監(jiān)控中心能

2015-01-30 11:05:50

基于Qsys + Nios II SBT開發(fā)的Nios II教程,內(nèi)容詳細(xì),學(xué)習(xí)NiosII的同學(xué)可以關(guān)注下~點(diǎn)擊下載

2014-10-13 18:17:58

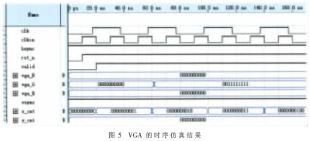

24M的時(shí)鐘信號(hào),供640*480分辨率的VGA驅(qū)動(dòng)電路使用。NIOS II CPU:實(shí)現(xiàn)系統(tǒng)的控制以及顯示內(nèi)容的處理。SDRAM:NIOS II CPU運(yùn)行內(nèi)存和TFT顯示圖像幀緩存

2020-02-26 19:37:23

SPI、定時(shí)器、UART串口等IP核,只要在Qsys中添加好這些IP,然后在NIOS II的開發(fā)環(huán)境(定制版Eclipse)中編寫驅(qū)動(dòng)程序和應(yīng)用程序即可完成該控制器的使用。當(dāng)然,為了讓這些IP用起來

2020-02-24 19:27:02

`附件為小梅哥SOPC公開課第二課NIOS II自定義IP的設(shè)計(jì)與使用的建隨堂工程。小梅哥SOPC公開課第二課主要講解如何使用Verilog自己編寫一個(gè)符合NIOS II Avalon MM接口總線

2016-08-13 11:04:32

內(nèi)部中斷需要具備以下幾個(gè)條件:(1)Status控制寄存器中的PIE位為1; (2)某個(gè)中斷請(qǐng)求irqn有效;(3)在ienable寄存器中,該中斷源相應(yīng)位為1 當(dāng)內(nèi)部中斷發(fā)生后,Nios II處理器會(huì)

2016-10-21 18:31:59

,近期主要深入學(xué)習(xí)了Qsys系統(tǒng)的硬件部分和軟件部分,首先學(xué)習(xí)了Nios II的硬件框架結(jié)構(gòu),收獲頗豐。 下圖是Qsys的系統(tǒng)結(jié)構(gòu)框圖: 圖中主要包括Nios II軟核處理器和UART、SPI、定制外設(shè)

2016-10-21 16:47:44

FPGA學(xué)習(xí)嵌入式硬件最小系統(tǒng)搭建(一)(NIOS II處理器設(shè)置)本期學(xué)習(xí)目的:利用NIOS II系統(tǒng)點(diǎn)亮LCD1602屏及5.7寸LCD(8080接口)。前言概述上篇文章介紹了嵌入式硬件系統(tǒng)概述

2021-12-20 07:02:02

收到遠(yuǎn)端的信號(hào),進(jìn)行解調(diào)解擴(kuò)并傳給網(wǎng)絡(luò),完成接收部分。其中一個(gè)NIOS II 核完成無線收發(fā)機(jī)接收和發(fā)送的信號(hào)處理和運(yùn)算,另一個(gè)核運(yùn)行操作系統(tǒng),完成以太網(wǎng)傳輸和其他相關(guān)控制。之所以選擇使用NIOS

2009-10-06 15:05:24

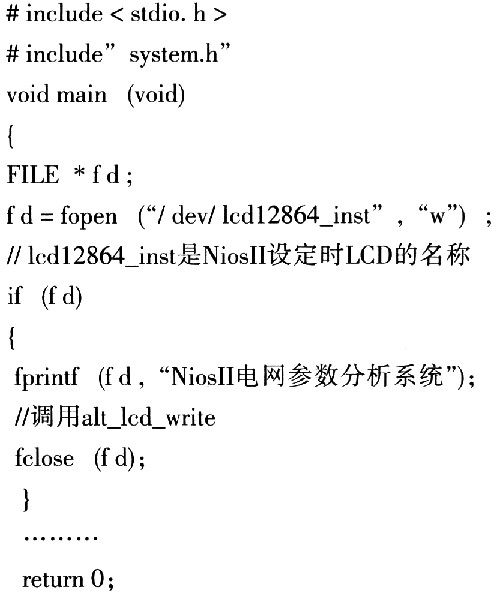

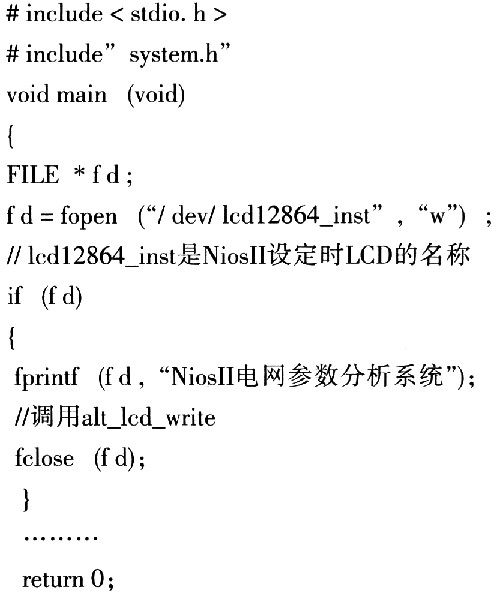

的程序設(shè)計(jì)在NiosⅡ和LCD的接口中,一方面可以通過在NiosⅡ系統(tǒng)中添加相應(yīng)I/O口的方式來實(shí)現(xiàn)對(duì)液晶顯示屏LCD的間接控制,另一方面也可以利用構(gòu)建IP核來直接進(jìn)行控制。第一種是將LCD接口當(dāng)作普通

2018-12-11 11:08:10

II軟核來完成,Nios II處理器將片上存儲(chǔ)器中的數(shù)據(jù)逐一讀取并進(jìn)行處理之后顯示在LCD上,Avalon總線負(fù)責(zé)各個(gè)控制器模塊的數(shù)據(jù)傳輸。FPGA選用Altera公司的EP3C5E144C8。1.2

2019-06-03 05:00:06

II CPU如圖4所示。4 系統(tǒng)實(shí)現(xiàn)啟動(dòng)Nios II IDE環(huán)境下,創(chuàng)建系統(tǒng)軟件控制部分后,運(yùn)行程序即可采集指紋圖像,本系統(tǒng)環(huán)境下采集的指紋圖像5所示。圖6為作參考比較的光學(xué)采集指紋圖像,指紋圖

2019-04-29 07:00:08

、NiosII實(shí)現(xiàn)hello world1.1硬件設(shè)計(jì)芯片選擇如下設(shè)置系統(tǒng)時(shí)鐘,Tools -> Qsys添加Nios II Processor在搜索框中,輸入nio,找到Nios II Processor,點(diǎn)擊Add,最后保存即可添加On_Chip Memory在搜索框中,輸入on_ch

2021-12-27 08:13:55

基于NioslI的SOPC系統(tǒng)中設(shè)計(jì)了LCD顯示驅(qū)動(dòng)IP核,并下載到Cyclone系列的FPGA中,實(shí)現(xiàn)了對(duì)LCD的顯示驅(qū)動(dòng)。

2019-11-04 08:18:58

信息顯示在LCD液晶顯示屏上。各硬件模塊之間的協(xié)調(diào)工作通過嵌入式軟核處理器NiosⅡ用編程實(shí)現(xiàn)控制。本設(shè)計(jì)所搭建的LCD12864控制器是通過編程實(shí)現(xiàn)的IP核。關(guān)鍵詞:DDS;FPGA技術(shù);順序存儲(chǔ);NiosⅡ;IP核

2019-06-21 07:10:53

任務(wù)需求來定制顯示控制功能,可以增強(qiáng)系統(tǒng)可靠性和設(shè)計(jì)靈活性,降低了成本。目前針對(duì)LCD 顯示屏設(shè)計(jì)的控制器IP 核文章較多[1-2],但對(duì)于TFT-LCD 觸控屏設(shè)計(jì)的控制器IP 核文章較少[3],而且

2018-11-07 15:59:27

實(shí)例精煉》第四章_VHDL的數(shù)據(jù)類型.avihttp://115.com/file/e7wpz111#《基于VHDL的FPGA與NIOS_II實(shí)例精煉》第十四章_字符型LCD的顯示控制.avihttp

2012-02-06 11:22:55

驗(yàn)證的IP模塊。參考演示包括將系統(tǒng)編程為具有墻壁和邊緣避免以及同步運(yùn)動(dòng)的自主車輛。簡(jiǎn)單的PID控制將用于影響直流電機(jī)的速度和位置。步進(jìn)電機(jī)將基于全步,半步和微步模式進(jìn)行控制。附錄中包含最終演示,用于監(jiān)控電池系統(tǒng)中剩余的電量并在LCD上顯示該值

2020-05-19 09:30:50

,LCD液晶顯示器憑借功耗低、體積小、輕薄及控制驅(qū)動(dòng)簡(jiǎn)單等特點(diǎn),在智能儀器、儀表和低功耗電子產(chǎn)品中得到了廣泛應(yīng)用。以深圳秋田視佳實(shí)業(yè)有限公司的液晶顯示模塊CBGl28064為例,告訴大家, 如何在SOPC的NiosII中設(shè)計(jì)LCD顯示驅(qū)動(dòng)IP核?實(shí)現(xiàn)了對(duì)LCD的顯示驅(qū)動(dòng)。

2019-08-05 07:56:59

時(shí),Builder開發(fā)工具中沒有提供現(xiàn)成的數(shù)碼管顯示IP核,這使設(shè)計(jì)者工作量增加。這里把數(shù)碼管控制器設(shè)計(jì)為一個(gè)共陰極(或共陽極)7段數(shù)碼管動(dòng)態(tài)顯示IP核,并給出此核的一個(gè)參考驅(qū)動(dòng)程序。

2019-08-09 06:09:05

Altera公司的FPGA作為全定制芯片的一個(gè)代表正在得到日益廣泛的應(yīng)用。為了用戶使用方便,Altera公司推出嵌入式軟核NiosⅡ可以便利地使用工具生成并放人FPGA芯片中。NiosⅡ軟核可以在用

2019-10-25 07:25:38

怎么實(shí)現(xiàn)基于Nios II DTMB單頻網(wǎng)適配器的設(shè)計(jì)?

2021-05-31 07:01:29

介紹如何在Altera開發(fā)平臺(tái)上,使用Nios軟核CPU來構(gòu)建嵌入式Internet系統(tǒng);并結(jié)合以太網(wǎng)遠(yuǎn)程數(shù)據(jù)采集系統(tǒng)的實(shí)例,介紹此類系統(tǒng)硬件,軟件的設(shè)計(jì)方法。

2021-06-04 07:05:47

本文以 640*480的數(shù)字輸入的 TFT-LCD顯示屏為例,介紹了一種基于 NiosⅡ軟核處理器實(shí)現(xiàn)對(duì) TFT-LCD接口的方法。解決了通常情況下必須使用LCD 控制專用芯片才能解決 LCD顯示的問題。

2021-06-08 06:46:33

是不是所有的cyclone IV系列的芯片都支持nios II軟核

2014-08-13 10:34:55

本文設(shè)計(jì)了一種在多處理器系統(tǒng)中的Nios II軟核處理器的啟動(dòng)方案,這個(gè)方案在外部處理器向Nios II的程序存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器加載數(shù)據(jù)時(shí),可以控制Nios II處理器的啟動(dòng)。

2021-04-27 06:52:42

求大神給幾個(gè)VHDL寫的基于NIOS IIIP核源碼,簡(jiǎn)單的就行,比如IIC AD什么的,多謝

2016-04-11 21:19:33

建立NIOS_Helloworld工程,進(jìn)行IP核連線的時(shí)候,NIOS的jtag_reset信號(hào)如何與jtag_uart進(jìn)行連接?

在原子哥的文檔中對(duì)這步的操作在下面,

上面是文檔中對(duì)連接方法的描述,但是我的qsys中在IRQ欄好像沒有進(jìn)行連接的按鈕

請(qǐng)問軟件是如何操作的?

2019-05-15 06:35:26

片上Nios Ⅱ嵌入式軟核多處理器系統(tǒng)具有哪些優(yōu)勢(shì)?如何實(shí)現(xiàn)片上嵌入式Nios Ⅱ軟核六處理器系統(tǒng)的設(shè)計(jì)?

2021-04-19 08:17:09

請(qǐng)問怎么去控制qsys搭建的SDRAM這個(gè)ip核,因?yàn)橄氚岩粋€(gè)ram核當(dāng)作一個(gè)外部AD數(shù)據(jù)的存儲(chǔ)器,將外部數(shù)據(jù)存儲(chǔ)起來,再用nios通過API函數(shù)讀出來作顯示,現(xiàn)在就是不知道怎么去去操作這個(gè)IP核

2019-08-25 17:35:20

、編譯和調(diào)試程序。Nios II IDE提供了一個(gè)統(tǒng)一的開發(fā)平臺(tái),用于所有Nios II處理器系統(tǒng)。僅僅通過一臺(tái)PC機(jī)、一片Altera的FPGA以及一根JTAG下載電纜,軟件開發(fā)人員就能夠往Nios

2015-09-08 22:35:45

II軟核,可以直接放在FPGA中,它體現(xiàn)了把實(shí)現(xiàn)產(chǎn)品的全部單元電路集成到一個(gè)芯片之內(nèi)的片上系統(tǒng)SOPC的思想。作為一種具有競(jìng)爭(zhēng)力的技術(shù),在國外已經(jīng)有大量的產(chǎn)品使用了這種技術(shù),在國內(nèi)使用Nios II

2019-05-29 05:00:04

4為UPFC控制器IP核輸出的實(shí)際波形圖。4 結(jié)束語本UPFC控制器IP能使輸出正弦波頻率跟電網(wǎng)頻率保持一致,且輸出正弦波的幅值和相位可根據(jù)需要進(jìn)行調(diào)節(jié);輸出的三角載波的頻率、幅值和相位保持不變。同時(shí),將UPFC控制器IP核和Nios II相結(jié)合還可提高系統(tǒng)的抗干擾能力。

2019-06-03 05:00:05

Nios II 軟件開發(fā)參考手冊(cè)

Nios II 軟件開發(fā)參考手冊(cè)

Nios II 軟件開發(fā)參考手冊(cè)

2007-06-05 18:56:43 120

120 首先介紹嵌入式實(shí)時(shí)操作系統(tǒng)μC/OS-II 和Nios 嵌入式處理器, 分析μC/OS-II 移植對(duì)目標(biāo)處理器的要求, 重點(diǎn)介紹μC/OS-II 在Nios 處理器上的移植過程,最后在Nios 開發(fā)板上對(duì)移植工

2011-03-08 09:31:38 90

90 首先介紹嵌入式實(shí)時(shí)操作系統(tǒng)μC/OS-II 和Nios 嵌入式處理器, 分析μC/OS-II 移植對(duì)目標(biāo)處理器的要求, 重點(diǎn)介紹μC/OS-II 在Nios 處理器上的移植過程,最后在Nios 開發(fā)板上對(duì)移植工作進(jìn)行

2009-05-16 14:32:43 28

28 基于Nios II的自動(dòng)指紋識(shí)別系統(tǒng)設(shè)計(jì):介紹基于Nios II處理器的嵌入式自動(dòng)指紋識(shí)別系統(tǒng)的實(shí)現(xiàn)方法;具體說明自動(dòng)指紋識(shí)別系統(tǒng)的基本原理、系統(tǒng)總體結(jié)構(gòu)、硬件結(jié)構(gòu)設(shè)計(jì)、用戶自定

2009-06-25 08:16:23 22

22 介紹了基于NIOS II 軟核處理器的SOPC 技術(shù),分析了傳統(tǒng)方法和基于SOPC 技術(shù)的方法實(shí)現(xiàn)擴(kuò)頻收發(fā)機(jī)的優(yōu)劣,詳細(xì)說明了嵌有雙NIOS II 的SOPC 技術(shù)的方案設(shè)計(jì)。該設(shè)計(jì)增強(qiáng)了系統(tǒng)功能,改善

2009-07-22 15:35:35 0

0 介紹了一種新的基于NIOS II的導(dǎo)航系統(tǒng)的設(shè)計(jì)方案. NIOS是建立在FPGA 上的嵌入式微處理器軟核, 由于它硬件設(shè)計(jì)上的靈活性和可裁減性,使得軟件設(shè)計(jì)上“平臺(tái)”的概念延伸到硬件設(shè)計(jì)

2009-08-05 11:05:00 20

20 本文以Nios II 嵌入式軟處理器為核心,利用USB 控制芯片CH372,設(shè)計(jì)了基于Nios II 嵌入式軟處理器的USB 通信接口。本文重點(diǎn)介紹了USB 接口的硬件實(shí)現(xiàn)方案,分析了CH372 的通信流程,并

2009-08-28 11:34:28 33

33 介紹了基于NIOS II 軟核處理器的SOPC 技術(shù),分析了傳統(tǒng)方法和基于SOPC 技術(shù)的方法實(shí)現(xiàn)擴(kuò)頻收發(fā)機(jī)的優(yōu)劣,詳細(xì)說明了嵌有雙NIOS II 的SOPC 技術(shù)的方案設(shè)計(jì)。該設(shè)計(jì)增強(qiáng)了系統(tǒng)功能,改善

2009-11-27 14:23:43 15

15 為了提高傳統(tǒng)指紋識(shí)別系統(tǒng)處理速度和安全問題,研究一種基于NIOS II 處理器的高速嵌入式指紋識(shí)別系統(tǒng)。利用NIOS II 的定制指令,F(xiàn)PGA 實(shí)現(xiàn)算法的硬件設(shè)計(jì),同時(shí)結(jié)合先進(jìn)的射頻識(shí)

2009-11-30 14:18:01 28

28 在NIOS-II 系統(tǒng)中A/D 數(shù)據(jù)采集接口的設(shè)計(jì)與實(shí)現(xiàn)摘要:進(jìn)行 SOPC 開發(fā),很有必要學(xué)習(xí)一下定制NIOS 外設(shè)的方法和技巧。本文就是基于這種目的,詳細(xì)的論述了在NIOS 系統(tǒng)中A/D 數(shù)據(jù)

2010-02-08 09:55:43 23

23 NIOS II軟核處理器是Altera公司推出的一款靈活高效的嵌入式處理器。該處理器的應(yīng)用常見于控制和通信領(lǐng)域。本文描述了在NIOS II系統(tǒng)上實(shí)現(xiàn)平臺(tái)直方圖均衡算法(Plateau Equalization ,PE)

2010-08-06 15:48:40 24

24 基于Nios-II設(shè)計(jì)和實(shí)現(xiàn)了支持PSTN網(wǎng)絡(luò)、Internet網(wǎng)絡(luò)的雙網(wǎng)傳真機(jī)系統(tǒng),利用FPGA實(shí)現(xiàn)了傳真機(jī)系統(tǒng)的多個(gè)電路模塊,包括A/D采樣控制邏輯、二值化圖像處理模塊、MH編碼模塊、MH譯碼模

2010-09-30 16:33:21 31

31 提出了將Altera公司的Nios II軟核嵌入到FPGA器件內(nèi)部來控制高性能直接數(shù)字頻率合成器AD9858的方法,在簡(jiǎn)要介紹Nios II和AD9858的特性的基礎(chǔ)上,詳細(xì)說明了系統(tǒng)設(shè)計(jì)電路結(jié)構(gòu)和軟件設(shè)計(jì)

2010-12-09 16:23:28 31

31 NIOS II的特性及開發(fā)設(shè)計(jì)流程

NIOS的主要特點(diǎn)NIOS II是一個(gè)用戶可配置的通用RISC嵌入式處理器。Altera推出的NIOS II系列嵌入式處理器擴(kuò)展了目前

2010-02-08 14:47:31 1430

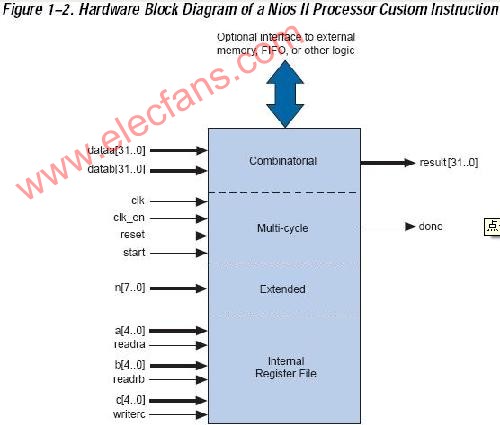

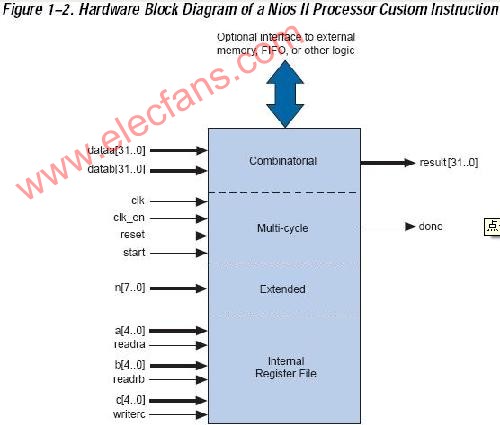

1430 NIOS II前哨計(jì)劃step by step 1(NIOS II用戶指令)

可編程軟核處理器最大的特點(diǎn)是靈活,靈活到我們可以方便的增加指令,這在其他SOC系統(tǒng)中做不到的,增加用戶指令可以把

2010-03-27 09:52:23 1040

1040

基于Nios-II設(shè)計(jì)和實(shí)現(xiàn)了支持PSTN網(wǎng)絡(luò)、Internet網(wǎng)絡(luò)的雙網(wǎng)傳真機(jī)系統(tǒng),利用FPGA實(shí)現(xiàn)了傳真機(jī)系統(tǒng)的多個(gè)電路模塊,包括A/D采樣控制邏輯、二值化圖像處理模塊、MH編碼模塊、MH譯碼模

2010-06-23 11:13:10 1795

1795

0 引言

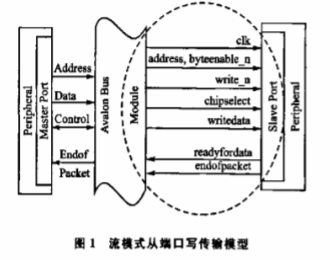

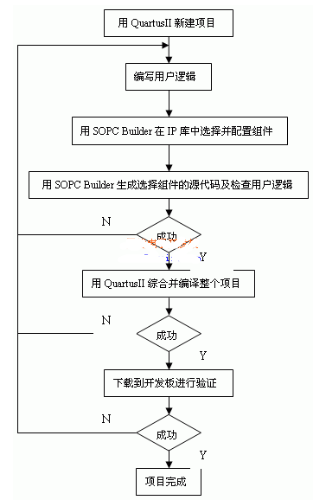

NIOSⅡ是Altera公司推出的第二代IP軟核處理器。它與其他IP核可構(gòu)成SOPC系統(tǒng)的主要部分。Altera SOPC Builder提供有NiosⅡ處理器及一些常用外設(shè)接口,因此,對(duì)于一

2010-08-16 09:44:23 1476

1476

基于Nios II/

2011-01-09 20:59:04 29

29 摘要! 主要闡述了以FPGA為核心的基于NIOS II軟核的嵌入式LCD圖形顯示設(shè)計(jì) 方法$ 從系統(tǒng)的角度提出在LCD上顯示圖形的設(shè)計(jì)過程#給出搭建NIOS II軟核的系統(tǒng)整體結(jié)構(gòu)圖#并 最終實(shí)現(xiàn)了圖形以及漢字在LCD上的顯示最后總結(jié)出利FPGA技術(shù)實(shí)現(xiàn)LCD 圖形顯示的優(yōu)勢(shì)$

2011-02-11 14:17:40 42

42 Nios II內(nèi)核詳細(xì)實(shí)現(xiàn)

2012-10-17 13:59:49 83

83 Nios II 系列處理器配置選項(xiàng):This chapter describes the Nios II Processor parameter editor in Qsys and SOPC

2012-10-17 14:08:42 17

17 Nios II定制指令用戶指南:With the Altera Nios II embedded processor, you as the system designer can

2012-10-17 14:18:49 37

37 使用Nios II緊耦合存儲(chǔ)器教程 Chapter 1. Using Tightly Coupled Memory with the Nios II Processor Reasons

2012-10-17 14:43:25 48

48 怎樣使用Nios II處理器來構(gòu)建多處理器系統(tǒng) Chapter 1. Creating Multiprocessor Nios II Systems Introduction to Nios II

2012-10-17 14:51:06 19

19 電子發(fā)燒友網(wǎng)核心提示 :當(dāng)您采用Nios II 嵌入式處理器進(jìn)行設(shè)計(jì)時(shí),您所使用的將是由Altera及其合作伙伴提供的可靠的軟件開發(fā)工具和軟件組件。 Nios II 嵌入式設(shè)計(jì)包 Nios II嵌入式設(shè)計(jì)

2012-10-17 15:31:13 1704

1704

為了實(shí)現(xiàn)對(duì)嵌入式系統(tǒng)中大量數(shù)據(jù)存儲(chǔ)的需求,提出了一種基于NIOS II的SD卡存儲(chǔ)系統(tǒng)設(shè)計(jì)方案,并完成系統(tǒng)的軟硬件設(shè)計(jì)。該存儲(chǔ)系統(tǒng)使用SPI模式對(duì)SD卡進(jìn)行讀寫訪問,SPI時(shí)序由NIOS II的

2013-07-25 16:19:49 66

66 NIOS II 常見問題總結(jié),如果你想要Altera的FPGA做嵌入式設(shè)計(jì),肯定要涉及到NIOS II的使用,本文總結(jié)了一些NIOS II的常見問題與解決方法

2015-12-01 15:43:34 14

14 在 Nios II 中根據(jù)需求定制基于 Avalon 總線的 IP 核模塊,并使用定制的模

塊實(shí)現(xiàn)對(duì)數(shù)碼管的控制。通過本章,你能學(xué)到

(1)在 Nios II 中定制基于 Avalon 總線的 IP 核模塊。

(2)在 Nios II 中控制數(shù)碼管。

2015-12-14 15:39:39 3

3 NIOS_II各種性能表格對(duì)NIOS_II內(nèi)核在各種型號(hào)的FPGA上的實(shí)現(xiàn)的性能說明

2015-12-21 17:19:15 22

22 介紹Modular Scatter-Gather DMA IP及如何與 Nios II 處理器搭配使用

2018-06-22 09:38:00 3030

3030

本文檔的主要內(nèi)容詳細(xì)介紹的是如何制作一個(gè)方便在Quartus II和Nios II中使用的簡(jiǎn)單IP。

2019-07-09 17:40:00 2

2 隨著電路規(guī)模越來越大,片上系統(tǒng)(SoC)已經(jīng)成為IC設(shè)計(jì)的發(fā)展趨勢(shì),相應(yīng)地也有了更加靈活的片上可編程系統(tǒng)(SOPC)。Nios II CPU是一個(gè)基于流水線設(shè)計(jì)的通用RISC微處理器,擁有五級(jí)流水線

2020-04-11 17:01:12 1353

1353

本文論述了一種基于Nios II的可重構(gòu)DSP系統(tǒng)設(shè)計(jì)。

2021-05-05 03:03:00 982

982

電子發(fā)燒友網(wǎng)站提供《基于NIOS II的SD卡讀寫控制設(shè)計(jì).pdf》資料免費(fèi)下載

2023-11-06 10:06:43 1

1

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論