當今的數字系統往往是圍繞CPLD/ FPGA 進行設計的, 首選的方案是采用同步時序電路設計 , 也稱作單時鐘系統, 電路中所有觸發器的時鐘輸入端共享同一個時鐘, 每個觸發器的狀態變化都是在時鐘的上升沿( 或下降沿) 完成的, 與時鐘脈沖信號同步。

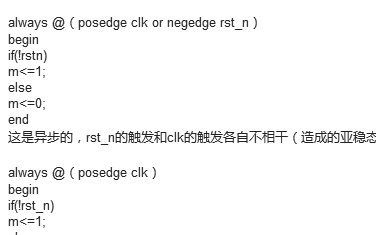

但在實際的工程應用中, 純粹單時鐘系統設計不能完成數據在不同時鐘域間的傳遞, 跨時鐘域的異步時序設計不可避免。異步時序電路中有多個獨立的時鐘源, 不同時鐘源存在頻率和相位的差異, 當數據信號通過兩個時鐘域的交界處時, 將會分別由這兩個時鐘來控制信號的值。此時如果兩時鐘信號的敏感沿非常接近并超過了允許的額度, 則將出現數據信號的不穩定, 即電路陷入亞穩態, 也稱為同步失敗。

異步電路設計的關鍵就是把數據或控制信號正確地進行跨時鐘域傳輸, 同時防止亞穩態的出現。如果對跨時鐘域帶來的亞穩態、采樣丟失等問題處理不當, 將導致系統無法正常運行。

隨著信息技術的飛速發展, 航天航空、軍事應用領域對數據異步傳輸的可靠性提出了更高的要求, 如果不徹底消除亞穩態隱患, 將可能導致災難性的后果。

1、 亞穩態的產生

1. 1 單觸發器的亞穩態

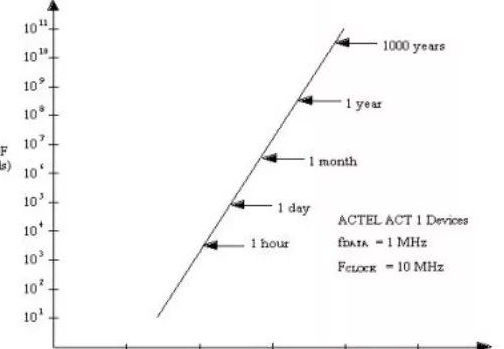

觸發器是數字電路設計中最常用的基本器件, 內部包含兩個雙穩態元件, 其特性曲線如圖1 所示。除了兩個穩定狀態0 和1 外, 還有一個狀態也滿足雙穩態元件的方程,即當兩個反相器都處于中間值的第3 種半穩定態----- 亞穩態, 反相器在非邏輯值范圍的反饋系數是相當大的, 一旦因干擾或噪音離開了這個中心點, 就會很快地進入邏輯值范圍( 穩態) 。

圖1:亞穩態問題

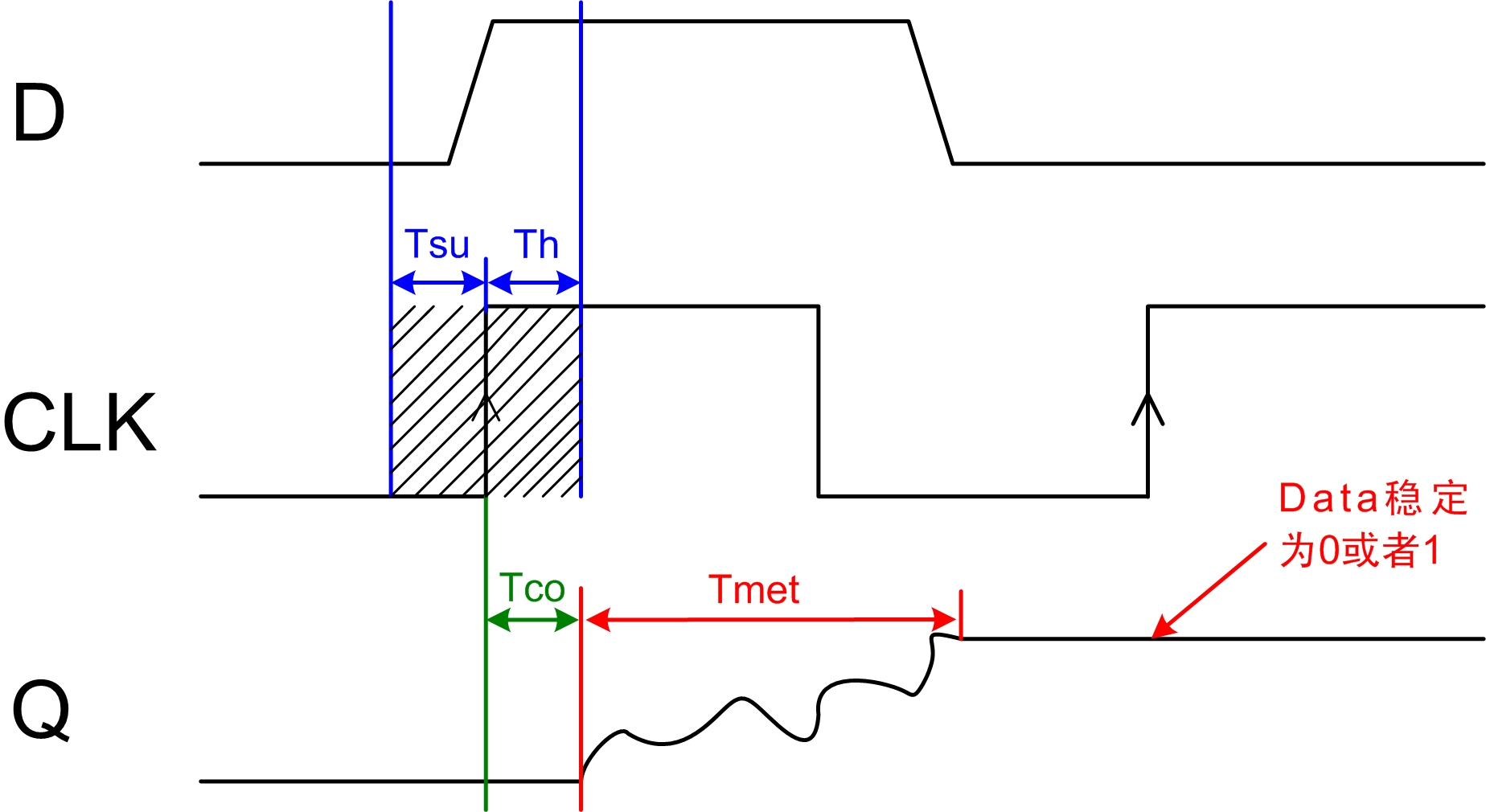

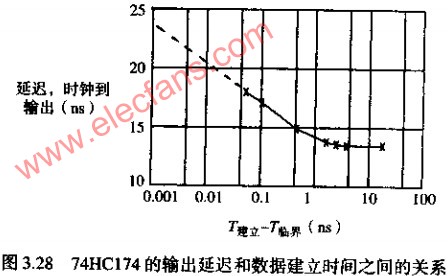

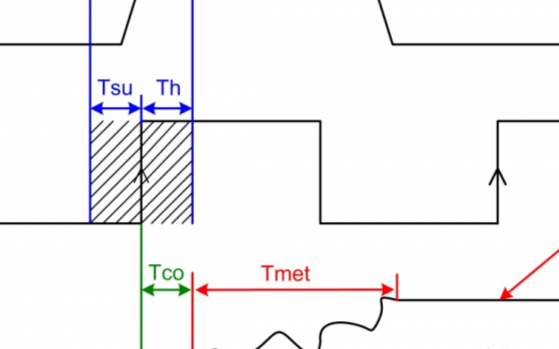

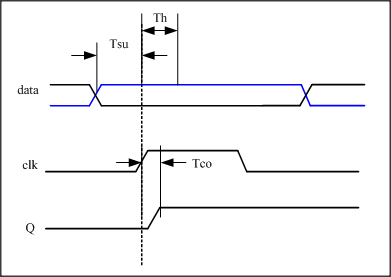

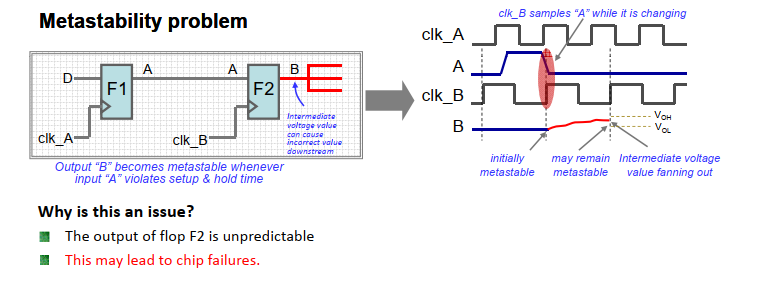

觸發器工作過程中要滿足數據建立( setup ) / 保持( hold) 的時間要求, 輸入信號在時鐘的上升沿前后是不允許發生變化的。對于使用上升沿觸發的觸發器來說,建立時間就是在時鐘上升沿到來之前, 觸發器輸入端數據必須保持穩定不變的最小時間; 而保持時間是時鐘上升沿到來之后, 觸發器輸入端數據還應該繼續保持穩定不變的最小時間。建立( setup) / 保持( hold) 時間與時鐘跳變沿的關系如圖2 所示。

圖2 setup-hold 時間

因為觸發器內部數據的形成需要一定的時間, 如果不滿足建立和保持時間, 觸發器將進入亞穩態, 其輸出在經過一段時間的不確定狀態后才能隨機地穩定到0 或1。在穩定期間, 觸發器輸出一些中間級電平, 或者可能處于振蕩狀態, 并且這種無用的輸出電平可以沿信號通道上的各個觸發器級聯傳播下去, 導致其他數字部件的邏輯混亂。

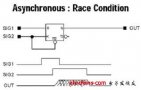

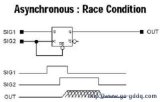

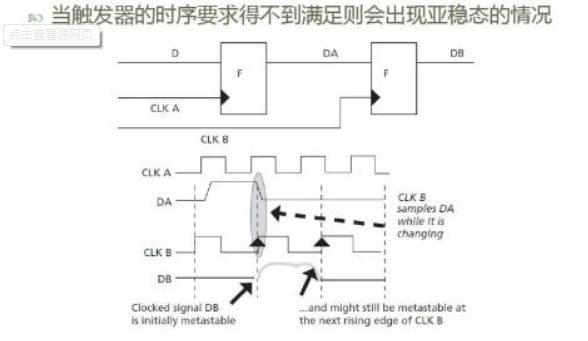

1. 2 異步時鐘造成的亞穩態

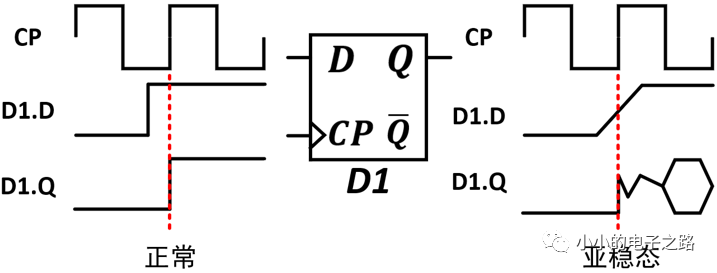

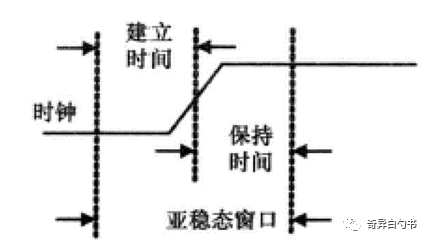

信號在跨時鐘域時應特別注意亞穩態問題。一個信號在過渡到另一個時鐘域時, 如果僅僅用一個觸發器將其鎖存, 那么采樣的結果將可能是亞穩態。圖3 所示為異步時鐘和亞穩態, 圖中a_ck 和b_ck 為異步時鐘。

圖3 觸發器產生亞穩態

信號dat 經過一個鎖存器的輸出數據為a_dat。用時鐘b_ck 進行采樣的時候, 如果a_dat 正好在b_ck 的set up??hold 時間內發生變化, 此時b_dat 就既不是邏輯1, 也不是邏輯0, 而是處于中間狀態。輸出信號處于中間狀態到恢復為邏輯1 或0 的這段時間, 稱為亞穩態時間。當觸發器的亞穩態時間超過一個時鐘周期時, 這種不確定狀態將會影響下一級的觸發器, 最終導致連鎖反應使整個系統功能失常。

1. 3 降低亞穩態的現有方法

常用于降低異步電路中亞穩態發生概率的方法有:

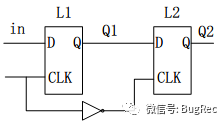

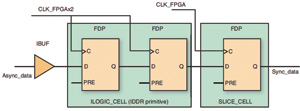

1) 兩級觸發器法

兩級觸發器法就是在一個信號進入另一個時鐘域之前, 將該信號用兩個觸發器連續鎖存兩次, 也稱為雙鎖存器法。這樣做可以防止由于異步輸入信號對于本級時鐘可能不滿足建立保持時間而使本級觸發器產生的亞穩態傳播到后面邏輯中。理論研究表明這種設計可以將出現亞穩態的幾率降低到一個很小的程度, 但這種方法同時帶來了對輸入信號的一級延時。

兩級觸發器法在2 個異步時鐘周期相差不大的情況下比較適合。在信號從快時鐘域向慢時鐘域過渡的時候,如果信號變化太快, 慢時鐘將可能無法對該信號進行正確的采樣, 導致采樣失敗。使用兩級觸發器法時, 應使原始信號保持足夠長的時間, 以便另一個時鐘域的觸發器可以正確地對其采樣。

2) 結繩法

針對雙鎖存器法在快時鐘域向慢時鐘域過渡中可能存在采樣失效的問題, 一般采用“結繩法” 進行設計, 通過分頻方式將慢時鐘信號的周期增長, 經雙鎖存采樣后再使其恢復原來的時鐘周期。即用“結繩” 將信號延長, 用“同步”實現雙鎖存采樣, 用“解繩”還原為原來的時鐘, 保證另一個時鐘域也可以正確采樣, 而接收方用相反的流程送回響應信號。

“結繩法”是一種安全的跨時鐘域的方法, 可以解決快時鐘域向慢時鐘域過渡的問題, 適用的范圍也很廣。但是“結繩法”實現較為復雜, 特別是其頻率不高, 所以在對設計性能要求較高的場合,應該慎用。

3) 異步FIFO

在有大量的數據需要進行跨時鐘域傳輸且對數據傳輸速度要求比較高的場合, 一般采用異步FIFO, 異步FIFO 即用一種時鐘寫入數據, 而用另外一種時鐘讀出數據, 其中這兩個讀寫時鐘是異步的。

4) 格雷編碼法

由實踐可知, 同步多個輸入信號出現亞穩態的概率遠大于同步1 個異步信號的概率。由于格雷碼每次只變化1位, 因此異步FIFO 的讀寫地址使用格雷碼計數器可以有效地減少亞穩態的產生, 特別是在地址位比較多的情況下能更好地解決亞穩態的問題。

2 、外部邏輯控制方法消除亞穩態

傳統的觀點認為: 只要系統中有異步元件, 亞穩態就是無法避免的。

在多時鐘域的異步電路系統中, 數據的建立和保持時間很難得到保證, 這時最好的方法是將所有非同源時鐘同步化[5] , 具體措施是使用帶復位端的D 觸發器, 并引入一個高頻時鐘( 頻率高于系統中的所有源時鐘) , 達到使系統中所有源時鐘同步的效果。基于這種思想, 本文提出一種新的方法-----半拍錯位同步法!, 選擇適當參數的邏輯器件, 便能徹底消除異步電路中的亞穩態。

2. 1 半拍錯位同步法原理

半拍錯位同步法的思想是: 從外部引入一高頻時鐘h_ck 到異步電路中, 通過一定的邏輯和時序處理, 將異步時鐘a_ck 同步到高頻時鐘的上升沿, 同時將異步時鐘b_ck同步到高頻時鐘h_ ck 的下降沿, 這樣兩個完全獨立的異步時鐘經過高頻時鐘h_ck 同步處理后, 時間上至少錯開時鐘h_ck 的半周期, 只要半周期滿足原電路中觸發器的建立時間要求, 便可徹底避免亞穩態的發生。

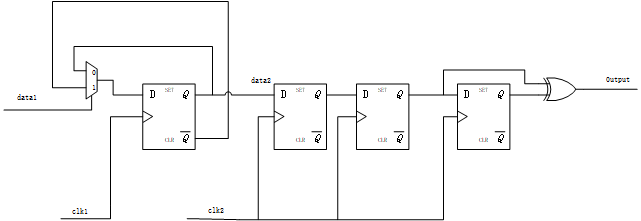

半拍錯位同步法的電路和時序波形圖如圖4 所示, 電路包括兩個帶異步復位端的D 觸發器、兩個信號延遲環節、兩個2 輸入端或門、兩個3 輸入端與門、1 個反相器。異步時鐘a_ck 與其延遲信號a_ck_d 的或輸出接觸發器D_A 的數據端D 和異步復位端CLR, a_ck 和a_ck_d 的與用于選通高頻時鐘h_ck 進入觸發器D_A 的時鐘端CP( 要求延遲時間大于觸發器D_A 的建立時間) 。

圖4 半拍錯位同步法的電路和時序波形圖

時序如下:

1) a_ck= 0 時, 觸發器復位端CLR 有效, a_ck_o= 0;

2) 上升沿過后, a_ck= 1 穩定作用在數據端D, 經延遲環節a_d 的適當延時后, a_ck 和a_ck_d 同時為1, 高頻時鐘h_ck 進入觸發器D_A 的時鐘端CP;

3) 高頻時鐘h_ ck 的上升沿將數據端D 的數據1 鎖存, 使輸出端a_ck_o= 1, a_ck_o 與h_ck 的上升沿同步;

4) a_ck 下降沿后a_ck= 0, 與門a_and 輸出0, 即觸發器D_A 的時鐘端CP 保持0, a_ck_o= 1;

5) a_ck 延時信號a_ck_d 下降沿后, 或門a_or 輸出0,觸發器復位使a_ck_o= 0。

異步時鐘b_ck 的時序情況與a_ck 類似, 唯一不同的是h_ck 的反相信號經b_ck 和b_ck_d 的與選通后進入D_B 的時鐘端, b_ck_o 與h_ck 的下降沿同步。

由圖4 可見, 設信號a_ck 和b_ck 分別在極為接近的時刻1 和2 向上跳變, 其相應輸出a_ck_o 和b _ck_o 的上升沿分別處于時刻3 和4, 時間上錯開了高頻時鐘的半周期, 同樣在時刻5 幾乎同時升上跳的信號a_ck 和b_ck, 輸出a_ck_o 和b_ck_o 的上升沿分別處于時刻7 和6, 也在時間上錯開了高頻時鐘的半周期。因此, 經過上部電路的處理后, 原來時間上完全獨立的信號a_ ck 和b_ck 變成了時間上有一最小固定間隔的信號a_ck_o 和b_ck_o。

為了敘述方便, 規定電路中參數的符號表示為: 延遲環節的延遲時間為T d, 高頻時鐘h_ck 的周期為T hck, 同步電路中D 觸發器的建立時間為信號T set, 保持時間為信號T hold , a_ck 和b_ck 的高電平寬度為T H , 基于上述表示, 根據半拍錯位同步法的時序要求, 對電路的相關參數選擇原則總結如下:

1) T hck》 T of f, T of f表示后面電路中對異步時鐘信號的時間分離或數據建立時間要求, 高頻時鐘應在滿足此條件基礎上取較高的頻率;

2) T d》 T s , 確保D 觸發器的數據建立時間滿足要求;

3) T H+ T d》 T set + T hold ;

4) T H》 T d+ 2 # T hck。

2. 2 半拍錯位同步法的應用

2. 2. 1 在異步觸發電路中的應用

以圖3( a) 電路為例說明半拍錯位同步法在異步觸發電路中的應用, 將半拍錯位同步電路串行接入圖3 的異步觸發電路, 給同步電路引入一高頻時鐘h _ck, 圖3( a) 電路中的a_ck 和b_ck 接同步電路的相應觸發器, dat 連接關系不變, 同步電路輸出a_ck_ o 和b _ck_ o 分別代替a_ck 和

b_ck接入原電路相應位置, 由2. 1 小節的分析知, 給原電路串入半拍錯位同步電路后, 由于a_ck_o 和b_ck_o 在時間上錯開半個h_ck 周期, 其后的觸發電路中不會再發生亞穩態。

2. 2. 2 在異步FIFO 中的應用

異步FIFO( First In First Out ) 為多時鐘域系統異步時鐘間接口設計提供了一種簡便、快捷的解決方案, 在網絡接口、圖像處理等方面, 得到了廣泛的應用。

異步FIFO 是跨時鐘域設計方法的集中體現, 體現了很多的方法。其中最重要的有兩點, 一個是亞穩態, 另一個就是和亞穩態類似但不相同的------多個控制/ 狀態信號的跨時鐘傳遞。對于異步FIFO, 采用格雷碼進行讀寫地址計數, 每次只變化1 個位, 大大減小了亞穩態發生的概率。由于異步FIFO 的讀寫信號屬于不同的時間域, 因此set up/ hold 沖突和亞穩態的發生是必然的, 數據的丟失概率不為零。

異步FIFO 產生亞穩態的原因是讀寫信號屬于不同的時間域, 沒有確定的時間關系, 因此只要通過適當的外部邏輯將讀寫信號在時間上產生間隔, 就能消除亞穩態, 解決異步FIFO 丟失數據問題。將半拍錯位同步法用于異步FIFO 的讀寫信號控制的電路如圖5 所示, 圖中虛線框內是半拍錯位同步電路。給同步電路引入高頻時鐘h_ck, 外部獨立的讀R# 和寫W# 信號接在虛線框內的同步器上,

同步電路的輸出R_O 和W_O 接FIFO 的讀寫管腳, 由2. 1小節的分析知, 給原電路串入半拍錯位同步電路后, 由于R_O和W_O 在時間上至少錯開半個h_ck 周期, 因此其后的異步FIFO 中不會發生亞穩態造成數據丟失。

圖5 半拍錯位同步法在異步FIFO 中應用

圖5 所示的電路是對異步FIFO 外加控制邏輯消除亞穩態。半拍錯位同步法也可用于由異步FIFO 的FPGA 設計中。

3、 結論

亞穩態是異步電路和異步FIFO 設計中的常見問題,將異步信號同步化的幾種常用方法雖能大大將降低亞穩態發生的概率, 但無法 根除! 亞穩態的發生。本文提出的半拍錯位同步法!, 通過附加的帶異步復位端的D 觸發器和高頻時鐘, 將異步時鐘分別同步到高頻時鐘的上升沿和下降沿, 使得過于接近的異步時鐘在時間上拉開一定的間隔, 只要選擇適當的延遲時間和高頻時鐘, 便能徹底消除亞穩態的發生, 在航天航空、軍事等對要求高可靠數據傳遞的應用領域具有廣闊的應用前景。

責任編輯:gt

電子發燒友App

電子發燒友App

評論