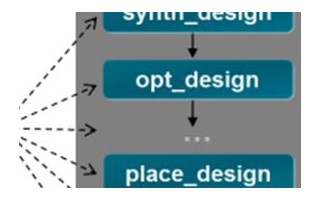

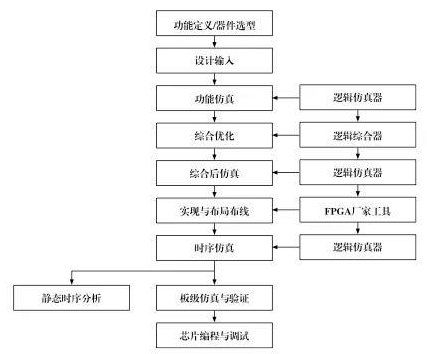

FPGA開發(fā)基本流程包括:設(shè)計(jì)輸入、設(shè)計(jì)仿真、設(shè)計(jì)綜合、布局布線,它們的連接關(guān)系如圖1 所示。

2010-06-10 08:24:15 1687

1687 如圖1.9所示。這個(gè)流程圖是一個(gè)相對(duì)比較高等級(jí)的FPGA開發(fā)流程,從項(xiàng)目的提上議程開始,設(shè)計(jì)者需要進(jìn)行FPG

2017-10-24 10:43:09 7183

7183

即是相應(yīng)的 HDL 程序以及最新非常流行的基于高層次綜合的程序方法,如Xilinx的一系列工具HLS、SDSoC和Altera的SoC EDS等。 (1)選擇FPGA(SoC)的若干理由 a)FPGA

2020-12-17 12:58:21 4094

4094 FPGA的開發(fā)流程是遵循著ASIC的開發(fā)流程發(fā)展的,發(fā)展到目前為止,FPGA的開發(fā)流程總體按照?qǐng)D1進(jìn)行,有些步驟可能由于其在當(dāng)前項(xiàng)目中的條件的寬度的允許,可以免去。

2023-01-06 11:19:28 1403

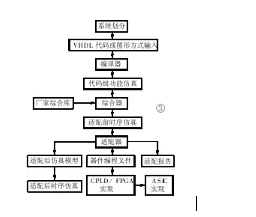

1403 FPGA是可編程芯片,因此FPGA的設(shè)計(jì)方法包括硬件設(shè)計(jì)和軟件設(shè)計(jì)兩部分。硬件包括FPGA芯片電路、存儲(chǔ)器、輸入輸出接口電路以及其他設(shè)備,軟件即是相應(yīng)的HDL程序以及最新才流行的嵌入式C程序。

2023-02-10 11:41:54 1390

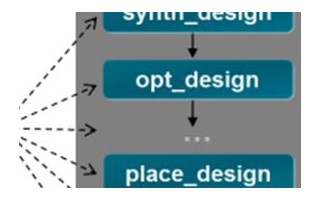

1390 FPGA 的設(shè)計(jì)流程簡單來講,就是從源代碼到比特流文件的實(shí)現(xiàn)過程。大體上跟 IC 設(shè)計(jì)流程類似,可以分為前端設(shè)計(jì)和后端設(shè)計(jì)。

2023-04-23 09:08:49 1577

1577

哪位大神可以發(fā)一個(gè)FPGA開發(fā)流程的文檔,用實(shí)例演示的,包括行為,功能和時(shí)序分析的,萬分感謝!

2014-05-14 10:34:40

如圖1.6所示。這個(gè)流程圖是一個(gè)相對(duì)比較高等級(jí)的FPGA開發(fā)流程,從項(xiàng)目的提上議程開始,設(shè)計(jì)者需要進(jìn)行FPGA功能的需求分析,然后進(jìn)行模塊的劃分,比較復(fù)雜和龐大的設(shè)計(jì),則會(huì)通過模塊劃分把工作交給一個(gè)

2019-01-28 04:24:37

基于FPGA的SOC設(shè)計(jì)方法 32基于FPGA的典型SOC開發(fā)流程為 32第五章、FPGA實(shí)戰(zhàn)開發(fā)技巧 335.1 FPGA器件選型常識(shí) 335.1.1器件的供貨渠道和開發(fā)工具的支持 335.1.2

2009-04-09 18:28:46

第四章、FPGA開發(fā)基本流程 294.1 典型FPGA開發(fā)流程與注意事項(xiàng)294.2 基于FPGA的SOC設(shè)計(jì)方法32基于FPGA的典型SOC開發(fā)流程為32第五章、FPGA實(shí)戰(zhàn)開發(fā)

2012-02-27 15:44:02

FPGA入門開發(fā)具體流程有哪些?求過程

2021-07-26 06:44:39

FPGA入門:基本開發(fā)流程概述 本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA/CPLD邊練邊學(xué)——快速入門Verilog/VHDL》書中代碼請(qǐng)?jiān)L問網(wǎng)盤:http://pan.baidu.com/s

2015-02-09 20:14:21

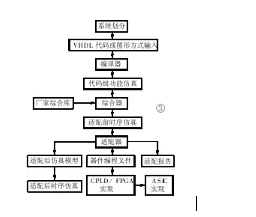

在第一章中,已經(jīng)給出了FPGA/CPLD的基本開發(fā)流程圖。這里不妨回顧一下,如圖5.15所示。這個(gè)流程圖是一個(gè)相對(duì)比較高等級(jí)的FPGA/CPLD器件開發(fā)流程,從項(xiàng)目的提上議程開始,設(shè)計(jì)者需要進(jìn)行

2015-03-03 14:31:44

FPGA入門:基本開發(fā)流程概述 在第一章中,已經(jīng)給出了FPGA/CPLD的基本開發(fā)流程圖。這里不妨回顧一下,如圖5.15所示。這個(gè)流程圖是一個(gè)相對(duì)比較高等級(jí)的FPGA/CPLD器件開發(fā)流程,從項(xiàng)目

2019-01-28 02:29:05

FPGA的設(shè)計(jì)流程就是利用EDA開發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開發(fā)的過程。FPGA的開發(fā)流程一般包括功能定義、設(shè)計(jì)輸入、功能仿真、綜合優(yōu)化、綜合后仿真、實(shí)現(xiàn)與布局布線、時(shí)序仿真與驗(yàn)證、板級(jí)仿真

2023-12-31 21:15:31

FPGA的設(shè)計(jì)流程就是利用EDA開發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開發(fā)的過程。FPGA的開發(fā)流程一般如圖1-10所示,包括電路功能設(shè)計(jì)、設(shè)計(jì)輸入、功能仿真、綜合優(yōu)化、綜合后仿真、實(shí)現(xiàn)、布線后仿真

2021-07-23 09:12:07

FPGA開發(fā)流程(特權(quán)同學(xué)版權(quán)所有)本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》(特權(quán)同學(xué)版權(quán)所有)配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-31 09:27:38

FPGA應(yīng)用開發(fā)入門與典型實(shí)例

2017-04-21 12:47:01

FPGA應(yīng)用開發(fā)入門與典型實(shí)例

2020-05-21 09:27:47

系統(tǒng)的設(shè)計(jì)技巧 2.4 FPGA硬件系統(tǒng)的調(diào)試方法 2.5 典型實(shí)例1:在Altera的FPGA開發(fā)板上運(yùn)行第一個(gè)FPGA程序 2.6 典型實(shí)例2:在Xilinx的FPGA開發(fā)板上運(yùn)行第一個(gè)

2012-02-09 15:45:32

FPGA應(yīng)用開發(fā)入門與典型實(shí)例pdf免費(fèi)下載(華清遠(yuǎn)見編寫)https://bbs.elecfans.com/forum.php?mod=viewthread&tid=216057&

2012-02-09 16:29:46

的學(xué)習(xí)方法,都將事半功倍。學(xué)習(xí)的過程為理解基礎(chǔ)概念、結(jié)合實(shí)踐應(yīng)用、掌握方法融會(huì)貫通,最終達(dá)到獨(dú)立開發(fā)的能力。本期將聚焦于解答基礎(chǔ)技術(shù)問題、提供學(xué)習(xí)工具和方法。本期互動(dòng)提問范圍:1、FPGA設(shè)計(jì)流程

2017-01-11 13:58:34

使用 ISE 進(jìn)行 FPGA 開發(fā)的流程大致可以分為 3 個(gè)步驟。1.設(shè)計(jì)輸入與仿真設(shè)計(jì)輸入(Design Entry)是指以 HDL 代碼、原理圖、波形圖以及狀態(tài)機(jī)的形式輸入設(shè)計(jì)源文件,而設(shè)計(jì)仿真

2018-09-28 09:34:34

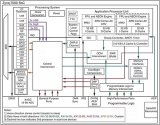

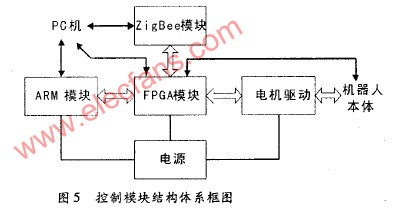

FPGA的邏輯資源組成,大都以IP 的形式提供,例如存儲(chǔ)器接口、USB接口以及以太網(wǎng)MAC層接口等,用戶根據(jù)自己需要在內(nèi)核總線上添加,并能自己訂制相應(yīng)的接口IP和外圍設(shè)備。基于FPGA的典型SOC開發(fā)流程為

2017-01-10 15:50:15

描述語言)是兩種最常用的數(shù)字硬件電路描述方法。其中,運(yùn)用 HDL 設(shè)計(jì)方法具有更好的移植性、通用性以及利于模塊劃分的特點(diǎn),在工作學(xué)習(xí)中被廣泛使用。典型 FPGA 的開發(fā)流程一般如下圖所示, 其包括功能

2022-02-23 06:23:33

;在設(shè)計(jì)后期,需要根據(jù)底層模塊的實(shí)現(xiàn)情況完成相應(yīng)的修訂。1.3.2 典型FPGA開發(fā)流程FPGA的設(shè)計(jì)流程就是利用EDA開發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開發(fā)的過程。FPGA的開發(fā)流程一般如圖1-7

2015-11-30 15:28:41

流程,否則走cold流程。注意這里所說的warm流程,只是軟件上的warm流程,并非說當(dāng)前是warm reset。5.2 primary boot和secondary boot這種判斷方法由平臺(tái)實(shí)現(xiàn)

2023-02-21 15:11:44

簡述SOC的設(shè)計(jì)流程跟方法,以及現(xiàn)在市場上跟SOC設(shè)計(jì)相關(guān)的解決方案;接下來我們會(huì)將眼光轉(zhuǎn)到OPENCORES,這是一個(gè)以opensource的精神推廣IC設(shè)計(jì)的機(jī)構(gòu),筆者會(huì)介紹在OPENCORES

2023-09-20 07:24:04

為什么verilog可以描述硬件?在SOC設(shè)計(jì)中使用verilog,和FPGA為對(duì)象使用verilog,有什么區(qū)別?SOC流程和FPGA流程的不同之處在哪里?

2021-06-21 07:02:59

嵌入式系統(tǒng)市場的滲透率急速攀升,FPGA廠商各自開發(fā)出更具競爭力的SoC FPGA、創(chuàng)新ASIC級(jí)可編程架構(gòu)、加強(qiáng)與SoC合作伙伴的交流,意圖打造更完善的SoC生態(tài)系統(tǒng),大舉進(jìn)攻嵌入式系統(tǒng)應(yīng)用市場。

2019-08-26 07:15:50

SoC芯片的開發(fā)流程SoC芯片開發(fā)流程大致分為四個(gè)階段,其中大部分工作都是借助于電子設(shè)計(jì)自動(dòng)化(EDA)工具完成的。總體設(shè)計(jì)總體設(shè)計(jì)階段的任務(wù)是按照系統(tǒng)需求說明書確定SoC的性能參數(shù),并據(jù)此進(jìn)行系統(tǒng)

2021-11-08 08:33:27

SoC設(shè)計(jì)流程一、SoC設(shè)計(jì)的特點(diǎn)二、軟硬件協(xié)同設(shè)計(jì)流程2.1 系統(tǒng)需求說明2.2 高級(jí)算法建模與仿真2.3 軟硬件劃分過程2.4 軟硬件同步設(shè)計(jì)三、基于標(biāo)準(zhǔn)單元的SoC芯片設(shè)計(jì)流程一、SoC

2021-11-11 07:48:45

家庭娛樂市場上的新興標(biāo)準(zhǔn)是什么?SoC設(shè)計(jì)中杜比數(shù)字加的實(shí)現(xiàn)優(yōu)化方法是什么

2021-06-08 07:15:27

先進(jìn)的設(shè)計(jì)與仿真驗(yàn)證方法成為SoC設(shè)計(jì)成功的關(guān)鍵。一個(gè)簡單可行的SoC驗(yàn)證平臺(tái),可以加快SoC系統(tǒng)的開發(fā)與驗(yàn)證過程。FPGA器件的主要開發(fā)供應(yīng)商都針對(duì)自己的產(chǎn)品推出了SoC系統(tǒng)的開發(fā)驗(yàn)證平臺(tái),如

2019-10-11 07:07:07

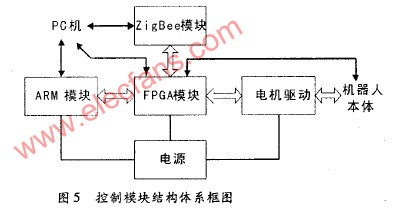

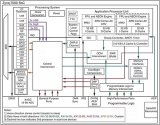

硬件加速,最典型的架構(gòu)就是將需要加速的大運(yùn)算量邏輯部署到FPGA上,而將流程控制的邏輯部署到arm上。典型的ZYNQ SoC結(jié)構(gòu)如圖1。 CNN簡介 CNN全稱卷積神經(jīng)網(wǎng)絡(luò),包括卷積層

2021-01-15 17:09:15

ASIC的設(shè)計(jì)流程是怎樣的?FPGA的開發(fā)流程又是怎樣的?

2021-11-01 07:08:47

`Xilinx Artix-7 FPGA快速入門、技巧與實(shí)例連載6——FPGA開發(fā)流程更多資料共享鏈接:https://share.weiyun.com/53UnQas如圖1.32所示,這是一個(gè)

2019-04-01 17:50:52

arm,asic,dsp,fpga,mcu,soc各自的特點(diǎn)人工智能受到越來越多的關(guān)注,許多公司正在積極開發(fā)能實(shí)現(xiàn)移動(dòng)端人工智能的硬件,尤其是能夠結(jié)合未來的物聯(lián)網(wǎng)應(yīng)用,對(duì)于移動(dòng)端人工智能硬件的實(shí)現(xiàn)

2021-11-11 07:35:31

開發(fā)流程與注意事項(xiàng) 294.2 基于FPGA的SOC設(shè)計(jì)方法 32基于FPGA的典型SOC開發(fā)流程為 32第五章、FPGA實(shí)戰(zhàn)開發(fā)技巧 335.1 FPGA器件選型常識(shí) 335.1.1器件的供貨渠道

2014-11-03 17:14:22

本文介紹在使用Arm DesignStart計(jì)劃開放的處理器核搭建SoC并通過FPGA實(shí)現(xiàn)的過程中所用工具軟件(不介紹如何操作),理清“軟件編程”和“硬件編程”的概念,熟悉SoC設(shè)計(jì)的流程。軟硬件

2022-04-01 17:48:02

例說FPGA連載8:FPGA開發(fā)流程特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 如圖1.9所示。這個(gè)流程圖是一個(gè)相對(duì)

2016-07-13 17:25:34

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載8:FPGA開發(fā)流程特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 如圖1.9所示。這個(gè)

2017-10-12 21:02:44

前言 本部門所承擔(dān)的FPGA設(shè)計(jì)任務(wù)主要是兩方面的作用:系統(tǒng)的原型實(shí)現(xiàn)和ASIC的原型驗(yàn)證。編寫本流程的目的是:l在于規(guī)范整個(gè)設(shè)計(jì)流程,實(shí)現(xiàn)開發(fā)的合理性、一致性、高效性。l形成風(fēng)格良好和完整的文檔

2017-12-08 14:47:15

華為FPGA設(shè)計(jì)流程指南本部門所承擔(dān)的FPGA設(shè)計(jì)任務(wù)主要是兩方面的作用:系統(tǒng)的原型實(shí)現(xiàn)和ASIC的原型驗(yàn)證。編寫本流程的目的是:l在于規(guī)范整個(gè)設(shè)計(jì)流程,實(shí)現(xiàn)開發(fā)的合理性、一致性、高效性。l形成

2017-12-18 10:45:03

產(chǎn)生的。 有了此層級(jí)的抽出,針對(duì)混合信號(hào)FPGA所提供的基本驗(yàn)證方法和沿著標(biāo)準(zhǔn)處理的數(shù)字FPGA基本上是相同的。 典型的PSC設(shè)計(jì)者會(huì)在設(shè)計(jì)過程中執(zhí)行以下步驟:在Libero中產(chǎn)生并整合系統(tǒng)功能區(qū)塊

2011-10-16 22:55:10

SoC設(shè)計(jì)的特點(diǎn)軟硬件協(xié)同設(shè)計(jì)流程基于標(biāo)準(zhǔn)單元的SoC芯片設(shè)計(jì)流程

2021-01-26 06:45:40

使用SoC FPGA,實(shí)現(xiàn)汽車?yán)走_(dá)的數(shù)字化處理本白皮書介紹使用Altera? 低成本Cyclone? V SoC FPGA,實(shí)現(xiàn)典型雷達(dá)系統(tǒng)數(shù)字化處理的可行性。與定制ASIC 相比,這一方法的優(yōu)勢

2013-11-13 15:56:28

嵌入式開發(fā)板開發(fā)流程有哪些呢?SOC系統(tǒng)開發(fā)流程有哪些呢?嵌入式開發(fā)板開發(fā)與SOC系統(tǒng)開發(fā)有哪些不同之處呢?

2021-12-27 07:55:18

SoC下載到安路FPGA開發(fā)板中,并編寫簡單的匯編代碼,利用Keil在SoC平臺(tái)上進(jìn)行調(diào)試運(yùn)行。硬件原理SoC組成圖1-1為本實(shí)驗(yàn)需要實(shí)現(xiàn)的SoC架構(gòu)示意圖。圖1-1 本實(shí)驗(yàn)實(shí)現(xiàn)的簡單

2022-08-09 17:09:36

)的發(fā)展趨勢,也是21世紀(jì)集成電路技術(shù)的主流,其為集成電路產(chǎn)業(yè)和集成電路應(yīng)用技術(shù)提供了前所未有的廣闊市場和難得的發(fā)展機(jī)遇。SOC為微電子應(yīng)用產(chǎn)品研究、開發(fā)和生產(chǎn)提供了新型的優(yōu)秀的技術(shù)方法和工具,也是解決電子產(chǎn)品開發(fā)中的及時(shí)上市(TTM——Time to Market)的主要技術(shù)與方法。

2011-09-27 11:46:06

FPGA開發(fā)流程與注意事項(xiàng) 294.2 基于FPGA的SOC設(shè)計(jì)方法 32基于FPGA的典型SOC開發(fā)流程為 32第五章、FPGA實(shí)戰(zhàn)開發(fā)技巧 335.1 FPGA器件選型常識(shí) 335.1.1器件的供貨渠道

2014-11-21 15:08:56

在介紹嵌入式 SoC IC 概念的基礎(chǔ)上,介紹基于重用(re-use)的 SoC IC 設(shè)計(jì)方法和流程, 涉及滿足時(shí)序要求、版圖設(shè)計(jì)流程和測試設(shè)計(jì)的問題, 并給出設(shè)計(jì)計(jì)劃考慮項(xiàng)目。

2009-05-13 16:09:42 28

28 一次呼叫典型流程:一次呼叫典型流程B.1 概述本章將分別給出主叫流程和被叫流程的例子,以示一次通話過程中UTRAN的典型流程。B.2 主叫流程主叫流程是指UE呼叫其它用戶

2009-11-28 17:57:44 26

26 系統(tǒng)(HPS)來評(píng)估SoC的特性及性能。Intel Agilex? F系列FPGA開發(fā)套件提供了一個(gè)完整的設(shè)計(jì)環(huán)境,其中包括采用PCI Express(PCIe)

2024-02-27 11:51:58

全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司,今天宣布了業(yè)界最全面的用于系統(tǒng)級(jí)芯片(SoC)驗(yàn)證的通用驗(yàn)證方法學(xué)(UVM)開源參考流程。為了配合Cadence EDA360中SoC實(shí)現(xiàn)能力的策略,

2010-06-28 08:29:14 2240

2240 摘要:文中詳述了FPGA被動(dòng)串行配置方式的時(shí)序,給出配置流程圖及實(shí)現(xiàn)的程序代碼,并通過實(shí)例驗(yàn)證了該方法的優(yōu)越

2010-07-21 14:48:48 1326

1326

《 FPGA的原型開發(fā)方法手冊(cè)》(FPMM),這是一本介紹如何使用 FPGA 作為平臺(tái)進(jìn)行片上系統(tǒng)(SoC)開發(fā)的實(shí)用指南。FPMM 收錄了眾多公司的設(shè)計(jì)團(tuán)隊(duì)在設(shè)計(jì)和驗(yàn)證方面的寶貴經(jīng)驗(yàn),

2011-03-14 09:06:50 734

734 Synopsys和Xilinx合作出版業(yè)界首本基于FPGA的SoC設(shè)計(jì)原型方法手冊(cè)。

2011-03-21 10:26:23 810

810 本文是關(guān)于Altera公司SoC FPGA 的用戶手冊(cè)(英文版) 。文中主要介紹了什么是SoC FPGA、SoC FPGA相關(guān)知識(shí)介紹、為什么要使用SoC FPGA以及SoC FPGA都應(yīng)用到哪些方面。

2012-09-05 14:03:08 153

153 白皮書介紹使用Altera?低成本 Cyclone? V SoC FPGA,實(shí)現(xiàn)典型雷達(dá)系統(tǒng)數(shù)字化處理的可行性。與定制ASIC 相比,這一方法的優(yōu)勢在于縮短了產(chǎn)品面市時(shí)間,支持現(xiàn)場現(xiàn),而且還可以使用汽車級(jí)器

2013-10-10 21:09:24 0

0 Altera全球SoC FPGA開發(fā)者論壇活動(dòng)在深圳成功舉行,Altera合作伙伴、FPGA開發(fā)者和工程師匯聚一堂,共同關(guān)注使用基于ARM的SoC FPGA中的精細(xì)粒度異構(gòu)計(jì)算技術(shù),在滿足下一代嵌入式計(jì)算應(yīng)用需求中,如何解決系統(tǒng)設(shè)計(jì)的難題。

2015-11-13 17:38:16 1927

1927 FPGA開發(fā)流程及編程思想,好東西,喜歡的朋友可以下載來學(xué)習(xí)。

2016-01-18 15:17:27 31

31 FPGA開發(fā)流程,好東西,喜歡的朋友可以下載來學(xué)習(xí)。

2016-01-18 15:17:27 32

32 設(shè)計(jì)了一種基于FPGA的驗(yàn)證平臺(tái)及有效的SoC驗(yàn)證方法,介紹了此FPGA驗(yàn)證軟硬件平臺(tái)及軟硬件協(xié)同驗(yàn)證架構(gòu),討論和分析了利用FPGA軟硬件協(xié)同系統(tǒng)驗(yàn)證SoC系統(tǒng)的過程和方法。利用此軟硬件協(xié)同驗(yàn)證

2017-11-17 03:06:01 13138

13138

門陣列(FPGA)做為安謀國際核心測試芯片,進(jìn)而建構(gòu)SoC原型制作平臺(tái)。 驗(yàn)證SoC設(shè)計(jì) FPGA原型最穩(wěn)當(dāng) FPGA原型制作是在FPGA上實(shí)作SoC或特定應(yīng)用集成電路(ASIC)設(shè)計(jì)的方法,并進(jìn)行硬件驗(yàn)證和早期軟件開發(fā)。

2018-05-11 09:07:00 2405

2405

不斷 從賽靈思FPGA設(shè)計(jì)流程看懂FPGA設(shè)計(jì) 1.XILINX ISE傳統(tǒng)FPGA設(shè)計(jì)流程 利用XilinxISE軟件開發(fā)FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合

2018-02-20 20:32:00 15820

15820

SDSoC是Xilinx推出的一個(gè)基于簡便易用的Eclipse集成設(shè)計(jì)環(huán)境(IDE)的工具套件,它支持Zynq-7000全可編程SoC和Zynq UltraScale+ MPSoC,以及MicroBlaze處理器,可以為開發(fā)者提供類似嵌入式 C/C++/OpenCL 應(yīng)用的開發(fā)體驗(yàn)。

2018-05-01 16:53:00 14997

14997 在一個(gè)芯片上,包括核心處理器、存儲(chǔ)單元、硬件加速單元以及眾多的外部設(shè)備接口等,具有設(shè)計(jì)周期長、實(shí)現(xiàn)成本高等特點(diǎn),因此其設(shè)計(jì)方法必然是自頂向下的從系統(tǒng)級(jí)到功能模塊的軟、硬件協(xié)同設(shè)計(jì),達(dá)到軟、硬件的無縫結(jié)合。

2018-05-10 15:25:00 21481

21481

FPGA的開發(fā)流程是遵循著ASIC的開發(fā)流程發(fā)展的,發(fā)展到目前為止,FPGA的開發(fā)流程總體按照?qǐng)D1進(jìn)行,有些步驟可能由于其在當(dāng)前項(xiàng)目中的條件的寬度的允許,可以免去,比如靜態(tài)仿真過程,這樣來達(dá)到項(xiàng)目

2018-11-18 09:55:45 1273

1273

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA教程之FPGA系統(tǒng)設(shè)計(jì)的主要思路和方法初探資料說明包括了:1.FPGA的適用領(lǐng)域及選型FPGA系統(tǒng)設(shè)計(jì)典型流程,2.FPGA邏輯設(shè)計(jì)方法 弓|入ASIC的設(shè)計(jì)方法,3.FPGA設(shè)計(jì)的常用技巧,4.FPGA系統(tǒng)設(shè)計(jì)中的對(duì)與錯(cuò)

2019-04-04 17:19:58 53

53 本文檔的詳細(xì)介紹的是FPGA設(shè)計(jì)有哪些良好的設(shè)計(jì)方法及誤區(qū)內(nèi)容包括了:1.FPGA的適用領(lǐng)域及選型,2.FPGA系統(tǒng)設(shè)計(jì)典型流程,3.FPGA邏輯設(shè)計(jì)良好設(shè)計(jì)方法一引入ASIC的設(shè)計(jì)方法,4.FPGA設(shè)計(jì)的常用技巧,5.FPGA系統(tǒng)設(shè)計(jì)中的誤區(qū)

2019-04-18 17:30:04 23

23 在使用 FPGA 構(gòu)建的基于微控制器的典型系統(tǒng)中,開發(fā)人員需要管理用于加載 FPGA 編程比特流的序列和安全性。在 Zynq SoC 中,集成的處理器負(fù)責(zé)執(zhí)行常規(guī)微控制器的任務(wù),包括管理 PL 結(jié)構(gòu)

2019-04-30 16:42:51 4721

4721

小梅哥最新款FPGA_SOC

2019-08-30 06:10:00 3548

3548

本教程介紹Quartus Prime CAD系統(tǒng)。本文概述了用fpga器件實(shí)現(xiàn)的典型電路設(shè)計(jì)CAD流程,并說明了該流程是如何在quartus prime軟件中實(shí)現(xiàn)的。通過給出使用quartus prime軟件在intel-fpga設(shè)備中實(shí)現(xiàn)非常簡單的電路的逐步說明,說明了設(shè)計(jì)過程。

2019-09-20 08:00:00 6

6 FPGA的設(shè)計(jì)流程就是利用EDA開發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開發(fā)的過程。FPGA的開發(fā)流程一般包括功能定義/器件選型、設(shè)計(jì)輸入、功能仿真、邏輯綜合、布局布線與實(shí)現(xiàn)、編程調(diào)試等主要步驟。

2019-11-06 15:17:28 2224

2224 FPGA的設(shè)計(jì)流程就是利用EDA開發(fā)軟件和編程工具對(duì)FPGA芯片進(jìn)行開發(fā)的過程。FPGA的開發(fā)流程包括功能定義/器件選型、設(shè)計(jì)輸入、功能仿真、邏輯綜合、布局布線與實(shí)現(xiàn)、編程調(diào)試等主要步驟。

2019-11-20 15:06:28 1545

1545 討論了利用FPGA工具實(shí)現(xiàn)MBUS總線的原理、方法,以實(shí)際操作介紹了FPGA設(shè)計(jì)流程,并給出FPGA常用設(shè)計(jì)技巧。

2019-12-24 14:54:08 9

9 FPGA的開發(fā)流程是遵循著ASIC的開發(fā)流程發(fā)展的,發(fā)展到目前為止,FPGA的開發(fā)流程總體按照下圖進(jìn)行,有些步驟可能由于其在當(dāng)前項(xiàng)目中的條件的寬度的允許,可以免去,比如靜態(tài)仿真過程,這樣來達(dá)到項(xiàng)目

2020-10-25 10:05:37 3592

3592

FPGA 是可編程芯片,因此 FPGA 的設(shè)計(jì)方法包括硬件設(shè)計(jì)和軟件設(shè)計(jì)兩部分。硬件包括 FPGA 芯片電路、 存儲(chǔ)器、輸入輸出接口電路以及其他設(shè)備,軟件即是相應(yīng)的 HDL 程序以及最新才流行

2022-12-20 13:13:19 1594

1594 的設(shè)計(jì)來例系統(tǒng)地介紹了利用多種EDA工具進(jìn)行 FPGA協(xié)同設(shè)計(jì)的實(shí)現(xiàn)原理及方法近年來,隨著微電子學(xué)的迅速發(fā)展以及SoC(System on Chip ,片上系統(tǒng)) 技術(shù)在設(shè)計(jì)領(lǐng)域引起的深刻變革,EDA(Electornic Design Automatic ,電子設(shè)計(jì)自動(dòng)化) 工具在系統(tǒng)設(shè)計(jì)中的地位愈發(fā)重要

2020-11-27 17:57:34 29

29 LTE排障流程及典型案例分享。

2021-05-25 15:57:57 5

5 FPGA-SoC芯片中EDAC模塊的設(shè)計(jì)與實(shí)現(xiàn)(深圳市宇衡源電源技術(shù))-該文檔為FPGA-SoC芯片中EDAC模塊的設(shè)計(jì)與實(shí)現(xiàn)簡介文檔,是一份還算不錯(cuò)的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-27 14:32:18 13

13 SoC芯片的開發(fā)流程SoC芯片開發(fā)流程大致分為四個(gè)階段,其中大部分工作都是借助于電子設(shè)計(jì)自動(dòng)化(EDA)工具完成的。總體設(shè)計(jì)總體設(shè)計(jì)階段的任務(wù)是按照系統(tǒng)需求說明書確定SoC的性能參數(shù),并據(jù)此進(jìn)行系統(tǒng)

2021-11-03 18:06:01 24

24 SoC設(shè)計(jì)流程一、SoC設(shè)計(jì)的特點(diǎn)二、軟硬件協(xié)同設(shè)計(jì)流程2.1 系統(tǒng)需求說明2.2 高級(jí)算法建模與仿真2.3 軟硬件劃分過程2.4 軟硬件同步設(shè)計(jì)三、基于標(biāo)準(zhǔn)單元的SoC芯片設(shè)計(jì)流程一、SoC

2021-11-06 16:21:01 37

37 描述語言)是兩種最常用的數(shù)字硬件電路描述方法。其中,運(yùn)用 HDL 設(shè)計(jì)方法具有更好的移植性、通用性以及利于模塊劃分的特點(diǎn),在工作學(xué)習(xí)中被廣泛使用。典型 FPGA 的開發(fā)流程一般如下圖所示, 其包括功能

2021-12-29 19:40:15 9

9 FPGA開發(fā)的具體難度,與軟件開發(fā)有輸入、編譯、鏈接、執(zhí)行步驟對(duì)應(yīng)的就是設(shè)計(jì)輸入、綜合、布局布線、下載燒寫,FPGA開發(fā)只是為了確保這核心實(shí)現(xiàn)主干路每一個(gè)環(huán)節(jié)的成功性加了其他的修飾(約束)和驗(yàn)證而已。下面將以核心主干路為路線,介紹每個(gè)環(huán)節(jié)的物理含義和實(shí)現(xiàn)目標(biāo)。

2022-06-30 14:23:29 3380

3380 硬件電路描述方法。其中,運(yùn)用 HDL 設(shè)計(jì)方法具有更好的移植性、通用性以及利于模塊劃分的特點(diǎn),在工作學(xué)習(xí)中被廣泛使用。典型 FPGA 的開發(fā)流程一般如下圖所示, 其包括功能定義/器件選型、設(shè)計(jì)輸入、功能仿真、綜合優(yōu)化、綜合后仿真、實(shí)現(xiàn)、布線后仿真、板級(jí)仿真以及芯片編程與調(diào)試等主要步驟。

2023-03-21 10:26:50 2623

2623 開始SoC FPGA的學(xué)習(xí)路程還是蠻難的,不僅要熟悉整個(gè)的設(shè)計(jì)流程,而且還要掌握FPGA以及軟件方面的知識(shí),尤其大概看了一下后面的整體設(shè)計(jì)部分,操作起來還是較為繁瑣的,以至于讓人暈頭轉(zhuǎn)向。盡管如此

2023-03-30 10:13:35 6239

6239 ??FPGA 的詳細(xì)開發(fā)流程就是利用 EDA 開發(fā)工具對(duì) FPGA 芯片進(jìn)行開發(fā)的過程,所以 FPGA 芯片開發(fā)流程講的并不是芯片的制造流程,區(qū)分于 IC 設(shè)計(jì)制造流程喲(芯片制造流程多麻煩,要好

2023-07-04 14:37:17 2387

2387

電子發(fā)燒友網(wǎng)站提供《面向Xilinx FPGA和SoC的超快設(shè)計(jì)方法指南.pdf》資料免費(fèi)下載

2023-09-14 10:02:31 1

1 電子發(fā)燒友網(wǎng)站提供《Xilinx FPGA和SoC的超高速設(shè)計(jì)方法指南.pdf》資料免費(fèi)下載

2023-09-14 09:41:06 0

0 FPGA原型驗(yàn)證流程是確保FPGA(現(xiàn)場可編程門陣列)設(shè)計(jì)正確性和功能性的關(guān)鍵步驟。它涵蓋了從設(shè)計(jì)實(shí)現(xiàn)到功能驗(yàn)證的整個(gè)過程,是FPGA開發(fā)流程中不可或缺的一環(huán)。

2024-03-15 15:05:33 97

97

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論