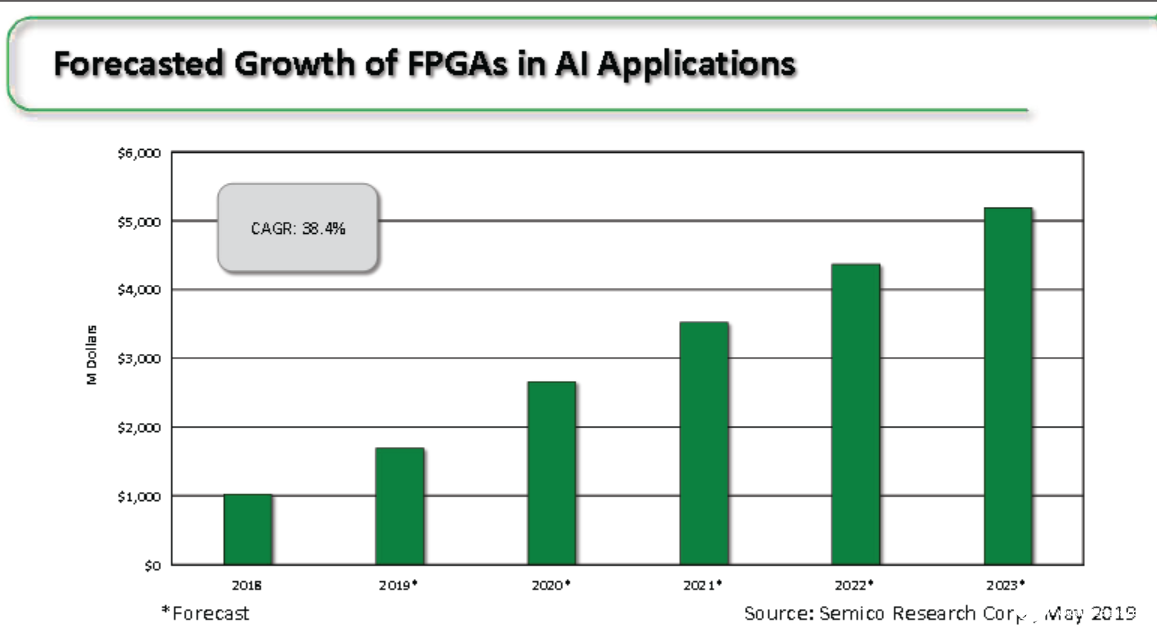

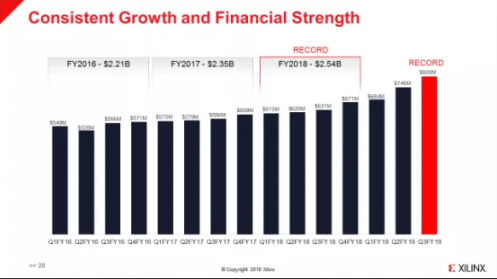

FPGA是AI/ML運算的主要芯片之一。據市場調查公司Semico Research的2019年5月數據,2018年用于AI的FPGA市值約10億美元,預計2019年為18億美元左右。到2023年的未來四年中,AI用FPGA將增長約3倍,達到52億美元(如下圖)。

這個增長是驚人的,因為過去多年來,FPGA業的年均增長率只有8%~9%。

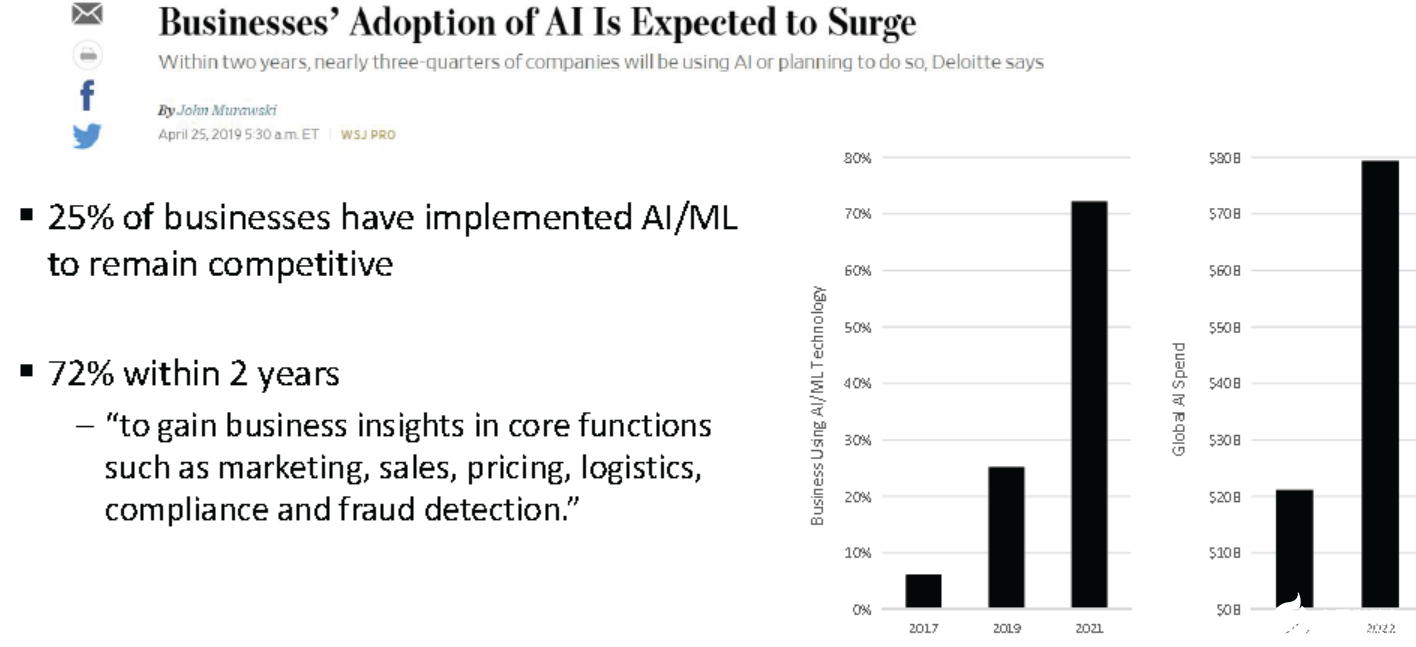

目前,25%的商業已經實現了AI/機器學習(ML),未來兩年內將達72%。帶來的好處是在核心功能方面帶來商業的洞察力,諸如市場營銷、銷售、定價、物流、合規和欺詐檢測。

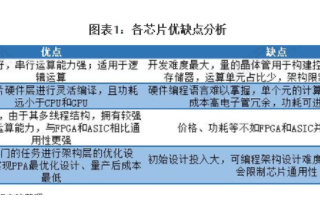

不過,這也為FPGA的傳統架構帶來了不小的挑戰。因為市面上有各種AI算法(如下圖),基本上底層是矩陣層,用高精度浮點運算,但是算法的變化趨勢是:精度/位數降低,從浮點改為定點,原因是為了把運算的復雜度降低,從而降低功耗。

數據加速有其特點,通常要有三要素:高算力,高效、豐富的存儲緩存能力,高效、大帶寬的數據運送能力。為此,FPGA芯片需要改進架構,以滿足數據加速的需要。

2、Achronix的7納米FPGA架構

近日,Achronix宣布推出突破性FPGA——Speedster7t,采用7納米工藝、TSMC流片,主要針對AI/ML(機器學習)和高帶寬網絡應用。為此,公司總裁兼CEO(首席執行官)Robert Blake向電子產品世界等介紹了新架構。

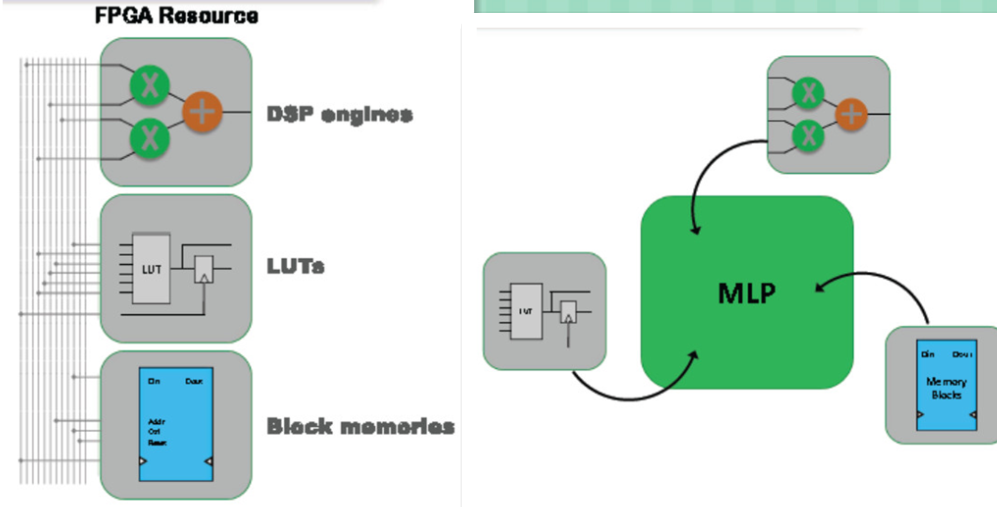

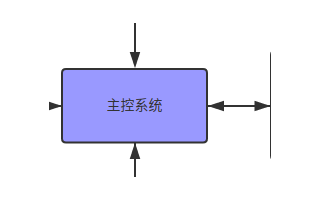

據悉,Speedster7t研發了三年。該公司至今已有十余年歷史,此前,已推出了三代FPGA。不過,為了應對AI挑戰,Speedster7t芯片的設計團隊重新設計架構,提出了兼具FPGA靈活性和ASIC高性能的新一代FPGA(如下圖)。

亮點如下。

*新的NOC(片上網絡)路由架構;

*新的機器學習處理器(MLP);

*最高速度接口,例如最新的第五代PCIe和400 Gbps以太網;

*是第一家內嵌GDDR6高帶寬內存單元的FPGA公司。

2.1 MLP

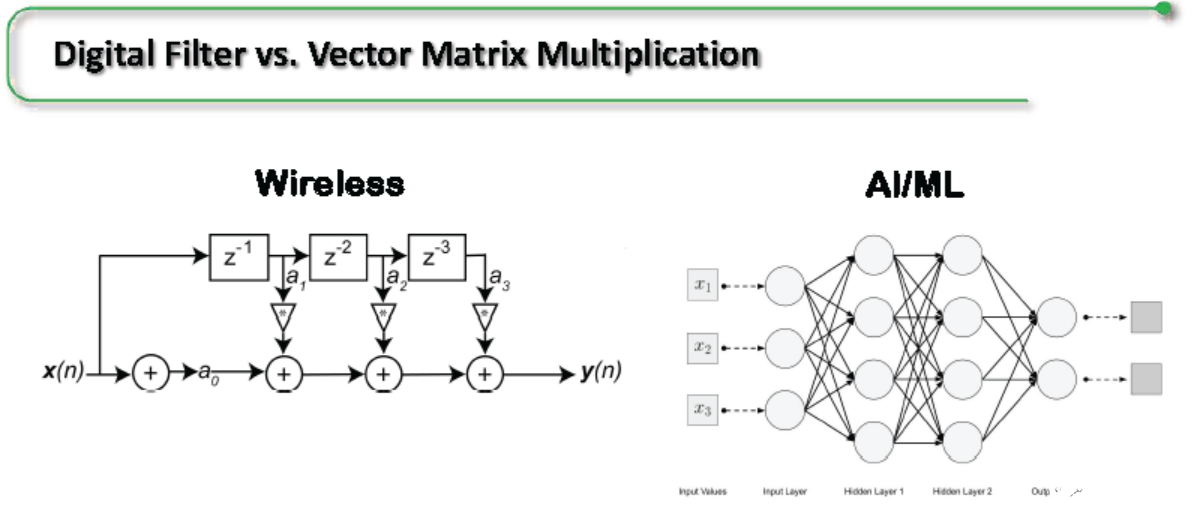

AI/ML需要矢量矩陣乘法,而傳統的帶DSP塊的FPGA的性能有限(如下圖左),新的MLP可帶來更高的性能(如下圖右)。

另外,傳統FPGA的數字濾波器也不適合(如下圖左),新的Speedster7t采用了矢量矩陣乘法。

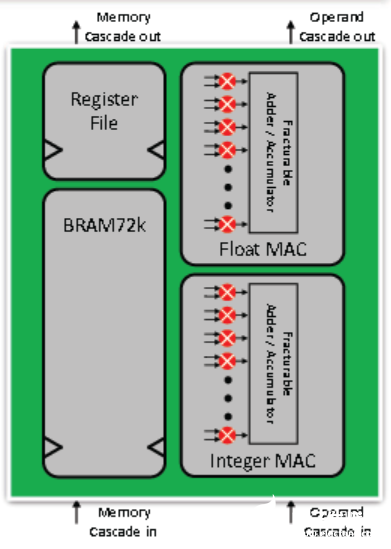

再有,新一代的Speedster7t MLP采用了專為AI/ML優化的數學塊(Math Block)(如下圖)。具有四個特點,①高密度乘陣列:每個MAC( 乘累加)支持最多32個乘法器,驅動可變精度的加法和累加器,有浮點MAC和整點MAC。②緊密相鄰的緩存塊:大塊RAM為72Kbits,寄存器文件是2Kbits。③通過運算和內存級聯功能,可以實現更復雜的算法,而無需使用FPGA布線資源。④支持多數字格式,包括浮點、整點和自定義格式。

2.2 內存層次結構和帶寬

內存在FPGA fabric(邏輯功能塊)中:每6個輸入LUT(查找表)中有2個寄存器,每個塊RAM中有72 Kbits。

率先采用GDDR6。

具有DDR4/5接口。

2.3 更高速率接口

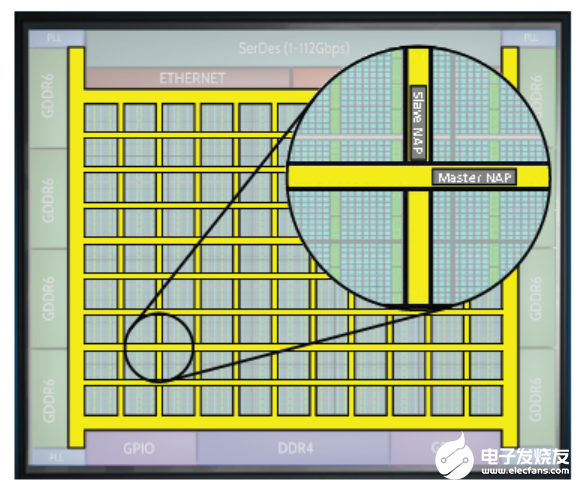

采用1~112 Gbps SerDes(串行收發器),有固化的以太網結構,硬化的第五代PCIe。

2.4 創新的二維片上網絡(NOC)

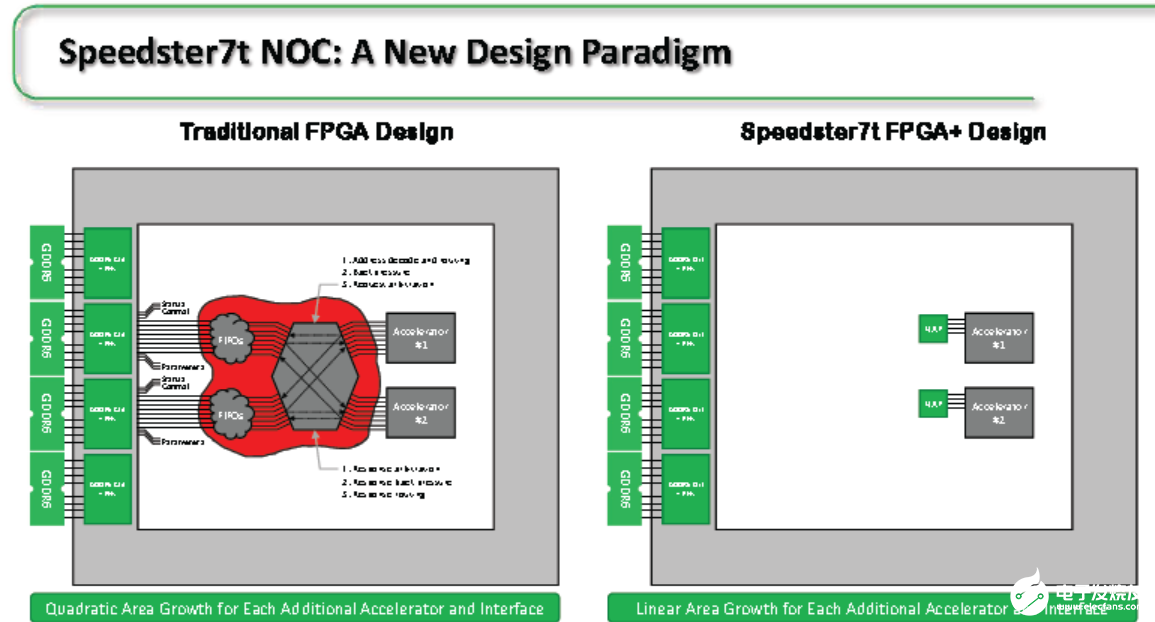

像疊加在FPGA互聯城市街道系統上的高速公路一樣,NoC支持片上處理引擎之間的高帶寬通信。例如,有的做圖像處理,有的做數據庫交流等,有了NOC,可以有效地做起來。

那么,一家友商的高端FPGA中也有高速公路架構,NOC的特點是什么?Robert稱速度更快,是市面上產品的十倍。

值得指出的是,NOC的外圍(如下圖的大黃框)是購買的IP,但是內部的構造是Achronix自己設計的。

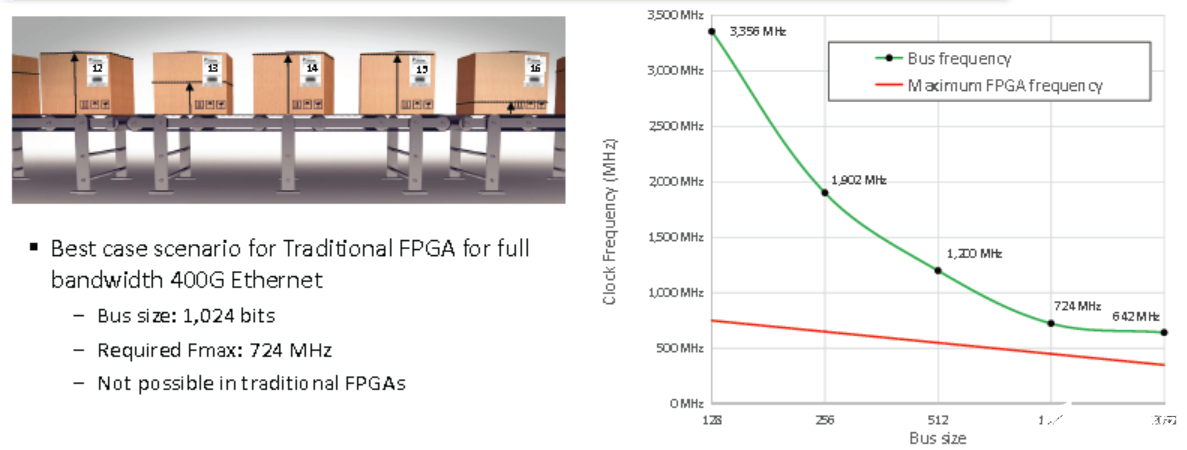

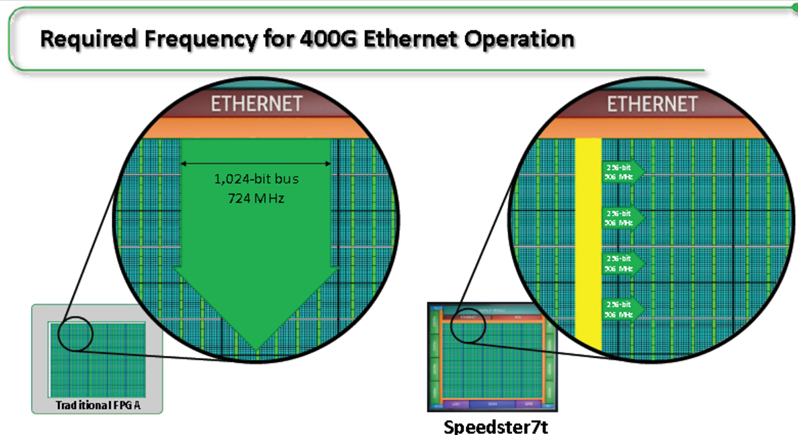

如何為400G以太網傳輸提供所需的頻率?通常采用打包方式。傳送速度需要足夠快,以確保來得及裝包。不過,包有大有小,例如視頻包較大,大包會降低效率,使得包之間有空的空間。

因此,傳統FPGA不能在任何400G以太網總線帶寬下運行得足夠快(如下圖)。

Speedster7t采用了分成多路傳輸方法(如下圖)。

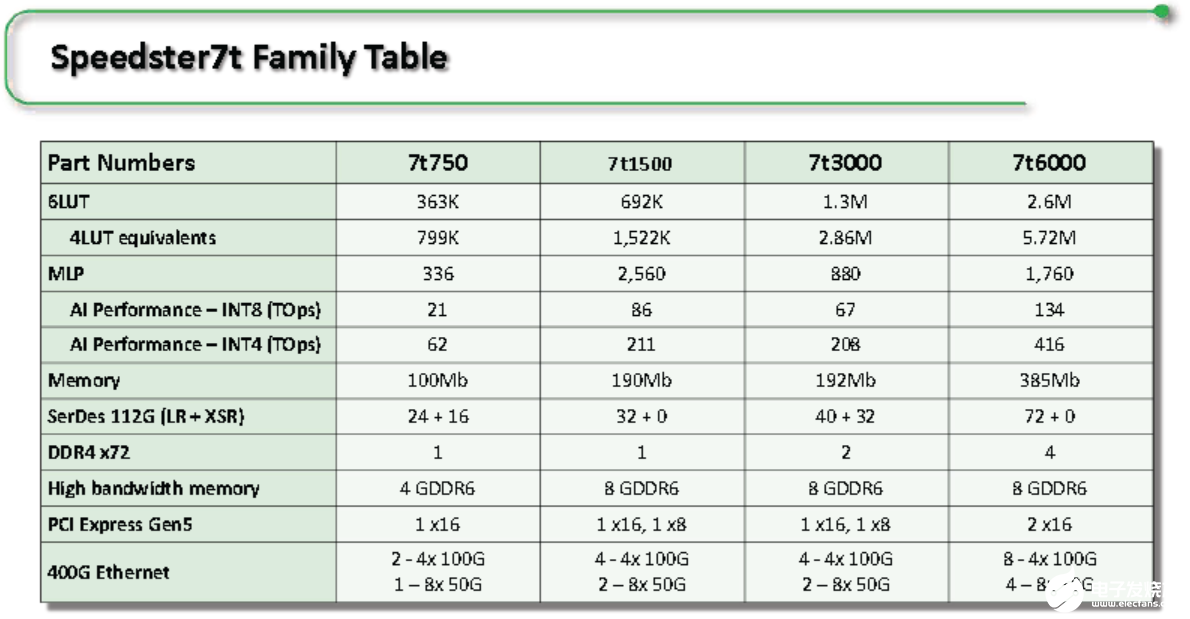

3、Speedster7t產品家族

此次發布的新芯片,預計2019年第四季度會提供樣片和加速卡,2020年量產。不過,相關的ACE軟件工具有很多創新,現在就可獲得。

4、創新性的商業模式

眾所周知,FPGA業有兩大巨擎,都有35年左右的歷史,專利和產品遍布。Achronix作為一家只有十余年歷史的公司,必須要另辟蹊徑。為此該公司定位于高端FPGA,主要應用領域是高性能數據加速,諸如高性能計算和網絡處理加速等。

不僅是上述的技術創新,該公司還有獨特的商業模式:既提供FPGA芯片,也有FPGA IP授權等業務,其IP產品——Speedcore eFPGA IP已于2016年推向市場,并于去年底推出了最新的第四代Speedcore。

Robert十分看好FPGA IP授權的前景,認為未來可能越來越多地用于ASIC,例如RF芯片是否也可以變成FPGA?這看起來似乎不可思議,但就像CPU界,二三十年前,沒人把CPU放進SoC中,而現在很常見。

現在FPGA芯片的營收占公司的比例最大,但IP授權發展速度最快。

5、評論——創新對小公司更加重要

Achronix公司的第一代FPGA產品是與Intel達成了協議,采用當時Intel最先進的工藝——22nm生產,型號為Speedster22i,意味著22nm、Intel流片。當時震動了業界,一方面人們不相信FPGA業最新工藝產品將被一家小公司做出,同時也發現Intel要涉足代工業務。

當時很多客戶雖然喜歡這家小公司的前沿產品,但不太放心,Achronix安慰說:“你可以不相信我,但你總不會不相信Intel啊!只要有Intel在,Intel就可以給客戶流片。”

沒想到幾年后,FPGA巨頭——Altera被Intel收為旗下。Achronix又轉到TSMC去流片。第四代產品叫Speedster7t,意味著7nm、TSMC流片。

而且Achronix還開辟的了新業務——IP授權模式,發展良好。

這讓大家再一次領略到初創公司在夾縫中生存時,創新的重要性。

此次FPGA架構的創新令人眼界大開,例如有些功能友商已有,Achronix的性能更高;有些架構和功能是Achronix首創的,專為AI/ML和高帶寬應用打造。

6、Achronix官方新聞稿如下

Achronix推出突破性的FPGA系列產品,以面向高帶寬數據加速應用的靈活性而將性能提升到全新高度

· 全新Speedster7t系列產品專為機器學習市場和高帶寬網絡應用而進行了優化

· 創新架構和ACE軟件工具為要求更高性能和更短設計周期的設計提供了全新范式

· Speedster7t器件采用臺積電(TSMC)的7nm FinFET工藝制造

美國加州圣克拉拉市, 2019年 5月 21日—基于現場可編程門陣列(FPGA)的硬件加速器件和高性能嵌入式FPGA(eFPGA)半導體知識產權(IP)領導性企業Achronix半導體公司(Achronix Semiconductor Corporation)今日宣布:推出創新性的、全新的FPGA系列產品,以滿足人工智能/機器學習(AI/ML)和高帶寬數據加速應用日益增長的需求。Achronix的Speedster?7t系列基于一種高度優化的全新架構,以其所具有的如同ASIC一樣的性能、可簡化設計的FPGA靈活性和增強功能,從而遠遠超越傳統的FPGA解決方案。

Speedster7t FPGA系列產品是專為高帶寬應用進行設計,具有一個革命性的全新二維片上網絡(2D NoC),以及一個高密度全新機器學習處理器(MLP)模塊陣列。通過將FPGA的可編程性與ASIC的布線結構和計算引擎完美地結合在一起,Speedster7t系列產品創造了一類全新的“FPGA +”技術。

隨著人工智能/機器學習的應用場景快速發展演進,新的解決方案都要去應對在高性能、靈活和上市時間等方面的不同需求。根據市場調研公司Semico Research的預測,人工智能應用中FPGA的市場規模將在未來4年內增長3倍,達到52億美元。

“我們正處于智能化、自學習計算的高增長階段的早期,這種計算將廣泛影響我們日的常生活。”Achronix Semiconductor總裁兼首席執行官Robert Blake表示:“Speedster7t是Achronix歷史上最令人激動的發布,代表了建立在四個架構代系的硬件和軟件開發基礎上的創新和積淀,以及與我們領先客戶之間的密切合作。Speedster7t是靈活的FPGA技術與ASIC核心效率的融合,從而提供了一個全新的‘FPGA+’芯片品類,它們可以將高性能技術的極限大大提升。”

在開發Speedster7t系列FPGA的產品過程中,Achronix的工程團隊完全重新構想了整個FPGA架構,以平衡片上處理、互連和外部輸入輸出接口(I / O),以實現數據密集型應用吞吐量的最大化,這些應用場景可見于那些基于邊緣和基于服務器的AI / ML應用、網絡處理和存儲。

Speedster7t器件采用了TSMC的7nm FinFET工藝制造,是專為接收來自多個高速來源的大量數據而設計,同時還需要將那些數據分發到可編程片上算法性和處理性單元中,然后以盡可能低的延遲來提供那些結果。Speedster7t系列產品包括高帶寬GDDR6接口、400G以太網端口和PCI Express Gen5等接口,所有這一切單元都互相連接以提供ASIC級帶寬,同時保留FPGA的完全可編程性。

“Achronix全新的Speedster7t FPGA系列產品是創新性芯片架構實現爆發的一個卓越案例,創造該架構的目的是直接面向AI應用處理大量的數據,” Semico Research公司ASIC和SoC首席市場分析師Rich Wawrzyniak說道。“通過將數學函數、存儲器和可編程性整合到其機器學習處理器中,再結合交叉芯片、二維NoC結構,從而形成了消除瓶頸和確保整個器件中數據自由流動的絕佳方法。在AI / ML應用中,內存帶寬就是一切,Achronix的Speedster7t在這一領域提供了令人印象深刻的性能指標。”

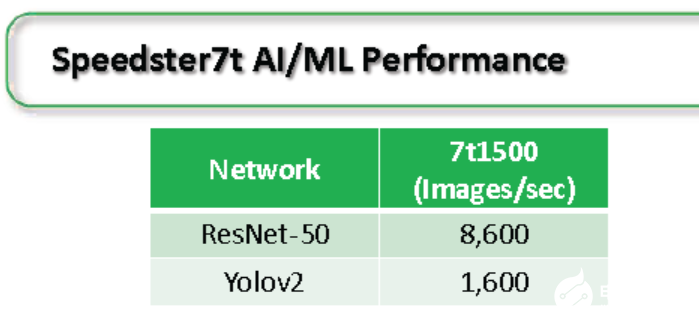

為計算性能進行了高度的優化

Speedster7t FPGA的核心是其全新機器學習處理器(MLP)中大規模的可編程計算單元平行陣列,它們可提供業界最高的、基于FPGA的計算密度。MLP是高度可配置的、計算密集型的單元模塊,可支持4到24位的整點格式和高效的浮點模式,包括對TensorFlow的16位格式的支持,以及可使每個MLP的計算引擎加倍的增壓塊浮點格式的直接支持。

MLP與嵌入式存儲器模塊緊密相鄰,通過消除傳統設計中與FPGA布線相關的延遲,來確保以750 MHz的最高性能將數據傳送到MLP。這種高密度計算和高性能數據傳輸的結合使得處理器邏輯陣列能夠提供基于FPGA的最高可用計算能力以每秒萬億次運算數量為單位(TOPS,Tera-Operations Per Second)。

世界級的帶寬

高性能計算和機器學習系統的關鍵之處是高片外存儲器帶寬,從而為多個數據流提供存儲源和緩沖。 Speedster7t器件是唯一支持GDDR6存儲器的FPGA,該類存儲器是具有最高帶寬的外部存儲器件。每個GDDR6存儲控制器都能夠支持512 Gbps的帶寬,Speedster7t器件中有多達8個GDDR6控制器,可以支持4 Tbps的GDDR6累加帶寬,并且以很小的成本就可提供與基于HBM的FPGA等效存儲帶寬。

“美光(Micron)樂于攜手Achronix去實現全球第一個面向高帶寬存儲需求而直接加載了GDDR6的FPGA產品,”美光計算與聯網業務部營銷副總裁Mal Humphrey。“像這樣的創新的和可擴展的解決方案將推動人工智能領域內的差異化,其中異構計算可選方案與高性能的存儲是加速獲得數據內涵的必需部分。”

除了這種非凡的存儲帶寬,Speedster7t器件還包括業界最高性能的接口端口,以支持極高帶寬的數據流。Speedster7t器件擁有多達72個業界最高性能的SerDes,可以達到1到112 Gbps的速度。還有帶有前向糾錯(FEC)的硬件400G以太網MAC,支持4x 100G和8x 50G的配置,以及每個控制器有8個或16個通道的硬件PCI Express Gen5控制器。

超高效率的數據移動

來自Speedster7t高速I / O和存儲器端口的數萬兆比特數據很容易淹沒傳統FPGA面向比特位的可編程互連邏輯陣列的路由容量,而Speedster7t架構包含一個可橫跨和垂直跨越FPGA邏輯陣列的創新性的、高帶寬的二維片上網絡(NOC),它們連接到所有FPGA的高速數據和存儲器接口。它們就像疊加在FPGA互連這個城市街道系統上的空中高速公路網絡一樣,Speedster7t的NoC支持片上處理引擎之間所需的高帶寬通信。NoC中的每一行或每一列都可作為兩個256位實現,單向的、行業標準的AXI通道,工作頻率為2Ghz,同時可為每個方向提供512 Gbps的數據流量。

通過在Speedster中實現專用二維 NoC, 極大地簡化了高速數據移動,并確保數據流可以輕松地定向到整個FPGA結構中的任何自定義處理引擎。最重要的是,NOC消除了傳統FPGA使用可編程路由和邏輯查找表資源在整個FPGA中移動數據流中出現的擁塞和性能瓶頸。這種高性能網絡不僅可以提高Speedster7t FPGA的總帶寬容量,還可以在降低功耗的同時提高有效LUT容量。

針對安全性至上和硬件確保應用的安全防護功能

Speedster7t FPGA系列產品在面臨第三方攻擊的威脅時,可用最先進的比特流安全保護功能應對,它們具有的多層防御能力可保護比特流的保密性和完整性。密鑰是基于防篡改物理不可克隆技術(PUF)進行加密,比特流由256位的AES-GCM加密算法進行加密和驗證。為了防止來自旁側信道的攻擊,比特流被分段,每個數據段使用單獨導出的密鑰,且解密硬件采用差分功率分析(DPA)計數器措施。 此外,2048位RSA公鑰認證協議被用來激活解密和認證硬件。用戶可以確信的是當他們加載其安全比特流時,它是預期的配置,這是因為它已通過RSA公鑰、AES-GCM私鑰和CRC校驗進行了身份驗證。

經驗證的、可向低成本ASIC轉換的途徑,用以滿足大批量需求

Achronix是唯一一家既提供獨立FPGA芯片又提供Speedcore?嵌入式FPGA(eFPGA)半導體知識產權( IP)的公司。Achronix在Speedcore eFPGA IP中采用了與Speedster7t FPGA中使用的同一種技術,可支持從Speedster7t FPGA到ASIC的無縫轉換。FPGA應用通常具有必須保持可編程性的功能,而其他固定功能則是專用于特定的系統應用。對于ASIC的轉換而言,固定功能可以被固化進ASIC結構中,從而減小芯片面積、成本和功耗。當使用Speedcore eFPGA IP將Speedster7t FPGA轉換為ASIC時,客戶有望節省高達50%的功耗并降低90%的成本。

責任編輯:gt

電子發燒友App

電子發燒友App

評論