100歐姆 1K,10K三檔量程怎么自動(dòng)換擋的電路圖

2011-08-31 12:27:35

ACEX 1K系列器件實(shí)現(xiàn)加載的方法有哪幾種?EPC2器件連接及工作原理是什么?

2021-04-15 06:38:25

ACEX1K - Programmable Logic Device Family - Altera Corporation

2022-11-04 17:22:44

/cpld的設(shè)計(jì)和優(yōu)化技巧。在討論fpga/cpld設(shè)計(jì)指導(dǎo)原則的基礎(chǔ)上,介紹了altera器件的高級(jí)應(yīng)用;引領(lǐng)讀者學(xué)習(xí)邏輯鎖定設(shè)計(jì)工具,詳細(xì)討論了時(shí)序約束與靜態(tài)時(shí)序分析方法;結(jié)合實(shí)例討論如何進(jìn)行設(shè)計(jì)優(yōu)化

2020-05-14 14:50:30

ALTERA器件選型手冊(cè)目錄 1、 MAX7000系列器件 ………………………………………………………………………………………….1 2、 MAX3000A系列器件

2012-08-10 18:24:17

Altera FPGA/CPLD設(shè)計(jì)與Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程從網(wǎng)上找到了一些Altera FPGA/CPLD經(jīng)典教材,包含夏宇聞老師的Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程(第2版)Altera FPGA/CPLD設(shè)計(jì)與Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程

2014-02-17 09:22:18

Altera FPGA/CPLD設(shè)計(jì)(高級(jí)篇)》

2012-12-06 15:51:36

《Altera FPGA_CPLD設(shè)計(jì) 基礎(chǔ)篇》是Altera官方指定培訓(xùn)中文教材,說(shuō)的較為詳細(xì),值得一看。

2013-02-25 17:42:17

:Stratix、StratixII、Cyclone、Cyclone II、ACEX 1K、APEX 20K和FLEX 10K等;</p><p align

2009-12-03 09:30:50

;amp;nbsp;FPGA:Stratix、StratixII、Cyclone、Cyclone II、ACEX 1K、APEX 20K和FLEX 10K等;</p>&

2009-12-04 09:28:56

可編程邏輯器件相關(guān)專輯 Altera-FPGA/CPLD設(shè)計(jì),從基礎(chǔ)篇到高級(jí)篇由淺入深幫助大家學(xué)習(xí)

2018-10-08 15:43:55

》, Volume I,Section I,3)。Cyclone III中的ram塊是M9k,每一塊中包含8192個(gè)存儲(chǔ)位,加上校驗(yàn)位共9216位,故稱M9k。每個(gè)ram塊可配置為表3-1中的各種模式

2015-09-05 18:59:57

我想用單片機(jī)配置altera 的CPLD epm240資料上寫(xiě)的要用到 cpld MSEL1、MSEL0,NSTATUS等引腳 但是這三個(gè)引腳在cpld的哪個(gè)位子了??

2011-11-09 21:25:51

、MAX7000 系列、Mercury、FELX10KE、APEX20KE、APEX20KC、ACEX1K、APEX II和 Stratix 等。 其開(kāi)發(fā)工具 MAX+PLUS II 是較成功

2019-03-04 14:10:13

最吸引我的,無(wú)論是目前炒的比較火的物聯(lián)網(wǎng)智能家居還是手持設(shè)備,藍(lán)牙、wifi,其具有的硬件的加密密鑰存儲(chǔ)和加密應(yīng)對(duì)措施,極低的功耗,都使其具有很大的優(yōu)勢(shì)出于各種安全性考慮,這個(gè)都是很好的選擇。三種加密器件

2016-08-24 11:37:39

三種復(fù)位方式比較

2012-08-16 17:31:50

三種常見(jiàn)的PCB錯(cuò)誤是什么

2021-03-12 06:29:32

三種常見(jiàn)的光刻技術(shù)方法根據(jù)暴光方法的不同,可以劃分為接觸式光刻,接近式光刻和投影式光刻三種光刻技術(shù)。 ◆投影式暴光是利用透鏡或反射鏡將掩膜版上的圖形投影到襯底上的暴光方法.在這種暴光方法中,由于掩膜

2012-01-12 10:56:23

的Modbus TCP Slave的一個(gè)保持寄存器的值,并將其放入變量Input_Word_1中。其中變量Input_Word_1的值被放入過(guò)程映像中,下面將采用三種方法讀取它的值。在此之前,首先使用piTest

2021-02-02 16:40:08

Teledyne e2v為系統(tǒng)設(shè)計(jì)師提供的定制方案處理器功耗的背景知識(shí)三種調(diào)整處理器系統(tǒng)功耗的方法

2021-01-01 06:04:09

三種遠(yuǎn)程測(cè)控終端(RTU)產(chǎn)品之間的比較

2021-05-28 06:27:08

AVR 系列單片機(jī)內(nèi)部有三種類型的被獨(dú)立編址的存儲(chǔ)器,它們分別為:Flash 程序存儲(chǔ)器、內(nèi)部SRAM 數(shù)據(jù)存儲(chǔ)器和EEPROM 數(shù)據(jù)存儲(chǔ)器[1]。Flash 存儲(chǔ)器為1K~128K 字節(jié),支持并行

2021-11-23 08:22:22

下面跟大家分享Altium Designer畫(huà)元器件封裝的三種方法。如有錯(cuò)誤,望大家指正。

2019-07-22 06:47:13

或ACEX1K系列等。盡管FPGA和CPLD都是可編程ASIC器件,有很多共同特點(diǎn),但由于CPLD和FPGA結(jié)構(gòu)上的差異,具有各自的特點(diǎn):

2019-07-01 07:36:55

IIC總線通訊接口器件的CPLD實(shí)現(xiàn)摘要:介紹了采用ALTERA公司的可編程器件EPF10K10LC84-3實(shí)現(xiàn)IIC總線的通訊接口的基本原理,并給出了部分的VHDL語(yǔ)言描述。該通訊接口與專用的接口芯片相比,具有使用靈活、系統(tǒng)配置方便的特點(diǎn)。 [/hide]

2009-10-30 14:57:35

QSPI特點(diǎn)QSPI三種工作模式

2020-12-31 06:36:55

提供方式 CD-ROM 免費(fèi)從Altera網(wǎng)站的下載中心下載,或從Quartus II 軟件Starter Suite CD-ROM中獲取 許可 永久 150天 器件支持 全部 ACEX? 1K

2012-08-15 12:30:03

STM32三種啟動(dòng)方式是什么

2021-12-15 07:16:54

01STM32的三種啟動(dòng)模式STM32有三種啟動(dòng)模式:FLASH啟動(dòng)、SRAM啟動(dòng)和系統(tǒng)存儲(chǔ)器啟動(dòng),通常三種啟動(dòng)方式由外部引腳boot0和boot1的電平?jīng)Q定。每個(gè)系列boot0和boot1電平對(duì)應(yīng)

2021-08-18 07:52:23

一、啟動(dòng)模式(Boot modes)閱讀:STM32中文參考手冊(cè)_V10.pdf 查看啟動(dòng)配置(Boot modes)。在STM32F10xxx里,可以通過(guò)BOOT[1:0]引腳選擇三種不同啟動(dòng)模式

2021-08-05 07:25:51

使用三種模式與外部的觸發(fā)信號(hào)同步:標(biāo)準(zhǔn)觸發(fā)模式、復(fù)位觸發(fā)模式和門控觸發(fā)模式。標(biāo)準(zhǔn)觸發(fā)模式:說(shuō)白了就是使用外部信號(hào)觸發(fā)內(nèi)部計(jì)數(shù)器啟動(dòng),然而如何配置呢,看手冊(cè):下面根據(jù)官方給出的步驟配置寄存器:vo...

2021-08-19 08:40:24

while的三種使用形式是什么樣的?

2021-11-02 08:35:34

學(xué)會(huì)CPLD的系統(tǒng)設(shè)計(jì)技術(shù)。本書(shū)以ALTERA公司的系列芯片為目標(biāo)載體,簡(jiǎn)要分析了可編程邏輯器件的結(jié)構(gòu)和特點(diǎn),以及相應(yīng)開(kāi)發(fā)軟件的使用方法,同時(shí),還用大量篇幅介紹了初學(xué)者最容易掌握的Verilog

2018-03-30 15:07:50

的文章提到,測(cè)速的三種方法:(1)在規(guī)定時(shí)間內(nèi)測(cè)量所產(chǎn)生的脈沖個(gè)數(shù)來(lái)獲得被測(cè)速度,稱為M法測(cè)速;(2)測(cè)量相鄰兩個(gè)脈沖的時(shí)間來(lái)測(cè)量速度,稱為T法測(cè)速;(3)同時(shí)測(cè)量檢測(cè)時(shí)間和在此時(shí)...

2021-09-13 07:08:01

一燈雙控的三種接線方法有哪些利弊

2021-03-11 07:10:04

。AS由FPGA器件引導(dǎo)配置操作過(guò)程,它控制著外部存儲(chǔ)器和初始化過(guò)程,EPCS系列:如EPCS1,EPCS4配置器件專供AS模式,目前只支持 Cyclone系列。使用Altera串行配置器件來(lái)完成

2023-04-24 15:34:27

他勵(lì)直流電動(dòng)機(jī)的三種制動(dòng)方法各有什么特點(diǎn)呢?求解

2023-03-21 10:14:21

伺服電機(jī)的三種測(cè)速方法1.M法: (1)M法:開(kāi)一個(gè)時(shí)間窗口,在這個(gè)時(shí)間窗口內(nèi)數(shù)編碼器脈沖個(gè)數(shù), 速度越快,當(dāng)然對(duì)于時(shí)間窗口數(shù)到的脈沖數(shù)就越多。 (2)角速度計(jì)算:角速度是指在時(shí)間窗口內(nèi)的平均

2016-01-28 10:13:47

方法是以下三種。 比較法:拆下懷疑有問(wèn)題的光耦,用萬(wàn)用表測(cè)量其內(nèi)部二極管、三極管的正反向電阻值,用其與好的光耦對(duì)應(yīng)腳的測(cè)量值進(jìn)行比較,若阻值相差較大,則說(shuō)明光耦已損壞。[align=left] 數(shù)字

2013-05-06 15:26:02

下面跟大家分享Altium Designer畫(huà)元器件封裝的三種方法。如有錯(cuò)誤,望大家指正。

2019-07-24 08:05:17

器件選型。 1. Compact系列CPLD總體介紹 Compact 系列器件是采用 55nm 工藝制造的低成本、高密度IO并具有非易失性的CPLD產(chǎn)品,采用先進(jìn)的封裝技術(shù),提供上電瞬間啟動(dòng)功能;其中

2024-03-16 07:08:16

從不同的側(cè)重點(diǎn)給出了幾種拓?fù)洌瑢?duì)其進(jìn)行分析比較三種拓?fù)溆衅涓髯缘挠腥秉c(diǎn),如何來(lái)選擇它們?

2021-04-07 06:05:16

Redis筆記(1)——安裝、卸載、三種方法啟動(dòng)Redis,Redis命令使用(干貨十足),Redis兩種方法設(shè)置密碼,時(shí)間復(fù)雜度(更完善哦~)

2020-06-08 16:09:26

基礎(chǔ)。我們知道了Spring Boot是個(gè)什么了,那么我們又該如何啟動(dòng)Spring Boot應(yīng)用呢?這里小編給大家推薦常用的三種方法。分別是IDEA編輯器啟動(dòng)、命令啟動(dòng)、java命令jar文件啟動(dòng)。下面

2021-01-14 17:33:42

本文介紹一個(gè)用微控制器在系統(tǒng)配置Lattice MACH4000系列CPLD器件的方案。

2021-04-30 06:43:20

如何采用Altera的CPLD器件實(shí)現(xiàn)時(shí)間統(tǒng)一系統(tǒng)的B碼源設(shè)計(jì)?

2021-05-07 06:21:24

藍(lán)牙無(wú)線組網(wǎng)的優(yōu)點(diǎn)是什么?常見(jiàn)的三種無(wú)線接入方式是什么?藍(lán)牙無(wú)線組網(wǎng)原理與上網(wǎng)方案分享

2021-05-26 06:33:11

我是個(gè)新手 剛剛接觸labview3天 ,通過(guò)查閱帖子 ,發(fā)現(xiàn)目前有三種方法:1.使用labview Interface for Arduino,這種需要把LVIFA_Base燒錄進(jìn)Arduino

2017-05-27 10:35:23

推薦ALTERA的FPGA電源器件選型手冊(cè)Power Management Reference Guide for Altera? FPGAs and CPLDsThis information

2009-12-17 15:21:27

的Flex系列、ACEX、APEX、Cyclone系列也是基于SRAM的可重構(gòu)邏輯。支持重構(gòu)的FPGA器件有數(shù)量逐漸增加的趨勢(shì)。但目前價(jià)格相對(duì)偏高。

2011-05-27 10:23:28

數(shù)字信號(hào)的三種糾錯(cuò)方法

2012-08-20 12:49:22

現(xiàn)在altera的CPLD芯片用的最多是哪幾款啊

2013-10-16 18:51:55

CPLD是altera的7256,20塊電路板有兩塊始終無(wú)法下載程序,下載器應(yīng)該是好的,量了CPLD的外圍,供電3.28V正常。板下載插針和CPLD之間是四路JTAG信號(hào),TCK,TDO,TMS,TDI。四引腳對(duì)地都不短路,四路串的是1K的電阻。

2017-07-13 11:48:55

盤古1K/2K 開(kāi)發(fā)套件是基于紫光同創(chuàng) FPGA 開(kāi)發(fā)平臺(tái)的開(kāi)發(fā)套件,以紫光同創(chuàng) Compa系列PGC1KG-LPG100 / PGC2KG-LPG100 器件為核心,預(yù)留豐富的擴(kuò)展 IO 及數(shù)碼管

2023-08-02 14:20:11

ⅡPro和和Virtex-ⅡProX系列產(chǎn)品.ppt2.2.1 FLEX系列產(chǎn)品.ppt2.2.2FLEX系列產(chǎn)品.ppt2.2.3 ACEX1K系列產(chǎn)品.ppt2.2.4 APEX系列

2012-12-06 16:10:55

原理根據(jù)讀取信號(hào)對(duì)應(yīng)輸出不同狀態(tài)24V、地 、懸空,三種狀態(tài)。現(xiàn)在想到二種方法,大家覺(jué)的哪個(gè)好?第二種繼電器方法好像是真正的懸空

2019-11-14 09:54:44

Altera FLEX/ACEX芯片結(jié)構(gòu)是如何構(gòu)成的?Intel XScale PXA270處理器的系統(tǒng)存儲(chǔ)器接口怎樣去設(shè)計(jì)?Linux下的ACEX1K50設(shè)備驅(qū)動(dòng)是如何實(shí)現(xiàn)的?

2021-04-30 06:44:14

關(guān)于ACEX1K的I/O腳驅(qū)動(dòng)能力. ALTERA 計(jì)算功耗的datasheet 中:對(duì)ACEX1K器件, PDCOUT (power of steady-state outputs)的計(jì)算就是根據(jù)IOH, IOL來(lái)計(jì)算的, 能否告訴我ACEX1K芯片的IOH, IOL分別是多少?

2019-08-07 00:00:34

使用ADA4895-1ARJZ時(shí),負(fù)載約1k歐,反向放大,系統(tǒng)電源±6V,正負(fù)電均串聯(lián)51歐(150歐)后給運(yùn)放供電。經(jīng)常發(fā)現(xiàn)器件損壞,而且是運(yùn)放電源被拉至±1.2~±2V左右,而正常工作時(shí)運(yùn)放電源約±5.4V。請(qǐng)問(wèn)容易壞的原因是什么,改進(jìn)方法除了單獨(dú)用±5V還有嗎?

2018-07-30 09:34:31

手冊(cè)上看到STM32F030 的FLASH 擦寫(xiě)次數(shù)只有1K,真的只有1K么?051系列的手冊(cè)上是10K,

2018-11-20 08:35:54

XC9500系列CPLD器件是什么?XC9500系列CPLD器件遙控編程的實(shí)現(xiàn)方法有哪些?如何實(shí)現(xiàn)CPLD遙控編程?

2021-04-27 07:15:42

Flash中的格式以及如何燒寫(xiě)Flash的方法:part1;part2 。 4、PS模式 這里把PS和FPP一起講,無(wú)非一個(gè)串行、一個(gè)并行。這兩種模式傳統(tǒng)使用Altera的Enhance配置芯片或者

2015-01-28 10:27:03

進(jìn)程類型進(jìn)程的三種狀態(tài)

2021-04-02 07:06:39

電路無(wú)疑是一種很好的解決方法。ACEX 1K器件是Altera公司著眼于通信、音頻處理及類似場(chǎng)合的應(yīng)用而推出的芯片系列,ACEX1K器件正逐步取代FLEX l0K系列成為首選的中規(guī)模器件產(chǎn)品。它具有

2019-06-18 06:05:34

《Altera FPGA/CPLD設(shè)計(jì)(高級(jí)篇)》結(jié)合作者多年工作經(jīng)驗(yàn),深入地討論了Altera FPGA/CPLD的設(shè)計(jì)、優(yōu)化技巧。在討論FPGA/CPLD設(shè)計(jì)指導(dǎo)原則的基礎(chǔ)上,介紹了Altera器件的高級(jí)應(yīng)用;引領(lǐng)讀者

2009-02-12 09:19:12 4799

4799 介紹利用Altera 公司CPLD 器件實(shí)現(xiàn)對(duì)電機(jī)高精度、寬范圍調(diào)速的控制方案,并給出簡(jiǎn)明扼要的VHDL 程序結(jié)構(gòu)與仿真結(jié)果。

2009-05-15 14:00:03 23

23 altera fpga/cpld設(shè)計(jì) 基礎(chǔ)篇結(jié)合作者多年工作經(jīng)驗(yàn),系統(tǒng)地介紹了FPGA/CPLD的基本設(shè)計(jì)方法。在介紹FPGA/CPLD概念的基礎(chǔ)上,介紹了Altera主流FPGA/CPLD的結(jié)構(gòu)與特點(diǎn),并通過(guò)豐富的實(shí)例講解

2009-07-10 17:35:45 57

57 Altera 公司出品系列器件所用設(shè)計(jì)軟件――Quartus®II,提供了一種其獨(dú)有的優(yōu)化方法:邏輯鎖定(LogicLock)。本文介紹了一種在實(shí)際工程中應(yīng)用邏輯鎖定的方法,并加以仿真驗(yàn)證

2009-09-03 08:39:59 11

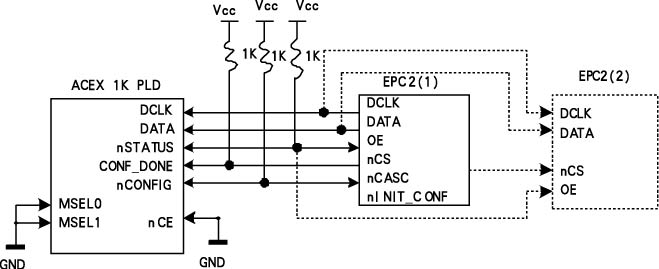

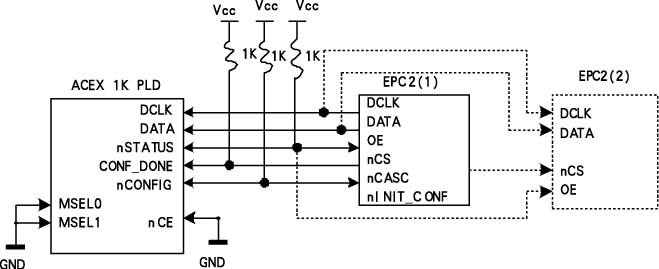

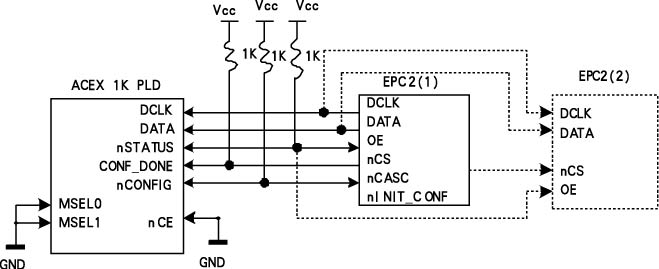

11 特征基于SRAM的LUT設(shè)備的配置設(shè)備提供以下特性:■配置Altera ACEX? 1K、APEX? 20K(包括APEX 20K、APEX 20KC和APEX 20KE)、APEX II

2023-03-07 18:54:42

摘要:在比較了ORCAD/PSPICE,PROTEL,Electronics Workbench三種仿真軟件各自特點(diǎn)的基礎(chǔ)上,介紹了把基于SPICE語(yǔ)言的器件模型加入三種軟件的方法,實(shí)現(xiàn)了三種軟件間器件模型的互相調(diào)用

2010-05-10 09:03:42 95

95 EPM1270F256C4N,ALTERA/阿爾特拉,介紹MAX?II系列即時(shí)開(kāi)啟非易失性CPLD基于0.18-μ,6層金屬閃存工藝,密度從240到2210個(gè)邏輯元件(LE)(128至22

2023-10-24 15:38:16

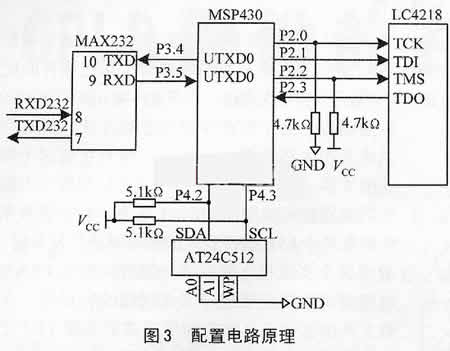

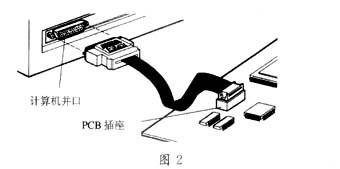

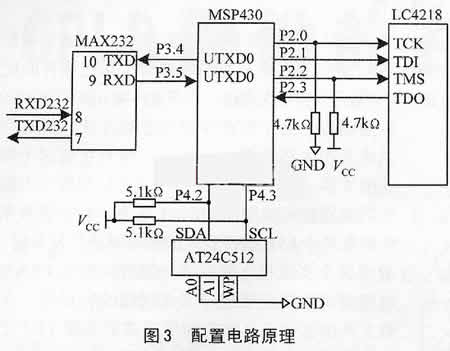

用單片機(jī)配置CPLD器件

ALTERA公司的可編程序邏輯器件APEX20K、FLEX10K和FLEX6000雖應(yīng)用廣泛,但由于其內(nèi)部采用SRAM存儲(chǔ)配置數(shù)據(jù),每次系統(tǒng)上電時(shí),必須用配置芯片對(duì)其進(jìn)行配置

2009-03-28 16:18:06 1071

1071

【摘 要】 介紹利用MAX+PLUSⅡ軟件對(duì)Altera公司的CPLD進(jìn)行圖形設(shè)計(jì)、編譯以及在系統(tǒng)編程的基本方法和步驟。 關(guān)鍵詞:MAX+

2009-05-15 21:56:09 844

844

以下是引用片段: 摘要: 介紹一種利用微控制器動(dòng)態(tài)配置CPLD器件的方法。將配置文件存放在存儲(chǔ)器中,配置文件中的控制代碼驅(qū)動(dòng)在微處理器中運(yùn)行的配置引擎;將配置文件中的配置信息通過(guò)JTAG口移入

2009-06-20 10:44:21 3034

3034

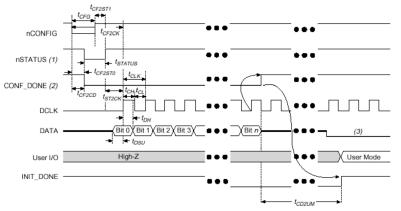

摘 要 :介紹ACEX 1K系列器件的配置方法,對(duì)幾種方法進(jìn)行了分析對(duì)比,并著重論述了應(yīng)用配置器件配置 ACEX 1K系列器件的優(yōu)點(diǎn)。

關(guān)鍵詞 :CPL

2009-06-20 10:51:54 478

478

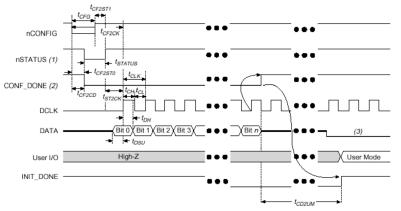

一、 配置方式

ALTERA CPLD器件的配置方式主要分為兩大類:主動(dòng)配置方式和被動(dòng)方式。主動(dòng)配置方式由CPLD器件引導(dǎo)配置操作過(guò)程,它控制著外部存儲(chǔ)器和

2009-06-20 10:58:14 1928

1928 摘要: 介紹了DDFS的原理和Altera公司的FPGA器件ACEX 1K的主要特點(diǎn),給出了用ACEX 1K系列器件EP1K10TC144-1實(shí)現(xiàn)數(shù)字頻率合成器的工作原理、設(shè)計(jì)思路、電路結(jié)構(gòu)和仿真結(jié)

2009-06-20 14:02:25 844

844

Altera增強(qiáng)MAX II系列,進(jìn)一步拓展其CPLD應(yīng)用

Altera公司宣布,提供工業(yè)級(jí)溫度范圍以及功耗更低的MAX IIZ器件,從而進(jìn)一步增強(qiáng)了MAX II CPLD系列。MAX IIZ CPLD完美的結(jié)合了邏輯

2009-11-05 09:53:58 1283

1283 Altera提供全面的定制邏輯器件系列產(chǎn)品FPGA、ASIC和CPLD。 學(xué)會(huì)以下術(shù)語(yǔ)有助于你加速實(shí)現(xiàn)Altera器件的開(kāi)發(fā)。 自適應(yīng)邏輯模塊(ALM) 協(xié)議實(shí)現(xiàn)配置(CvP) 嵌入式HardCopy模塊......

2012-06-04 14:02:43 20

20 本資料是關(guān)于Altera公司基本器件的主要介紹(主要特性、優(yōu)勢(shì)、適用配置器件、型號(hào)、引腳、下載電纜、軟件等) 目 錄 1、 MAX7000系列器件 2、 MAX3000A系列器件 3、 MAX II 系列器件 4、

2012-08-15 14:58:49 60

60 altera FPGA/CPLD高級(jí)篇(VHDL源代碼)

2012-11-13 14:40:38 134

134 Altera FPGA_CPLD設(shè)計(jì)(實(shí)例源代碼)

2013-09-09 16:09:23 442

442 下載的PLD稱之為FPGA。把Flash、EEPROM框架或乘積項(xiàng)框架的PLD稱為CPLD。 Altera把自己的PLD產(chǎn)品MAX系列/FLEX/ACEX/APEX系列稱為CPLD。由于FLEX

2017-06-19 09:59:13 3996

3996 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA教程之ALTERA的CPLD與FPGA器件的詳細(xì)資料說(shuō)明主要內(nèi)容包括了:一、Altera器件一般介紹,二、MAX 7000 系列器件,三、FLEX10K系列器件,四、邊界掃描測(cè)試

2019-02-27 17:27:31 15

15 本文檔詳細(xì)介紹的是FPGA教程之CPLD和FPGA的配置與下載的詳細(xì)資料說(shuō)明主要內(nèi)容包括了:一、CPLD/FPGA器件的配置,二、MAX系列非易失性器件的下載配置,三、FLEX/ACEX系列FPGA的下載配置,四、ALTERA的編程文件

2019-02-28 09:56:18 17

17 FPGA CPLD可編程邏輯器件的在系統(tǒng)配置方法(深圳市村田電源技術(shù)有限公司)-FPGA CPLD可編程邏輯器件的在系統(tǒng)配置方法? ? ? ? ? ? ? ? ? ?

2021-09-18 10:51:20 13

13 Altera FPGA CPLD學(xué)習(xí)筆記(肇慶理士電源技術(shù)有限)-Altera FPGA CPLD學(xué)習(xí)筆記? ? ? ? ? ? ? ? ?

2021-09-18 10:54:41 79

79 CPLD的MAX系列器件庫(kù)max-13.0.1.232

2022-12-21 17:26:11 4

4

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論