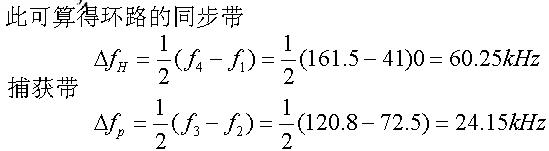

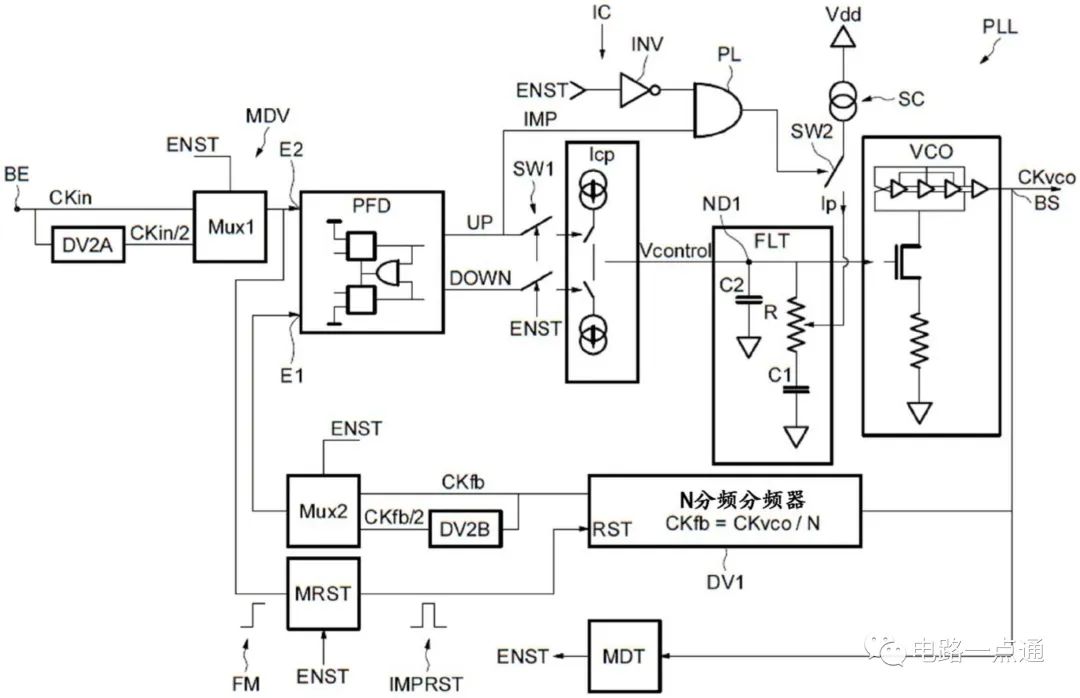

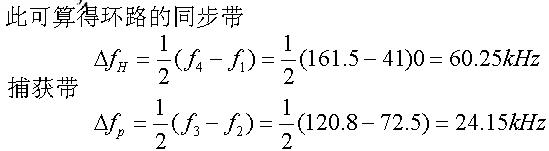

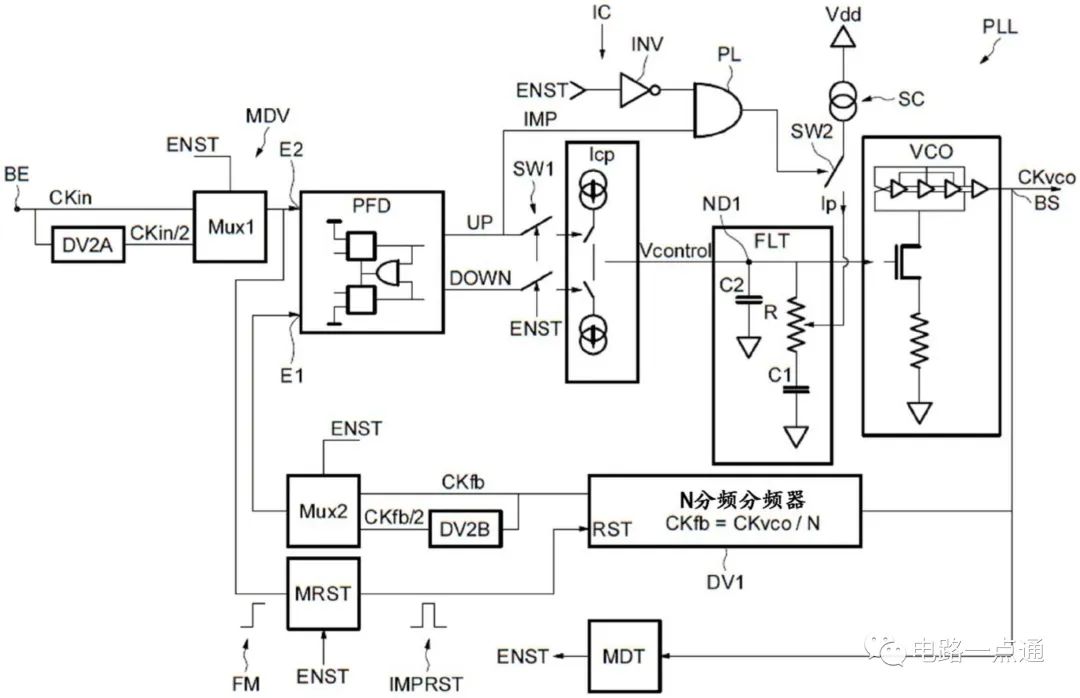

本文采用一種基于比例積分(PI)控制算法的環路濾波器應用于帶寬自適應的全數字鎖相環,建立了該鎖相環的數學模型

2010-10-14 10:03:25 1271

1271

本文針對傳統鎖相環所存在的鎖相范圍窄、環路帶寬和控制參數固定、以及提高鎖相速度與減小穩態誤差相互制約等問題,提出了一種新型帶寬自適應全數字鎖相環的設計方案。該設計方案中的系統采用比例積分控制

2014-01-17 11:33:47 2508

2508

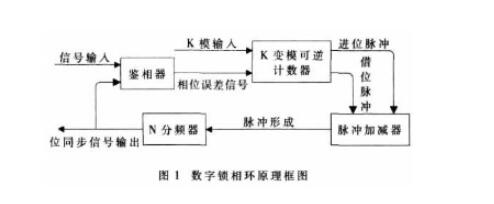

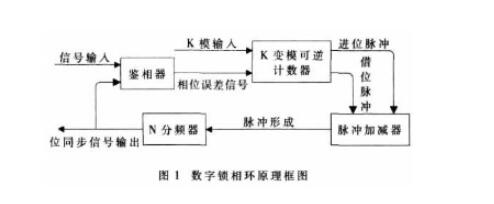

本文在說明全數字鎖相環的基礎上,提出了一種利用FPGA設計一階全數字鎖相環的方法,并給出了關鍵部件的RTL可綜合代碼,并結合本設計的一些仿真波形詳細描述了數字鎖相環的工作過程,最后對一些有關

2018-10-25 09:17:13 8237

8237 該文章是完全原創,用最簡潔的語言講清楚FPGA實現負反饋的精要。震撼!FPGA實現負反饋控制純數字鎖相環!.zip (225.26 KB )

2019-04-30 04:50:41

Phase-Locked Loop)逐步發展起來。所謂全數字鎖相環,就是環路部件全部數字化,采用數字鑒相器、數字環路濾波器、數控振蕩器構成鎖相環路,并且系統中的信號全是數字信號。與傳統的模擬電路實現的鎖相環

2010-03-16 10:56:10

本帖最后由 gk320830 于 2015-3-7 20:18 編輯

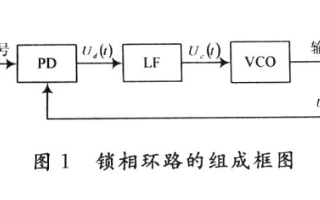

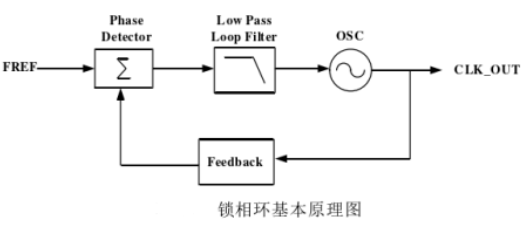

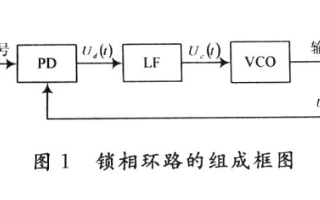

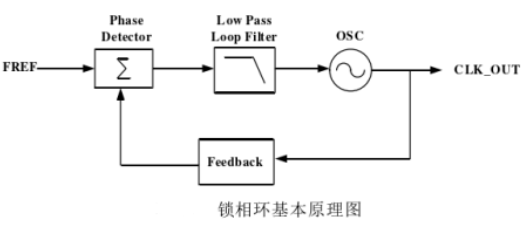

鎖相環的原理,特性與分析所謂鎖相環路,實際是指自動相位控制電路(APC),它是利用兩個電信號的相位誤差,通過環路自身調整作用,實現頻率準確跟蹤的系統,稱該系統為鎖相環路,簡稱環路,通常用PLL 表示。

2008-08-15 13:18:46

鎖相環路中的反饋信號是正反饋還是負反饋呢?

2023-04-13 11:28:35

鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL,Phase-Locked Loop)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號

2022-01-11 06:34:28

鎖相環路由哪些組成?它的基本特性是什么?應用于哪些領域?

2021-04-12 06:58:54

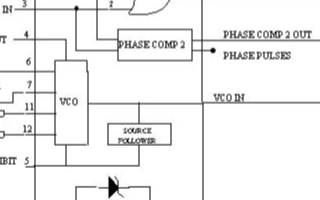

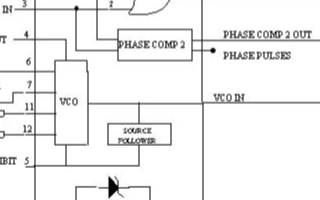

介紹了鎖相環路的基本原理,分析了集成鎖相環芯片ADF4106的工作特性,給出了集成鎖相環芯片ADF4106的一個應用實例,為高頻頻率合成器的設計提供了很好的思路。 關鍵詞:ADF4106,鎖相環,頻率合成器,環路濾波器

2019-07-04 07:01:10

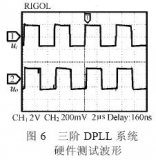

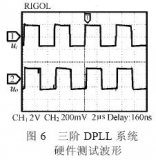

HDL硬件描述語言對優化前后的算法進行了編碼實現。仿真和實驗結果表明,優化后的數字三相鎖相環大大節省了FPGA的資源,并能快速、準確地鎖定相位,具有良好的性能。關鍵詞:FPGA;三相鎖相環;乘法復用;CORDIC

2019-06-27 07:02:23

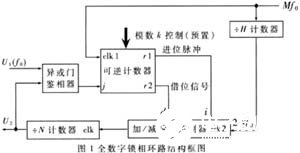

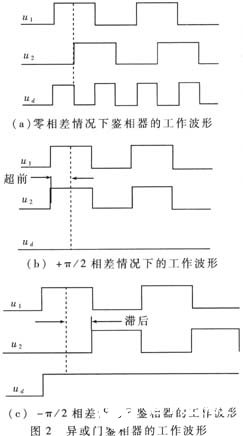

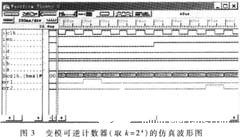

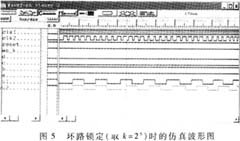

隨著集成電路技術的不斷進步,數字化應用逐漸普及,在數字通信、電力系統自動化等方面越來越多地運用了數字鎖相環。它的好處在于免去了模擬器件的繁瑣,而且成本低、易實現、省資源。本文綜合以上考慮,在一片FPGA中以Quartus II為平臺用VHDL實現了一個全數字鎖相環功能模塊,構成了片內鎖相環。

2019-10-10 06:12:52

鎖相環是什么工作原理?如何采用FPGA與頻率綜合器ADF4111相結合的方法實現數字鎖相式頻率源的設計?

2021-04-14 07:00:20

全數字鎖相環由那幾部分組成?數字鎖相環的原理是什么?如何采用VHDL實現全數字鎖相環電路的設計?

2021-05-07 06:14:44

由于一般的晶振受限于工藝與成本,做不到很高的頻率,可在需要高頻應用時,由相應的器件VCO,實現轉成高頻,但并不穩定,故利用鎖相環路來實現穩定且高頻的時脈沖訊號。本例通過MC9S12XS128這款

2021-12-10 06:26:47

經典數字鎖相環路結構及工作原理是什么?改進的數字鎖相環結構及工作原理是什么怎樣對改進的數字鎖相環進行仿真?

2021-04-20 06:47:12

數字鎖相環頻率合成系統的工作原理CPU控制數字鎖相環頻率合成系統FPGA實現

2021-04-09 06:20:37

工程師您好:ADF4351內部集成VCO振蕩器,如果結合外部環路濾波器和外部參考時鐘頻率能構成數字鎖相環嗎?如果不能是不是因為ADF4351內部沒有鑒相器,如果我想做數字鎖相環還要和ADF4002合用嗎?能實現位同步嗎?期待您們的答復!

2018-09-14 14:23:29

我剛接觸鎖相環沒多長時間,最近想使用ADF4106搭建一個雙環鎖相環,我閱讀的資料都沒有說主環路環路濾波器參數計算問題,我想咨詢專家ADIsimPLL是否可以仿真計算雙環鎖相環,如果可以具體怎么考慮,如果可以告訴我一些主環路環路帶寬的知識就更好了.

2019-03-07 10:34:03

概述:LMX2430是一款高頻鎖相環路芯片,它可在2.25V至2.75V的電壓范圍內操作。這三款芯片的其他功能包括可隨意選擇的同步或異步停機模式、1mA或4mA的可編程電荷泵電流、內置超時計數器的快速鎖定技術、...

2021-04-08 07:24:00

LMX2433是一款高頻鎖相環路芯片,它可在2.25V至2.75V的電壓范圍內操作。這三款芯片的其他功能包括可隨意選擇的同步或異步停機模式、1mA或4mA的可編程電荷泵電流、內置超時計數器的快速鎖定

2021-04-13 07:27:00

高頻鎖相環路LMX2434資料下載內容包括:LMX2434引腳功能LMX2434內部方框圖

2021-03-29 06:27:34

第1章 鎖相環路的基本工作原理第1節 鎖定與跟蹤的概念第2節 環路組成第3節 環路的動態方程第4節 一階鎖相環路的捕獲、鎖定與失

2008-04-21 08:52:00 142

142 智能全數字鎖相環的設計

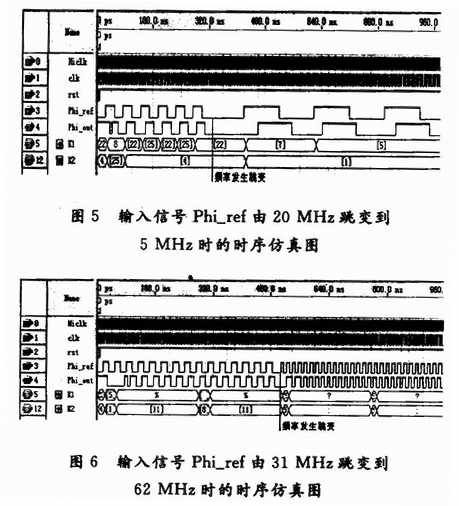

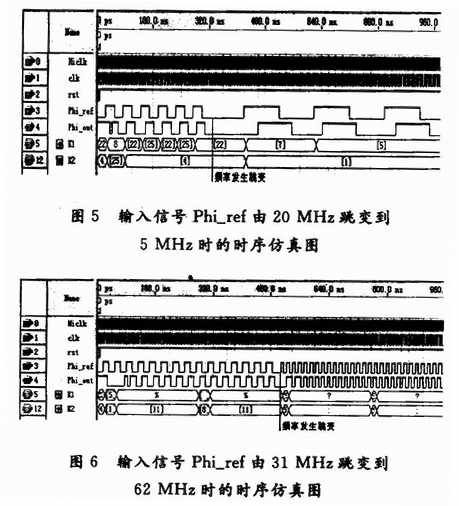

摘要: 在FPGA片內實現全數字

2008-08-14 22:12:51 56

56 所謂鎖相環路,實際是指自動相位控制電路(APC),它是利用兩個電信號的相位誤差,通過環路自身調整作用,實現頻率準確跟蹤的系統,稱該系統為鎖相環路,簡稱

2008-08-15 12:41:05 332

332 一、實驗目的1、掌握模擬鎖相環的組成及工作原理。2、學習用集成鎖相環構成鎖相解調電路。3、學習用集成鎖相環構成鎖相倍頻電路。

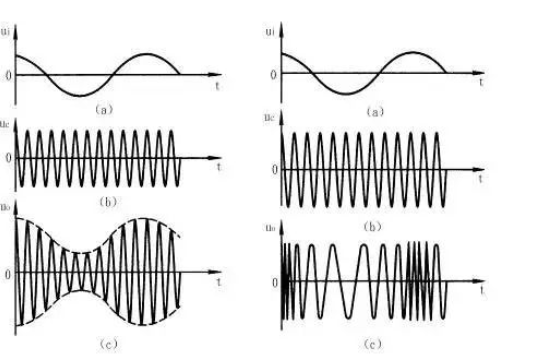

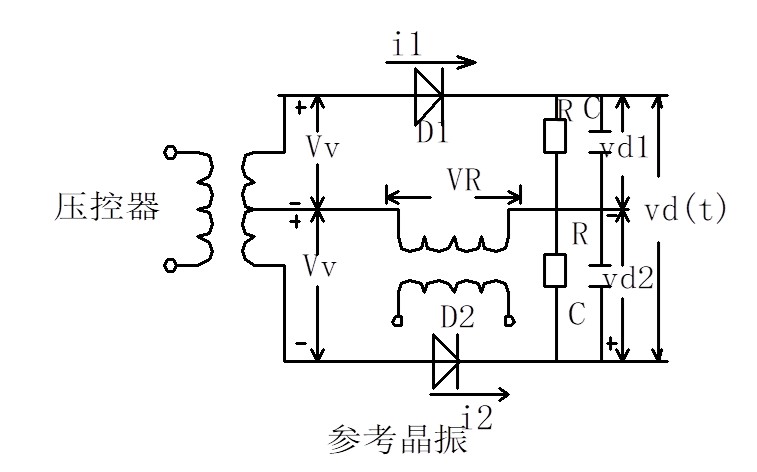

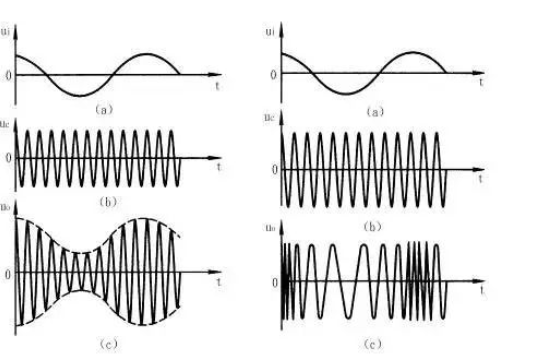

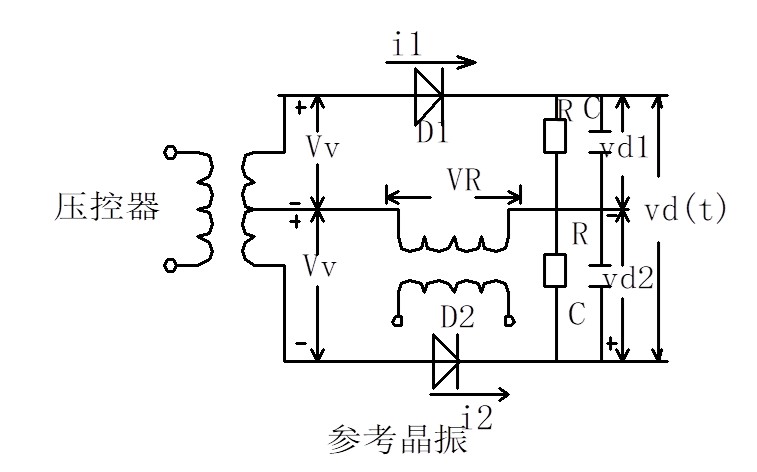

二、鎖相環路的基本原理

2009-03-22 11:44:37 126

126 以TRAC020LH 完全可重配置模擬器件和TRAC 開發軟件為基礎,設計模擬鎖相環;給出仿真結果和利用PIC 單片機對器件進行配置的應用電路。該鎖相環成功應用于逆變器的頻率跟蹤,性能

2009-04-15 11:42:39 11

11 介紹了鎖相環路的工作原理以及MM74HC4046AN鎖相環芯片的引腳功能。給出了利用鎖相環進行頻率變換的方案和用方波信號進行頻率變換的實際電路,并對環路和相位進行了分析。

2009-04-27 15:42:23 50

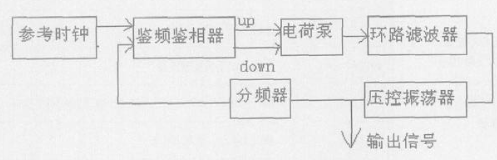

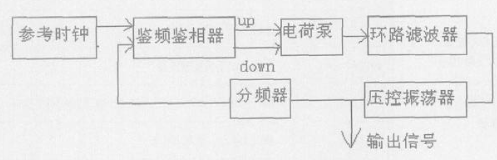

50 本文主要設計了基于相位控制技術的時鐘恢復系統的PLL 鎖相環路。分別對各單元電路結構——鑒頻鑒相器、電荷泵、環路濾波器、壓控振蕩器、分頻器進行設計。采用2.5V,0.25μm

2009-06-01 15:51:53 54

54 智能全數字鎖相環的設計:在FPGA片內實現全數字鎖相環用途極廣。本文在集成數字鎖相環74297的基礎上進行改進,設計了鎖相狀態檢測電路,配合CPU對環路濾波參數進行動態智能配

2009-06-25 23:32:57 72

72 基于FPGA的全數字鎖相環設計:

2009-06-26 17:30:59 141

141 介紹了應用VHDL技術設計嵌入式全數字鎖相環路的方法。詳細敘述了其工作原理和設計思路,并用可編程邏輯器件FPCA予以實現。

2009-07-21 16:46:41 0

0 在載波調制信號的相干解調中,必須提取相干載波,如何從接收信號中提取相干載波,一般方法是采用鎖相環路。它能從淹埋在噪聲中的微弱信號中提取出相干載波,從而大大提高接

2009-08-03 10:09:06 4

4 一種FPGA時鐘網絡中鎖相環的實現方案:摘 要:本文闡述了用于FPGA 的可優化時鐘分配網絡功耗與面積的時鐘布線結構模型。并在時鐘分配網絡中引入數字延遲鎖相環減少時鐘偏差,探

2009-08-08 09:07:22 25

25 本文在介紹了經典全數字鎖相環(all digital PLL, ADPLL)的基礎上,提出了具有捕獲鎖定未知輸入信號頻率功能的ADPLL,使用方便,應用廣泛。本文詳盡的描述了系統的工作原理和關

2009-08-29 10:07:08 43

43 鎖相環頻率合成器(Motorola集成電路應用技術叢書):鎖相環路設計基礎,鑒相器,壓控振蕩器,程序分頻器,前置分頻器,單片集成鎖相環路等內容。

2009-09-05 08:20:52 0

0 鎖相環被廣泛應用于電力系統的測量和控制中。介紹了一種新型的基于比例積分控制邏輯的全數字鎖相環。通過對其數學模型的分析,闡述了該鎖相環的各項性能指標與設計參數的

2010-07-02 16:54:10 30

30 本文在分析商用全數字鎖相環的常用技術和低頻信號的特點后,提出一種適用于低頻信號的基于CPLD的鎖相環實現方法。

2010-08-06 14:39:19 118

118 鎖相環路的原理及特性

鎖相環路的應用

單片集成鑒相器

集成壓控振蕩器

單片集成鎖相環

.................

2010-08-28 15:56:34 99

99 介紹了應用VHDL技術設計嵌入式全數字鎖相環路的方法。詳細描

2010-09-19 10:09:14 68

68 鎖相環原理

鎖相環路是一種反饋電路,鎖相環的英文全稱是Phase-Locked Loop,簡稱PLL。其作用是使得電路上的時鐘和某一外部時鐘的相位同步。因鎖相環可以

2007-08-21 14:46:04 4879

4879 鎖相環路跟蹤特性的測量方法:鎖相環路的跟蹤特性是可以測量的。以CMOS集成鎖相環路5G4046構成的跟蹤濾波器如圖6-2(a)。在電源電壓為10V,中心頻率fo=1

2008-04-21 11:53:40 1225

1225

介紹了鎖相環路的基本原理,分析了集成鎖相環芯片ADF4106的工作特性,給出了集成鎖相環芯片ADF4106的一個應用實例,為高頻頻率合成器的設計提供了很好的思路。???

2009-05-05 19:57:57 2585

2585

摘要: 在FPGA片內實現全數字鎖相環用途極廣。本文在集成數字鎖相環74297的基礎上進行改進,設計了鎖相狀態檢測電路,配合CPU對環路濾波參數進行動態智

2009-06-20 12:39:32 1408

1408

基于柔性鎖相環路的動態電壓恢復器控制方案的研究

摘要:動態電壓恢復器(DVR)是一種新型電能質量調節裝

2009-07-11 13:46:26 416

416

寬頻帶數字鎖相環的設計及基于FPGA的實現數字鎖相環(DPLL)技術在數字通信、無線電電子學等眾多領域得到了極為廣泛的應用。與傳統的模擬電路實現的

2009-11-23 21:00:58 1187

1187

全數字環路濾波器,什么是全數字環路濾波器

環路濾波器的性能優劣會直接影響到跟蹤環路的性能。而采用數字化的環路濾波器便于調試參數和提高

2010-03-23 15:12:15 3685

3685 本文涉及的鎖相環路是基于相位控制的時鐘恢復系統。目的是用鎖相環電路-PLL和DLL實現USB2.0收發器宏單遠UTM的時鐘恢復木塊。其中PLL環路構成的時鐘發生器獎外部晶振的12MHZ的正弦信號

2011-03-03 14:58:34 50

50 鎖相環路由于具有高穩定性、優越的跟蹤性能及良好的抗干擾性,在頻率合成中得到了廣泛應用。但簡單的鎖相環路對輸出頻率、頻率分辨率等指標往往不能滿足要求,所以要對簡單鎖相環

2011-05-28 13:42:13 943

943

針對擴頻通信系統的載波同步,提出一套完善的數字鎖相環設計方案. 該方案利用新穎的可控根法完成1~3階模擬鎖相環(APLL)環路參數設計,并實現從模擬域到數字域的轉換,得到的數字鎖相

2011-08-26 16:10:38 122

122 針對傳統的全數字鎖相環只能鎖定已知信號和鎖頻范圍較小的問題, 提出了一種自動變模控制的寬頻帶全數字鎖相環。對比分析了各類全數字鎖相環鎖頻、鎖相的工作機理, 提出了一種新

2011-09-14 15:22:22 79

79 由于鎖相環路有上述種種優良的特性,再加上集成鎖相環的出現,使鎖相環路在電子技術等各個領域獲得了廣泛的應用,下面對鎖相環在不同領域中的應用情況作一簡單的概述。 1 在通

2012-09-21 10:09:10 3819

3819 基于FPGA的數字鎖相環設計與實現技術論文

2015-10-30 10:38:35 9

9 基于鎖相環的滯后超前環路濾波器的設計與仿真,設計方案。技術指標、電路等。

2016-05-24 10:03:05 11

11 Xilinx FPGA工程例子源碼:用FPGA實現數字鎖相環

2016-06-07 15:07:45 37

37 鎖相環路的基本原理和性能分析,有需要的下來看看

2016-08-09 15:45:55 0

0 一種基于bang_bang鑒頻鑒相器的全數字鎖相環設計_陳原聰

2017-01-07 20:49:27 11

11 PLL(Phase Locked Loop),也稱為鎖相環路(PLL)或鎖相環,它能使受控振蕩器的頻率和相位均與輸入參考信號保持同步,稱為相位鎖定,簡稱鎖相。

2017-05-22 10:11:40 8673

8673

鎖相環路在通信系統中得到了廣泛的應用。本文針對超高頻RFID讀寫器的工作特點,設計了基于數字頻率合成器LMX2315的鎖相環路,給出了鎖相環偽隨機跳頻程序流程圖。

2017-09-07 18:54:00 18

18 一、設計目標 基于鎖相環的理論,以載波恢復環為依托搭建數字鎖相環平臺,并在FPGA中實現鎖相環的基本功能。 在FPGA中實現鎖相環的自動增益控制,鎖定檢測,鎖定時間、失鎖時間的統計計算,多普勒頻偏

2017-10-16 11:36:45 18

18 1.鎖相環的基本組成許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步,利用鎖相環路就可以實

2017-11-20 10:33:16 193377

193377

鎖相環在通信、雷達、測量和自動化控制等領域應用極為廣泛,已經成為各種電子設備中必不可少的基本部件。隨著電子技術向數字化方向發展,需要采用數字方式實現信號的鎖相處理。因此,對全數字鎖相環的研究和應用得

2017-11-24 20:03:04 10723

10723

許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步,利用鎖相環路就可以實現這個目的。鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。

2018-01-22 11:18:45 13409

13409

EngineerIt-鎖相環應用中的環路帶寬

2019-04-15 06:07:00 11933

11933

鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL,Phase-Locked Loop)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號頻率的自動跟蹤,所以鎖相環通常用于閉環跟蹤電路。

2019-09-20 07:05:00 3503

3503

隨著集成電路技術的不斷進步,數字化應用逐漸普及,在數字通信、電力系統自動化等方面越來越多地運用了數字鎖相環。它的好處在于免去了模擬器件的繁瑣,而且成本低、易實現、省資源。本文綜合以上考慮,在一片FPGA中以Quartus II為平臺用VHDL實現了一個全數字鎖相環功能模塊,構成了片內鎖相環。

2020-07-16 09:16:08 2465

2465

,為了減小壓控振蕩器控制電壓的紋波,它采用了二階無源環路濾波器,這樣就構成了三階電荷泵鎖相環。系統級設計與仿真驗證是鎖相環設計的第一步和關鍵的一步。本文對一種用作時鐘倍頻器的三階電荷泵鎖相環進行了系統級設計與仿真驗證,仿真環境采用SIMULINK。

2020-07-24 09:59:51 2564

2564

鎖相環路(Phase Lock Loop,PLL)是一種自動相位控制(APC)系統,是現代電子系統中應用廣泛的一個基本部件。它的基本作用是在環路中產生一個振蕩信號(有時也稱本地振蕩),這個信號的頻率

2020-08-05 14:15:24 5089

5089

鎖相環路是一種反饋控制電路,簡稱鎖相環( PLL)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號頻率的自動跟蹤, 所以鎖相環通常

2020-08-06 17:58:25 24

24 基本鎖相環路是由鑒相器、低通濾波器以及壓控振蕩器構成的相位負反饋系統,具有一個頻率輸入端口,一個電壓輸出端口以及一個頻率輸出端口,通常,模擬模擬鎖相環的鑒相器由模擬乘法器承擔,壓控振蕩器由弛張振蕩器承擔。

2020-12-04 08:00:00 3

3 本文提出了一種適用范圍廣泛的全數字鎖相環(ADPLL)實現方法.在鎖相環輸入頻率未知的情況下,實現鎖相鎖頻功能。本文從全數字鎖相環的基本實現方式入手.進行改進,并使用VH DL語言建模,使用FPGA進行驗證。

2021-01-26 15:03:00 65

65 本文提出了一種適用范圍廣泛的全數字鎖相環(ADPLL)實現方法.在鎖相環輸入頻率未知的情況下,實現鎖相鎖頻功能。本文從全數字鎖相環的基本實現方式入手.進行改進,并使用VH DL語言建模,使用FPGA進行驗證。

2021-01-26 15:03:00 18

18 鎖相環路誕生于20世紀30年代。近年來,鎖相技術在通信、航天、測量、電視、原子能、電機控制等領域,能夠高性能地完成信號的提取、信號的跟蹤與同步,模擬和數字通信的調制與解調、頻率合成、濾波等功能

2021-03-31 11:59:11 4204

4204

為了提高全數字鎖相環的系統運行速度、降低系統功耗,同時提高鎖相系統的動態性能與穩態性能,提出一種基于流

2021-04-01 11:53:12 1740

1740

AD805:數據重定時鎖相環路過時數據表

2021-05-10 16:12:35 8

8 基于FPGA的寬頻帶數字鎖相環的設計與實現簡介說明。

2021-06-01 09:41:14 26

26 基于FPGA的高性能全數字鎖相環

2021-06-08 11:09:01 45

45 鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL,Phase-Locked Loop)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。

2022-03-29 09:54:55 11472

11472 許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步,利用鎖相環路就可以實現這個目的。

2022-05-06 15:27:28 2196

2196 鑒相器是鎖相環路的關鍵部件。在頻率合成器中所采用的鑒相器主要有正弦波相位檢波器與脈沖取樣保持相位比較器兩種。

2022-11-11 16:56:47 3910

3910

許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步,利用鎖相環路就可以實現這個目的。

2023-02-23 10:00:31 1001

1001 許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步,利用鎖相環路就可以實現這個目的。

2023-08-19 09:31:50 1092

1092

信號倍頻。在本文中,我們將詳細探討鎖相環如何實現倍頻。 鎖相環的基本原理 在介紹鎖相環如何實現倍頻之前,我們先來回顧一下鎖相環的基本原理。鎖相環電路主要由三個部分組成:相位檢測器(Phase Detector, PD)、環路濾波器(Loop Filter, LF)和振蕩器(Voltage Cont

2023-09-02 14:59:37 1594

1594 電子發燒友網站提供《基于VHDL的全數字鎖相環的設計.pdf》資料免費下載

2023-11-10 09:47:34 0

0 在現代數字通信中, 數據傳輸中一個很重要的問題就是同步問題。而同步系統中的核心技 術就是鎖相環。鎖相環有模擬鎖相環、模擬?數字混合環、全數字鎖相環等。前二種環路都要采 用壓控振蕩器V CO , 利用

2023-11-09 08:31:40 1

1 簡介:動態電壓恢復器(DVR)是一種新型電能質量調節裝置,它能有效抑制電網電壓波動對敏感負載的影響。介紹了應用于DVR的一種新型的鎖相技術—柔性鎖相環路〔softphase locked loop(SPLL)〕和以此為基礎的控制方案。

2023-11-09 08:31:40 0

0 簡介:鎖相環路的工作原理

§1-2 鎖相環路的工作原理

鎖相環路實質上是一個相差自動調節系統。為了掌握環境的工作原理,理解環 路工作過程中發生的物理現象,必須導出環路的相位

2023-11-09 15:16:24 0

0 鎖相環路(Phase Locked Loop)是一個閉環的相位控制系統,它的輸出信號的相位能自動跟蹤輸入信號相

位。

2023-11-09 15:20:46 0

0 在鎖相環(PLL)中,低通濾波器通常用于濾除鎖相環環路中的高頻噪聲,并平滑鎖相環的控制信號。

2023-12-22 18:15:04 285

285 兩個信號相位同步、頻率自動跟蹤的功能。數字鎖相環不僅具有可靠性好、精度高、環路帶寬和中心頻率編程可調等優點,還解決了模擬鎖相環的直流零點漂移、器件飽和及易受電源和環境溫度變化等缺點,此外還具有對離散

2024-01-02 17:20:25 701

701

鎖相環路與自動頻率控制電路有何區別?為什么說鎖相環相當于一個窄帶跟蹤濾波器 鎖相環路(PLL)和自動頻率控制電路(AFC)是常見的頻率調節電路,它們的主要區別在于功能和應用場景。 首先,我們來探討

2024-01-31 15:24:57 180

180 基本鎖相環通常由鎖相檢測器(Phase Detector)、低通濾波器(Loop Filter)和令牌圈振蕩器(VCO)組成。它是最簡單的鎖相環形式,用于頻率和相位同步。

2024-01-31 16:00:55 218

218

電子發燒友App

電子發燒友App

評論