嵌入式系統往往執行比較單一的任務,針對某種特定應用而專門設計,但目前在嵌入式系統中采用的微處理器絕大部分都是通用嵌入式微處理器,其通用的指令集面對千差萬別的嵌入式應用時暴露出專用性差,執行效率低的弱點。另一個問題是,目前應用的嵌入式微處理器都是硬核,功能模塊和指令集都是固定的,當應用發生較大變化時,很難通過對微處理器功能模塊和指令集進行擴展來適應變化,往往只能換用一款新的微處理器,甚至重新設計整個嵌入式系統的硬件和軟件,浪費了大量的時間和金錢。因此,如何提高指令集的針對性,提高指令的執行效率以及如何增強嵌入式微處理器的擴展能力成了困擾嵌入式系統開發人員的兩個難題。

1.ASIP和FPGA

ASIP的提出是微處理器設計理念的一項重大創新。ASIP(Application-Specific Instruction set Processor)即專用指令集處理器,它相對傳統微處理器最大的特點就是其指令集針對特定應用專門設計,一條指令就可以完成該種應用常做的一系列運算,例如一些常用算法,這樣就極大的提高了指令的執行效率,往往若干條普通指令幾十個時鐘周期完成的操作用一條專用指令幾個時鐘周期就完成了。

采用ASIP理念設計微處理器可以在很大程度上解決上一節提到的指令集專用性差,指令執行效率低的問題,但這是要付出代價的,因為這些專用指令一般需要專門硬件電路支持才能實現。

ASIP用傳統的集成電路技術實現是不現實的,集成電路設計復雜,開發周期長,定型后無法進行擴充,這樣每遇到一種新應用,就得重新設計一款專用芯片,成本是不可接受的,這在一個時期內限制了ASIP的發展,直到FPGA(Field Programmable Gate Array,現場可編程門陣列)的出現,才為ASIP的實現提供了可能。

FPGA內部包含可配置邏輯模塊CLB(Configurable Logic Block),可以方便的用硬件描述語言進行開發。硬件描述語言描述要實現的電路的功能,經過編譯、綜合形成配置FPGA芯片的字節碼文件,經下載后就可以在CLB內部形成一塊模擬的專用電路,功能與實際電路完全一樣,這樣就可以實現對ASIP中專用指令的支持。用FPGA實現ASIP,相對傳統的集成電路來說,最大的優點是擴展性好,遇到新應用時,完全可以對一個較小的軟核原型進行擴充,通過添加新模塊,實現對針對該應用設計的專用指令的支持,迅速完成新的設計。此外,FPGA還有設計方便,開發周期短,可重復編程等優點。

基于以上討論,可以看出ASIP+FPGA設計模式可以從很大程度上解決引言中提到的兩個難題。為了進行更深入的研究,我們對該設計模式進行了嘗試,用VHDL硬件描述語言在FPGA上實現了一個8位微處理器軟核(以下稱為WolfMCU),并為該微處理器實現了6條專用指令,每一條專用指令都由FPGA芯片中的專用電路支持。

2.WolfMCU體系結構設計

微處理器常用的體系結構有兩種――馮氏結構和哈佛結構。在馮氏結構中,指令和數據使用同一個存儲器,經由同一個總線傳輸,而在哈佛結構中,使用兩個獨立的存儲器,分別存儲指令和數據,并且使用兩條獨立的總線,分別作為CPU與每個存儲器之間的專用通信路徑,這樣就保證了系統具有較高的可靠性,嵌入式系統追求的就是高可靠性,因此哈佛結構的嵌入式微處理器在嵌入式系統中被廣泛應用,本文介紹的WolfMCU也采用了哈佛結構。

2.1 WolfMCU的體系結構

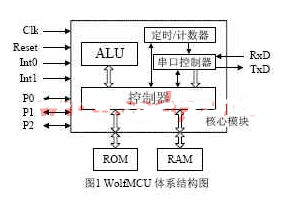

WolfMCU由6個模塊組成,包括控制器、運算器、定時器/計數器、存儲器、串口通信控制器和并行通訊接口,如圖1所示。

控制器是WolfMCU的大腦,在它的控制下,各模塊協調有序的工作。控制器包括四個模塊――譯碼模塊、有限狀態機模塊、存儲器控制模塊和中斷處理模塊。譯碼模塊對指令進行譯碼,產生相應的控制信號。有限狀態機模塊控制WolfMCU在不同工作狀態之間進行轉換。WolfMCU共有四種工作狀態:STARTUP、FETCH、EXEC1和EXEC2。STARTUP是WolfMCU加電后的初始狀態,WolfMCU復位后也回到這個狀態;FETCH是取指令狀態,EXEC1和EXEC2是指令執行狀態,處理器根據譯碼結果在這兩個狀態下取操作數進行計算。存儲器控制模塊在譯碼模塊產生的控制信號的作用下取指令和操作數,并送往正確的地方。中斷處理模塊接收外部中斷并進行處理,WolfMCU共有兩個中斷源:Int0和Int0。

運算器在控制器的控制下完成指定的運算。WolfMCU的運算器支持8位數據的加、減、乘、與、或、非等基本運算,還支持十進制調整、乘加、乘減、平方后加、平方后減、取絕對值等特殊運算,這些特殊運算由專用指令實現,由專用電路支持。

系統內不同部件的工作時鐘可能與系統時鐘不一致,比如串口控制器,它的工作時鐘根據不同波特率而不同,這就要求系統提供相應的時鐘,以保證其正常工作,定時器/計數器可以實現對系統時鐘進行分頻以遍提供給相應的部件使用。

存儲器包括100字節的ROM、和100字節RAM(ROM和RAM都可以擴充容量)。ROM里存放要執行的程序,RAM中存放運算過程中產生的數據。ROM中的程序可由上位PC機通過串口寫入。

2.2 實驗驗證

2.1節介紹了WolfMCU的體系結構,接下來以一個小程序為例分析WolfMCU工作的具體過程。

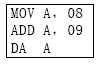

該程序實現加法的操作,圖2所示是該程序的三條指令及其在軟核ROM中的存儲狀態,第一條指令NOP是空操作指令,第二條指令把立即數56H送到累加器Acc中去,第三條指令給累加器Acc加上立即數5FH,結果保存在累加器Acc中,最后Acc中的結果是56H+5FH=B5H。

第一條空操作指令比較簡單,系統不進行任何操作,只是狀態由初始狀態(STARTUP),變為取指令狀態(FETCH),PC指針加1,指向下一條指令MOV。

在第二個指令周期里,系統處于FETCH狀態,存儲器控制模塊從ROM的001地址處讀出8位數據(01110100),把它送往譯碼模塊譯碼,譯碼模塊根據指令碼(01110100)識別出這是MOV_Acc_imm指令(把立即數送往累加器Acc),知道該指令需要有一個操作數,所以把PC指針加1,并把系統下一個狀態置為EXEC1,為下一個周期取該指令的操作數做好準備。

第三個指令周期開始,存儲器控制模塊取出操作數56H(01010110),同時譯碼模塊發出控制信號,指出這是從ROM輸入的數據(因為系統處在EXEC1狀態),目標寄存器是累加器Acc,然后PC指針加1,置系統下一個狀態為FETCH,為取下一條指令做好準備。在這個時鐘周期內,存儲器控制模塊已經把56H送到累加器Acc中了。

ADD指令的執行過程和MOV指令類似,這里就不做詳述,唯一不同的是ADD指令執行過程中經過了兩次譯碼,第一次和MOV相同,第二次是在控制器把加法控制信號發送到ALU之后,ALU還要識別出這條加法指令是要把立即數和累加器中的操作數相加,這樣才能最終完成操作。

至此,這段程序執行完畢,正確輸出結果B5H。下載到Memec V2mb1000 FPGA開發板上的運行,通過七段數碼管顯示的結果,如圖3所示:

3.WolfMCU指令集設計

對于桌面計算機系統來說,因為要面對不同的應用,指令集功能越強大越好,通用性越強越好。但對于嵌入式系統來說,由于只面對某種特定的應用,所以在滿足應用需求的前提之下指令集越小越好,指令越專用,效率越高越好。

綜合考慮了指令集尺寸和專用性,WolfMCU的指令集共有22條指令,包括16條通用指令和6條專用指令。16條通用指令都是最常用的指令,以后再設計其他專用指令集微處理器時可以在此基礎上進行擴充,通用指令包括數據傳送指令,算術運算指令,邏輯運算指令,控制轉移指令等四類,在這不再詳述。6條專用指令,如表1所列,增強了WolfMCU的運算能力。

除了指令的功能之外,指令的尋址方式也是指令集設計的一個重要方面, WolfMCU共支持4種尋址方式:立即尋址、寄存器尋址、直接尋址、寄存器間接尋址。

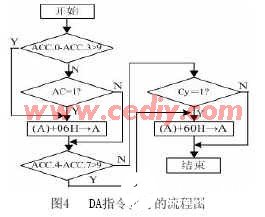

ASIP的設計,重點和難點是專用指令的實現,下面以DA指令(十進制調整)為例介紹一下專用指令的實現。這條指令跟在加法指令后,對累加器Acc中8位結果進行調整,使它調整為壓縮得BCD碼的數,以完成十進制加法運算功能。DA指令執行的流程圖如圖4所示,具體代碼不再詳細介紹,這段代碼編譯后形成一個模塊連接在WolfMCU的控制器上,下載到FPGA芯片之后,相當于有一塊專用電路支持DA指令,控制器只要把ACC中的內容發送到這個模塊,就可以返回調整后的結果,大大提高了該指令的執行效率。用下面的程序測試DA指令的執行效果:

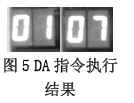

程序執行十進制的8和9相加,在WolfMCU軟核上執行后,輸出0107(圖5所示為通過七段數碼管顯示結果),說明DA指令執行正確。

其他專用指令的實現方式和DA指令類似,也是作為一個模塊連接在WolfMCU軟核之上,調用這些指令時,只需把操作數傳送給這些模塊。

4.專用指令實現與普通指令實現的性能對比

上表中列出的乘加、乘減等指令也像十進制調整指令一樣,因為有專門的電路支持這些指令,因此可以在幾個時鐘周期內迅速輸出結果。

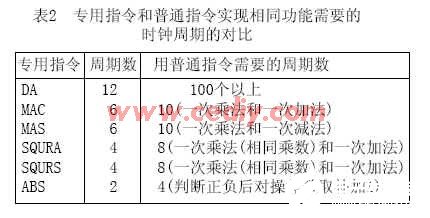

上面提到的十進制調整指令,首先需要判斷累加器的低四位是否大于9,輔助進位標志位是否為1,二者滿足其一就給低四位加上06H,然后判斷高四位,若高四位或進位標志為1,則給高四位加上60H,如果使用普通指令編程實現,至少需要上百個時鐘周期,而采用專用指令之后,只需要12個時鐘周期,表2列出了采用專用指令和普通指令時需要的時鐘周期的對比。

由表2可以看出,采用專用指令后,所需時鐘周期數至少降低了40%,為實現這些專用指令付出的硬件代價還是值得的。

5.總結

本文介紹了一種提高嵌入式微處理器指令執行效率和擴展性的設計思路--ASIP+FPGA,并對這種思路進行了嘗試,實現了一個8位的微處理器軟核,為這個軟核設計了16條通用指令和6條專用指令,通過與普通指令的實現開銷進行對比,驗證了ASIP+FPGA設計模式的優勢,這個簡單的8位微處理器軟核可以作為設計復雜ASIP的原型,可以很容易的擴展成16位、32位,也可以很方便的添加新的專用指令,滿足新應用的需要。

本文作者創新點:1.提出了一種嵌入式微處理器設計模式--ASIP+FPGA模式,從體系結構和專指令集設計兩方面對該設計模式進行了分析。2.采用該設計模式,在Xilinx V2MB1000

FPGA開發板上設計并實現了一款嵌入式微處理器軟核(WolfMCU),驗證了該設設計模式的優勢。3.WolfMCU采用模塊化設計,可以方便的擴展到16位或添加新的功能模塊。

責任編輯:gt

電子發燒友App

電子發燒友App

評論