1、 引言

在雷達、氣象、地震預報、航空航天、通信等領域里,現場信號具有重要的作用,這些信號的主要特點是實時性強,數據速率高,數據量大,處理復雜,運算量大。因此,高速數據采集的研究一直是工程實踐中一項倍受人關注的領域。目前由于數字信號的快速發展,對信號采集的要求也不斷的提高,特別是在參數方面的要求越來越高,如精度、速度、采樣通道數等。鑒于此,本文會介紹一種基于FPGA來控制高速A/D轉換器AD9432實現高速采集,從而滿足在系統中的應用。

2、 系統結構

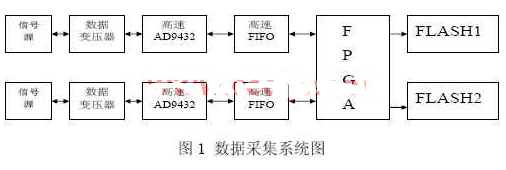

系統對輸入的兩路模擬信號采樣率為60MHz,每路1K的采樣周期(前100微秒進行采樣,后900微秒進行數據轉換,放入FLASH中),量化精度為12bit。轉換后的數據經過FPGA的控制送到乒乓FLASH中。再以140Mbps的數據率平穩輸出,利用FPGA對數據進行幀結構處理,最后經數據采集卡送入電腦中通過軟件進行顯示。數據采集系統的結構如圖1所示。

3 、硬件設計

常用的高速多通道數據采集的設計方案有兩種:

(1)以單片機MCU為控制核心,控制多通道數據采集與處理。因為單片機本身指令周期及處理速度的影響,同時隨著程序量的增加,如果程序的健壯性不理想的話,可能會出現“程序跑飛”和“復位”現象。因此對于高速多通道數據采集,普通單片機很難滿足系統對數據采集實時性和同步性的要求。

(2)以FPGA作為數據采集的控制核心,實現多通道模擬信號的采集和處理。由于FPGA采集采樣控制、處理、緩存、傳輸控制、通訊于一個芯片內,編程配置靈活,開發周期短,系統簡單,具有高集成度、體積小、低功耗、高速、I/O端口多、在線系統編程等優點,尤其在只需要簡單數據處理的情況下,FPGA能夠提供比專用高速DSP更好的解決方案,并且特別適用于對時序有嚴格要求的高速多通道數據采集系統。

針對雷達實時監測系統對實時性和同步性的要求,選擇第二種方案設計高速多通道數據采集系統。

本設計中采取了高速模數轉換器AD9432+高速FIFO+大規模可編程邏輯器件FPGA+FLASH存儲芯片的方案。根據之前相關系統的經驗,此方案的可實現性高,系統可靠性大。關鍵器件的選擇目的如下:

1.高速AD轉換器的選擇

信號采集的核心是模數轉換技術。模數轉換包括采樣、保持、量化和編程四個過程采樣就是將一個連續變化的信號X(t)轉換成時間上離散的采樣信號X(n)。

由于本系統時鐘頻率為60MHz,分辨率要求又較高,所以積分型、順次逼近型、閃爍型無法使用本次設計,在本次設計中采用了ADI公司生產的AD9432模數轉換器。它是單片、12位精度、采用帶有誤差校正邏輯的多級差分流水結構的、105Msps高速模數轉換器,片內集成高性能的采樣保持放大器和參考電壓源。同時,AD9432還具有較低的功耗(850mw)和較高的信噪比(66dB)。

2.固態存儲介質的選擇

可作為固態記錄器件的半導體件有多種,其中主要包括SRAM,DRAM,FRAM,FLASH等幾種器件;其中SRAM和DRAM為易失型(斷電后數據不能保持),FRAM和FLASH為非易失型(斷電后數據能保持)。由于DRAM和FLASH兩種器件的特速工藝結構,能實現較高的位密度,因而得到廣泛應用。

SRAM和DRAM均為易失型器件,需要一個后備電池提供連續的電源,同時,它們的電源功耗相當大。在EEPROM的基礎上發展起來的閃爍(Flash)PROM,解決了上訴問題。FLASH為非易失型器件,當斷電后,數據仍保持在FLASH存儲芯片中,因而不需要后備電源,同時它的功耗非常低。由于半導體技術的迅速發展,FLASH存儲芯片的密度不斷提高,容量越來越大,所以本設計采用了SAMSUNG公司生產的K9F1G08U0M型FLASH。

3、可編程邏輯器件的選擇

本系統采用了Xilinx公司生產的XC2S100E型FPGA。

XC2S50E是Spartan-IIE系列產品中的一款,它采用了1.8V的內核電壓,系統性能可達到200MHz,具有50000個系統門,CLB數量為16×24,LC數量1728,BlockRAM容量32Kbit,擁有182個I/O。由于這款FPGA采用了低內核電壓,這將從根本上減小芯片功耗,從而解決高速工作狀態下發熱量大的問題。同時其豐富的門陣列資料,也為復雜控制邏輯的實現提供了可能。

3.1 ADC轉換以及控制

根據上述采樣要求,ADC轉換芯片選用ADC公司的AD9432,在使用AD9432時,本設計采取了以下方法:

1.高速采集工作中,為滿足抗干擾性強,傳輸數率快,電平穩定,采用外接ECL差分芯片來提供差分時鐘;

2.為滿足對直流精度和溫度漂移的要求,采用外接基準電壓源的形式;

3.為滿足對信號輸入抗電磁干擾及信號放大采樣輸入端前加變壓器;

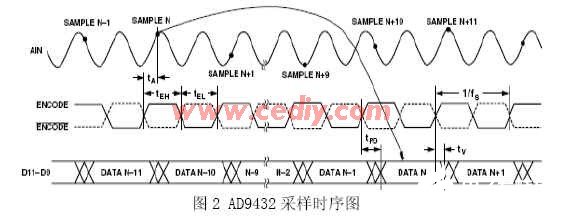

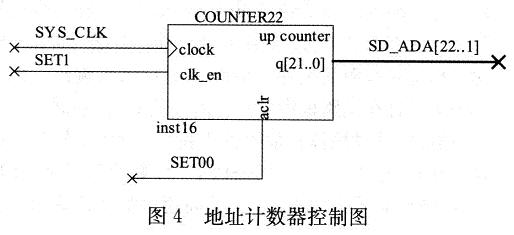

4.從圖2中可以看出,由于AD9432采用多級差分流水結構,其在每個時鐘周期的上升沿捕獲一個采樣值,10個周期以后才可以輸出轉換結果,可以看出輸出管道延遲10個采樣周期,因此采樣時鐘脈沖的個數必須比采樣點數至少多10個才能保證采樣的正確。

由于通道數有2路,因此直接取其數字量的高12bit先分別送入高速FIFO中,再送入FPGA中,利用FPGA內部的資源生成鎖存器進行兩路數據的合并,這樣提高了集成度,可以減少外圍的器件數量。設定兩路鎖存器的時鐘相差1800,這樣可以實時地把輸入的數據轉換為順次輸入的數據。

3.2 ADC控制時序說明

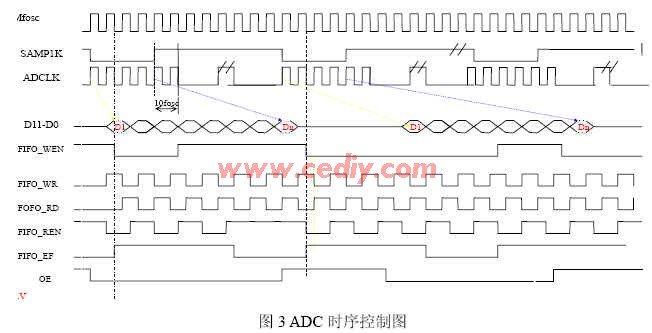

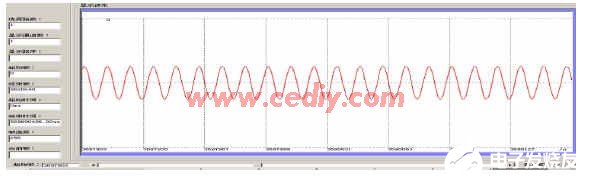

采集信號啟動,開始采集數據,在60MHz頻率下工作,如圖3。

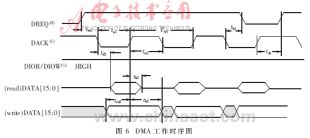

因為兩路是對稱的,所以兩路控制AD是同時進行,時序一致。由于ADC的輸出延時,啟動ADC采集后,延遲10個fosc,送出FIFO的寫時鐘WCLK和寫使能信號/WEN,把AD采集的數據送到FIFO中。在每個fosc的上升沿檢查FIFO的/EF引腳,若/EF=‘1’,說明FIFO不空,就啟動對FIFO的讀操作,否則,對FIFO的讀操作無效。由FPGA送出FIFO的讀時鐘信號RCLK和讀使能信號/REN,把FIFO中的12位數據讀出,進入FPGA片內進行乒乓FLASH數據處理。

3.3 乒乓FLASH的結構及讀寫控制

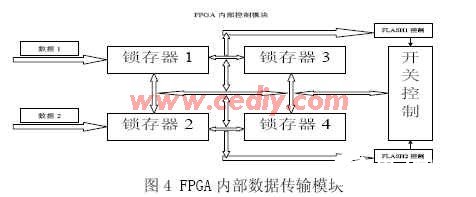

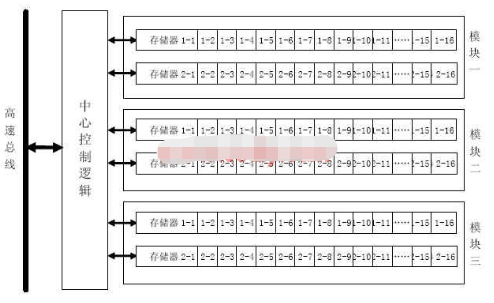

由于需要同時輸入和不間斷輸出數據,且數據量較大,因此選用乒乓FLASH來保證采樣和傳輸同時進行。乒乓傳輸部分包括兩個開關控制(FPGA中實現)以及兩塊高速FLASH,如圖4。

部數據傳輸模塊

將在FPGA中已經合并的數據再分為兩路,流向由鎖存器控制,當門控信號控制FLASH1時,FLASH1則進行數據寫入,鎖存器1打開,鎖存器2成高阻狀態;與此同時,FLASH2進行數據讀出,鎖存器3成高阻狀態,鎖存器4打開。當滿足切換的條件后,切換到FLASH2寫入而FLASH1讀出的模式,如此循環。

為了使各個通道的數據排列在同一個數據區、讀出時更加容易操作,我們將同一個通道的數據放在一片FLASH,即在1/60MHz的時間內,寫入FLASH的地址不變,其中兩片FLSAH的片選信號CS交替有效,而讀出FLASH中只有一片FLASH的CS有效。這樣,更具FLASH的容量大小及讀取速度,在一個0.4s的時間段中,正好讀出一片FLASH的數據就是一個通道數據,而下一個0.4s的時間段中,正好讀出的一片FLASH的數據就是一個通道的數據,而下一個中讀出的就是另一個通道的數據。

4 、抗干擾硬件設計

由于本系統的數據傳輸率比原有的設備提高了幾倍,達到120Mbps,此時電路板將面臨噪聲和干擾問題。本系統采用了一下抗干擾措施。

1.高速數據采集系統把系統的電源分成模擬和數字兩部分,把系統的地分成模擬地和數字地,正確使用兩者之間的單點接地或多點接地,盡量用真個平面作為地平面。

2.在電源接入PCB板和板上每對電源和地之間加上濾波和去耦電路,能夠更好地消除有電源引起的噪聲。系統將數字電源和模擬電源分開供電,以免快速變換的數字信號干擾模擬信號。

3.去耦電容有兩個作用:一方面是本集成電路的蓄能電容,提供和吸收該集成電路開門關門瞬間的充放電能;另一方面旁路掉該器件的高頻噪聲;

4.時鐘產生器盡量靠近到用該時鐘的器件,時鐘線要盡量短;

5.布線的方式盡量采用菊鏈法的方式,這種結構便于阻抗匹配;

6.印制板盡量使用45度折線而不用90度折線布線,以減小高頻信號對外的發射與耦合;

7.任何信號都不要形成環路,如不可避免,必須讓環路區盡量小;

8.用大容量的鉭電容而不是電解電容作電路充放電能儲電容,而使用電解電容須在每個電容邊上加一個小的高頻旁路電容。

5、 實驗驗證

通過上述方案,進行了硬件實現,圖5顯示了該設計的高速采集系統對50Hz的正弦波形采集,并對采集后的波形實現了波形再現,該圖所顯示的波形符合采集前設定的波形,充分說明了該系統的可行性。

6、 結束語

高速數據采集系統的關鍵技術體現在合理的設計結構和對干擾的有效抑制,本文對這兩方面進行了充分的考慮,接下來利用FPGA組織方式靈活的特點,根據實際情況設計合理的結構滿足同步實時高速數據采集系統的要求,因此,本文所介紹的是一種不失一般性的數據采集解決方案。

本文作者創新點:1.以AD9432為核心的高速數據采集系統,最高采樣率能達到60MB/S;

2.利用FPGA編程設計乒乓FLASH結構;

責任編輯:gt

電子發燒友App

電子發燒友App

評論