1 前言

閃存(又稱FLASH,閃速存儲器)是一種新興的半導(dǎo)體存儲器,是一種不揮發(fā)性存儲器NVM(Non-Volatile Memory)。它采用類似于EPROM的單管疊柵結(jié)構(gòu)的存儲單元,是新一代用電信號擦除的可編程ROM;既吸收了EPROM結(jié)構(gòu)簡單、編程可靠的優(yōu)點(diǎn),又具有EEPROM用隧道效應(yīng)擦除的快捷特性,集成度可做得很高,因而在便攜式數(shù)據(jù)存儲和各種圖像采集記錄系統(tǒng)中得到了廣泛的應(yīng)用。其主要特點(diǎn)有:非易失性,可靠性高;功耗小;壽命長,可以在在線工作的情況下進(jìn)行寫入、讀出和擦除操作,標(biāo)準(zhǔn)擦寫次數(shù)可達(dá)10萬次;密度大、成本低,具有很高的容量密度,價(jià)格也在不斷降低;具有抗震動、抗沖擊、溫度適應(yīng)范圍寬等。正是由于閃存具有上述諸多優(yōu)點(diǎn),近年得到了快速而迅猛的發(fā)展。

全球閃速存儲器的主要供應(yīng)商有AMD、Atmel、Fujistu、Hitachi、Hyundai、Intel、Micron、Mitsubishi、Samsung、SST、Sharp、Toshiba。由于各自技術(shù)架構(gòu)的不同,分為幾大陣營,因此閃速存儲也按其采用技術(shù)的不同而分為幾大類:

*NOR技術(shù)——代表公司Intel,特點(diǎn)為擦除和寫入慢、隨機(jī)讀快;

*NAND技術(shù)——代表公司Samsung、Toshiba,特點(diǎn)為隨機(jī)讀寫慢、以頁為單位連續(xù)讀寫快;

*AND技術(shù)——代表公司Hitachi,特點(diǎn)為低功耗,價(jià)格高。

*由EEPROM派生的閃速存儲器。特點(diǎn):介于NOR與EEPROM之間。

存儲器的發(fā)展具有容量更大、體積更小、功耗更低、價(jià)格更低的趨勢,這在閃速存儲器行業(yè)表現(xiàn)得淋漓盡致。隨著半導(dǎo)體制造工藝的發(fā)展,主流閃速存儲器廠家采用90nm,甚至73nm的制造工藝。

借助于先進(jìn)工藝的優(yōu)勢,閃速存儲器的容量可以更大:NOR技術(shù)已經(jīng)出現(xiàn)512Mb的器件,NAND和AND技術(shù)已經(jīng)有32Gb的器件。

芯片的封裝尺寸更小:從最初DIP封裝,到PSOP、SSOP、TSOP封裝,再到BGA封裝,閃速存儲器已經(jīng)變得非常纖細(xì)小巧。

工作電壓更低:從最初12V的編程電壓,一步步下降到5V、3.3V、2.7V、1.8V單電壓供電;符合國際上低功耗的潮流,更促進(jìn)了便攜式產(chǎn)品的發(fā)展。

位成本大幅度下降:采用NOR技術(shù)的Intel公司的28F128J3價(jià)格為25美元,NAND技術(shù)和AND技術(shù)的閃速存儲器已經(jīng)突破10MB/2美元的價(jià)位,性價(jià)比極高。

本文中討論的是采用NAND技術(shù)的TH58NVG1S3A。

2 TH58NVG1S3A芯片

TH58NVG1S3A是Toshiba公司生產(chǎn)的一款閃存芯片。它的單片容量是2Gbits,采用的是NAND技術(shù),它可以在200μs內(nèi)完成一頁2112個(gè)字節(jié)的編程操作,還可以在2ms內(nèi)完成128K字節(jié)的擦除操作,同時(shí)數(shù)據(jù)區(qū)內(nèi)的數(shù)據(jù)能以20MBps的速度讀出。

TH58NVG1S3A大容量閃存芯片的I/O口既可以作為地址的輸入端,也可以作為數(shù)據(jù)的輸入/輸出端,同時(shí)還可以作為指令的輸入端。芯片上的寫控制器能自動控制所有編程和擦除操作,包括提供必要的重復(fù)脈沖、內(nèi)部確認(rèn)和數(shù)據(jù)空間等。

2.1 TH58NVG1S3A芯片的性能參數(shù)

TH58NVG1S3A的主要特點(diǎn)如下:

?采用3.3V電源;

?芯片內(nèi)部的存儲單元陣列為(256+8192K)×8bits,數(shù)據(jù)寄存器和緩沖存儲器均為(2K+64)×8bits;

?具有指令/地址/數(shù)據(jù)復(fù)用的I/O口;

?由于采用可靠的CMOS移動門技術(shù),使得芯片最大可實(shí)現(xiàn)100000次編程/擦除操作,該技術(shù)可以保證數(shù)據(jù)保存10年而不丟失。

2.2 TH58NVG1S3A芯片的主要引腳說明

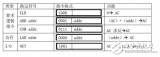

TH58NVG1S3A有48個(gè)引腳,具體功能如下:

I/O0~I/O7:數(shù)據(jù)輸入輸出口,I/O口常用于指令和地址的輸入以及數(shù)據(jù)的輸入/輸出,其中數(shù)據(jù)在讀的過程中輸入。當(dāng)芯片沒有被選中或不能輸出時(shí),I/O口處于高阻態(tài)。

CLE:指令鎖存端,用于激活指令到指令寄存器的路徑,并在WE上升沿且CLE為高電平時(shí)將指令鎖存。

ALE:地址鎖存端用于激活地址到內(nèi)部地址寄存器的路徑,并在WE上升沿且ALE為高電平時(shí),地址鎖存。

CE:片選端用于控制設(shè)備的選擇。當(dāng)設(shè)備忙時(shí)CE為高電平而被忽略,此時(shí)設(shè)備不能回到備用狀態(tài)。

RE:讀使能端,用于控制數(shù)據(jù)的連續(xù)輸出,并將數(shù)據(jù)送到I/O總線。只有在RE的下降沿時(shí),輸出數(shù)據(jù)才有效,同時(shí)它還可以對內(nèi)部數(shù)據(jù)地址進(jìn)行累加。

WE:寫使能控制端,用于控制I/O口的指令寫入,同時(shí),通過該端口可以在WE脈沖的上升沿將指令、地址和數(shù)據(jù)進(jìn)行鎖存。

WP:寫保護(hù)端,通過WP端可在電源變換中進(jìn)行寫保護(hù)。當(dāng)WP為低電平時(shí),其內(nèi)部高電平發(fā)生器將復(fù)位。

RY/BY_N:就緒/忙輸出,RY/BY_N的輸出能夠顯示設(shè)備的操作狀態(tài)。RY/BY_N處于低電平時(shí),表示有編程、擦除或隨機(jī)讀操作正在進(jìn)行。操作完成后,RY/BY_N會自動返回高電平。由于該端是漏極開路輸出,所以即使當(dāng)芯片沒有被選中或輸出被禁止時(shí),它也不會處于高阻態(tài)。

3 利用CPLD對TH58NVG1S3A控制的實(shí)現(xiàn)

本項(xiàng)目采用的CPLD是LATTICE公司的高密度在系統(tǒng)可編程邏輯器件ISPLSI1032E,這款CPLD有84腳和100腳兩種封裝形式,有64個(gè)I/O口供用戶使用,內(nèi)部集成6000門,有192個(gè)寄存器。能夠滿足設(shè)計(jì)需要。

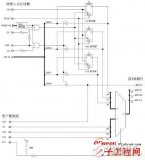

3.1 硬件連接

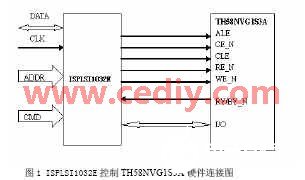

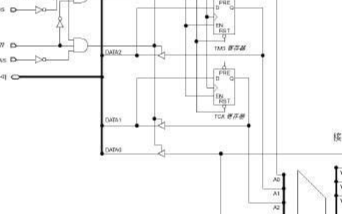

圖1所示為ISPLSI1032E控制TH58NVG1S3A芯片的主要信號連接情況。圖中ADDR、DATA、CMD是系統(tǒng)與外部的接口信號,提供給用戶使用;CLK是輸入到CPLD的時(shí)鐘信號(頻率為20Mhz);另外ISPLSI1032E提供6根控制線和8根數(shù)據(jù)線以實(shí)現(xiàn)對TH58NVG1S3A的邏輯控制和數(shù)據(jù)交換,這些對用戶是不透明的。ADDR是提供給閃存的29位的地址輸入線,可實(shí)現(xiàn)對閃存的512M×8bits單元尋址;CMD為3位輸入線表示對閃存的操作狀態(tài)(讀、寫、擦除等);DATA 為雙向8位數(shù)據(jù)線;RY/BY_N是TH58NVG1S3A的反饋信號,示意操作過程是否結(jié)束;其他信號是TH58NVG1S3A的控制信號。

3.2 軟件設(shè)計(jì)

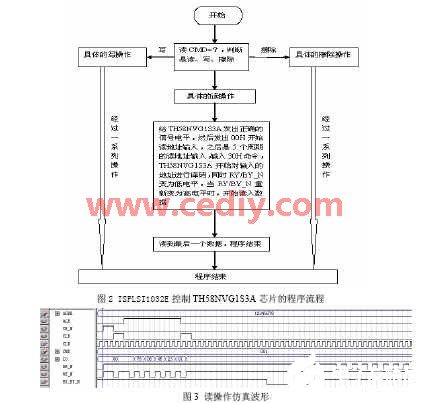

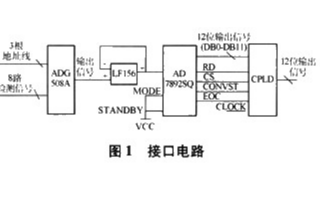

本文使用VHDL語言對CPLD進(jìn)行編程。VHDL語言具有很強(qiáng)的電路描述和建模能力,能從多個(gè)層次對數(shù)字系統(tǒng)進(jìn)行建模和描述,使用VHDL語言對CPLD進(jìn)行編程,可以將硬件工作軟件化,從而大大簡化了硬件設(shè)計(jì)任務(wù),提高了設(shè)計(jì)效率和可靠性,在語言方面具有很好的易讀性;同時(shí)VHDL語言描述的系統(tǒng)是以并行方式工作的,大大提高了系統(tǒng)的運(yùn)算速度;用VHDL語言進(jìn)行電子系統(tǒng)設(shè)計(jì)的最大優(yōu)點(diǎn)是使我們專致于功能的實(shí)現(xiàn),而不需要對不影響功能的因素花費(fèi)過多時(shí)間和精力,縮短了產(chǎn)品的開發(fā)時(shí)間。VHDL是一種標(biāo)準(zhǔn)語言,不是針對某廠家的器件,而是針對所有可編程邏輯器件,因而具有普遍性,成為最常用的硬件描述語言。程序流程如圖2 所示。其中用CMD=001表示讀閃存,CMD=010表示對閃存進(jìn)行寫操作,CMD=100表示對閃存進(jìn)行塊擦除。

TH58NVG1S3A的讀是按頁執(zhí)行的。讀操作首先把00H命令寫到指令寄存器作為讀地址輸入指令,一旦該指令被鎖存,就不能在下頁中寫入讀操作了,然后輸入5個(gè)周期的地址數(shù)據(jù)到地址寄存器中進(jìn)行地址譯碼,最后把30H寫到指令寄存器作為讀開始指令,但是并不是馬上就能從閃存讀出數(shù)據(jù),直到將選定頁中的2112字節(jié)數(shù)據(jù)存入數(shù)據(jù)寄存器后才能從閃存輸出數(shù)據(jù),系統(tǒng)可以通過分析RY/BY_N腳的輸出來判斷數(shù)據(jù)轉(zhuǎn)移是否完成。選定頁中的2112字節(jié)數(shù)據(jù)能夠在25μs內(nèi)被存入數(shù)據(jù)寄存器中,而存入數(shù)據(jù)寄存器的數(shù)據(jù)可以很快地被讀出,數(shù)據(jù)通過周期為50ns 的RE脈沖被連續(xù)輸出至I/O。

TH58NVG1S3A的寫操作也是按頁進(jìn)行的。首先輸入連續(xù)數(shù)據(jù)輸入指令80H,再輸入5個(gè)周期的地址數(shù)據(jù)到地址寄存器中進(jìn)行地址譯碼,之后在50ns的WE周期上升沿將要寫入的2112字節(jié)數(shù)據(jù)寫入數(shù)據(jù)寄存器中,最后輸入自動編程指令10H開始編程。可以通過查詢RY/BY_N腳的輸出來判斷編程是否完成。編程完成后通過輸入讀狀態(tài)寄存器70H來確定編程操作是否成功。雖然閃存的寫操作是以頁為單位的,但是TH58NVG1S3A可以將一頁空間(2112字節(jié))分成8個(gè)部分(0-511,512-1023,1024-1535,1536-2047,2048-2063,2064-2079,2080-2095,2096-2111)分別操作,只是在進(jìn)行寫操作的時(shí)候,把要進(jìn)行寫操作的部分寫入需要的數(shù)據(jù),其他7個(gè)不需要進(jìn)行寫操作的部分必須寫“1”。

TH58NVG1S3A的擦除操作是以塊為單位進(jìn)行的。塊地址裝載將從一個(gè)塊擦除指令60H開始,之后是三個(gè)周期的塊地址輸入,然后輸入擦除指令D0H開始擦除,通過查詢R/B來判斷擦除操作是否完成。TH58NVG1S3A內(nèi)的狀態(tài)寄存器可以確認(rèn)編程和擦除操作是否成功完成。在寫入指令(70H)到指令寄存器后,讀循環(huán)會把狀態(tài)寄存器的內(nèi)容在RE的下降沿輸出到I/O。而在新的指令到達(dá)前,指令寄存器將保持讀狀態(tài)。

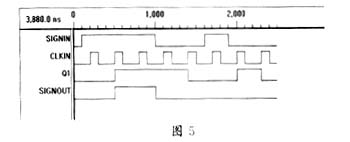

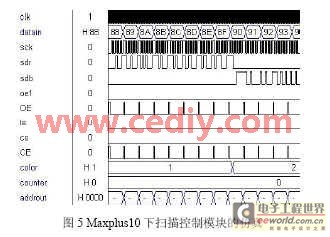

本文編程的讀操作仿真波形如圖3,寫和擦除與讀操作方式類似,不再贅述。

4 結(jié)束語

本文的創(chuàng)新點(diǎn)是成功使用CPLD控制TOSHIBA公司新推出的2Gbits NAND FLASH芯片 TH58NVG1S3A,完成了軟硬件設(shè)計(jì),使本系統(tǒng)相對于傳統(tǒng)的存儲方式來說更適用于非常惡劣的環(huán)境,有非常高的可靠性,能夠承受強(qiáng)烈的震動,具有較低的功耗,靈活性高,控制方便,已經(jīng)成功應(yīng)用于某航天項(xiàng)目中,并產(chǎn)生了很好的效果。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評論