1.引言

隨著互聯網的廣泛應用,網絡信息安全已成為人們越來越關注的問題。但是目前國內外采用最普遍的網絡安全措施防火墻類軟件存在如下缺陷:第一防火墻隔離的網絡還是基于TCP/IP協議來進行信息交換的,而TCP/IP協議是存在漏洞,因此它無法防止協議本身的漏洞;第二防火墻的運行離不開操作系統,操作系統和防火墻軟件都可能存在未知的漏洞,從而不能禁止利用這些漏洞而進行的網絡入侵和攻擊的發生,使得整個防護體系十分脆弱;第三防火墻類軟件在可信網絡與不可信網絡之間提供了網絡的直連通道,但是它并不能保證準許放行的數據的安全性,同時在對入侵檢測上也存在局限性。而物理隔離技術通過中斷內部網絡與互聯網的直接連接,不支持TCP/IP協議,不依賴于操作系統,只允許內外網間進行適度的原始數據交換,從而在根本上解決了防火墻的缺陷,為內部可信網絡可以提供更好的安全性保護。所以我國在《計算機信息系統國際互聯網管理規定》第六條中規定涉及國家秘密的計算機必須實行物理隔離。

2.物理隔離網閘

物理隔離網閘(以下簡稱網閘)是一種采用物理隔離技術,由帶有多種控制功能專用硬件在電路上切斷網絡之間的鏈路層連接,并能夠在網絡間進行安全適度的應用數據交換的網絡安全設備,它通過使內外部主機在任何時間都完全斷開,對TCP/IP協議及應用協議的剝離和重建,實現內外網在OSI模型七層的網絡隔離。通常具備有安全隔離、內核防護、協議轉換、病毒查殺、訪問控制、安全審計和身份認證,七大安全功能模塊。其硬件設備主要由三部分組成:外部處理單元、內部處理單元、隔離硬件。

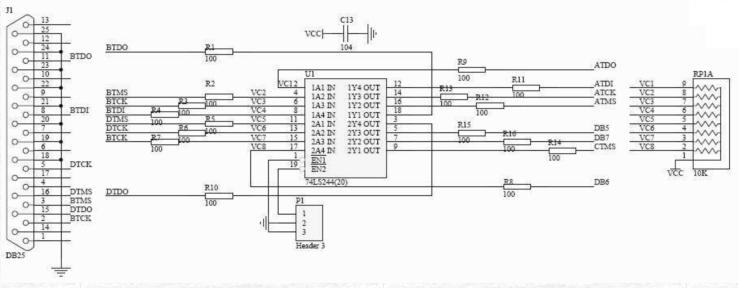

目前網閘的技術路線主要有基于SCSI的開關技術和基于總線的開關技術兩種。基于總線的實時開關技術的網閘采用雙端口靜態存儲器(Dual Port SRAM,以下簡稱DPRAM)配合基于獨立的CPLD或FPGA的控制電路,雙端口各自通過開關與獨立的計算機主機連接(如圖1)。CPLD(或FPGA)作為獨立的控制電路保證雙端口靜態存儲器的每一端口上存在一個開關,且兩個開關不能同時閉合即K1×K2=0。基于SCSI開關技術的網閘和圖1相似,只是數據通道換為SCSI硬盤接口,而存儲介質使用的是SCSI硬盤,控制單元使用專門設計的硬件電路板實現。

但是目前采用上述實現技術的網閘系統普遍存在數據交換速度低、數據交換實時性差的問題。為克服這些問題,我們在進行MIPS網閘設計中提出并應用了基于總線的雙通道循環緩沖區實時開關技術。

3. 基于總線的雙通道循環緩沖區實時開關技術

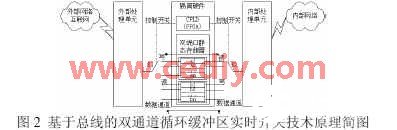

在圖1原有的設計中,進行數據交換時,內部和外部處理單元在任何時刻只有一方與隔離硬件相連。如果數據通道的速度為A bps,那么內外部處理單元間的數據交換速度最高只能達到A/2 bps,未能充分利用發揮數據通道的能力。為此我們提出如圖2的設計。

將原有設計中的DPRAM存儲區域分為A(a1,a2,…an)和B(b1,b2,…bn)兩塊(ai、bi為n個相等的小塊存儲區),K1和K2的約束為K1ai×K2ai=0且K1bi×K2bi=0(K1ai表示K1與ai相連,K2ai、K1bi、K2bi與此相同)。如此一來就將原有圖1設計中的一個雙向數據通道變為了兩個單向的數據通道,當內外部主機中的一方對ai或bi進行訪問時,另一方仍可以對aj或bj(i≠j)進行訪問,同時實現了傳輸數據的隔離。

假設開關K1,K2與每一存儲區域ai,bi的訪問是隨機進行的,那么在足夠長的一段時間內,開關K1,K2與每一存儲區域ai,bi的連接概率都是相等的,因此

我們對ai、bi區域的訪問控制進行設計,使其分別組成兩個循環緩沖區,這將進一步的減少內外部處理單元對隔離硬件訪問讀寫沖突的發生,同時也提高了交換數據的實時性。通過這樣的設計能使系統總線數據通道工作于“全雙工”狀態,提高了數據交換的速度和實時性,提升了系統的整體性能,滿足系統更高的應用需求。

4.硬件設計實現

在我們設計的網閘系統中其內外部處理單元由基于MIPS處理器的嵌入式計算機系統組成,隔離硬件模塊為雙端口RAM卡,其包含通斷控制電路,讀寫保護邏輯和數據存儲電路。隔離硬件與內外部處理單元采用SDRAM總線連接。

4.1內外部處理單元的設計實現

內外部處理單元MIPS主板的硬件電路結構上與PC機相似,如圖3所示。

圖3 MIPS主板的硬件電路框圖

內外處理單元與內外網的連接通過板上的千兆網卡實現的,監控主機系統與網閘系統的連接是通過百兆網絡口實現的,該百兆口是對網閘進行設置的唯一端口且不和其它網絡相連接。同時該嵌入式計算機系統還對外提供了如PCI、IDE、串口等常用接口。獨立的嵌入式主機為內(外)網提供了該側的全部硬件和軟件資源,保證了系統內數據可以獲得及時的處理。

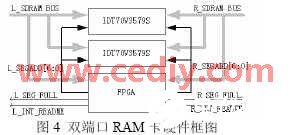

4.2雙端口RAM卡的設計實現

由于在MIPS網閘中實現數據交換的過程是通過對雙端口RAM卡上的存儲芯片的讀寫來完成的。存儲芯片作為為內外網絡的數據交換存儲區,其訪問設計方案決定了MIPS網閘交換的整體速度。為了最大限度的提高MIPS網閘的數據交換速度,我們MIPS網閘項目組采用了基于SDRAM總線的雙通道循環緩沖區實時開關技術,使得MIPS網閘數據交換速度有了突破性的提高。 圖4為雙端口RAM卡的硬件框圖。

設計中采用IDT70V3579S作為內外網間的數據緩沖區,Xilinx Virtex-II XC2V40作為控制單元。設計中采用兩片70V3579S,使得數據存儲區域和SDRAM位寬相同(64bit數據位8bit校驗位)。整個數據存儲區域為32K×72bit,容量為256KB,在設計中A、B存儲區域大小均為128KB,同時將A、B分別劃分成64段ai、bi,每段大小為2KB(因為MIPS處理器RM7065C的cache頁替換每次為2KB,如此設置有助于提高系統性能)。如此一來DPRAM地址將分為兩部分:高位地址(段地址)和低位地址(段內地址)。

在MIPS網閘中雙端口RAM卡與內外部處理單元間數據交換非常頻繁,根據第3節的設計原理我們利用FPGA來解決內外網機對雙口RAM讀寫的操作沖突,提高速據傳輸速度。在FPGA內設置有如下寄存器:REG_L_W是用于控制左端寫入的6位段地址寄存器,可以直接對應DPRAM的左端寫入段地址;REG_R_R是用于控制右端讀出的6位段地址寄存器,可以直接對應DPRAM的右端讀出段地址;REG_L_RES是對應于64段ai資源使用情況的64位段標志寄存器;REG_R_W是用于控制右端寫入的6位段地址寄存器,可以直接對應DPRAM的右端寫入段地址;REG_L_R是用于控制左端讀出的6位段地址寄存器,可以直接對應DPRAM的左端讀出段地址;REG_R_RES是對應于64段bi資源使用情況的64位段標志寄存器。通過寄存器REG_L_W、REG_R_R、REG_R_W、REG_L_R將ai、bi組成循環緩沖區,同時實現K1、K2與不同的段的連接。通過寄存器REG_L_RES、REG_R_RES指示判斷段資源的使用情況,并通知系統北橋。

當北橋向DPRAM寫入或讀出數據時,由FPGA根據其內部管理寄存器,發出高7位地址L/R_SEGADD[6:0]控制北橋具體訪問的數據段ai、bi,而且在FPGA中硬件設置使兩端不能同時對同一目標段進行訪問,從而控制K1、K2與ai、bi的連接,實現數據的隔離。

對于雙端口RAM卡與SDRAM接口的連接實現如下:首先,MIPS網閘是一個數據交換類的共享存儲系統,而MIPS主板中北橋GT芯片支持UMA(同一地址架構,Unified Memory Architecture),這一特性為設計共享存儲系統提供了很高的靈活性,為我們設計實現提供了便利。其次,在設計中采用的XC2V40芯片能與外部存儲器(如SDR/DDR SDRAM,SDR/DDR SRAM )之間建立高性能接口,非常適合我們MIPS網閘系統的應用要求。最為關鍵的是,通過比較DPRAM與SDRAM在讀寫的操作時序,兩者具有相似性,其主要時序兩者基本一致。DPRAM與SDRAM讀寫操作的最大不同在于DPRAM進行讀寫操作時,其地址是一次輸出同時數據線上信號也發生變化,而SDRAM的地址是分行列地址發出的,在發送行地址等待TRCD周期后,發送列地址,在此時刻數據信號才出現在數據線上。因此根據以上的比較分析,我們可以通過FPGA的設計使得DPRAM對于北橋來說運行于SDRAM情況之下,即北橋GT對DPRAM的操作符合SDRAM規范。

具體設計辦法如下:在北橋GT對雙端口RAM卡進行訪問并發出行地址時,我們設計北橋同時選通FPGA,在經過FPGA內部的運算后,經過TRCD的延遲,在北橋向雙端口RAM卡發出列地址及CAS的同時,FPGA發出運算后的合適的DPRAM高位地址(段地址)。此時,高位地址與低位地址將組合成為完整的DPRAM地址并同時到達DPRAM,然后再進行讀寫操作。從而實現在邏輯上北橋對DPRAM的訪問操作等同于SDRAM。

在系統運行中,高7位段地址與北橋發出的列地址中的低8位DADDR[7:0]拼接為雙端口靜態存儲器的完整地15位地址DPRAM_ADDR[14:0],完成對段內單元的訪問。FPGA的控制功能還包括:判斷DPRAM是否有數據及通知北橋數據可讀,DPRAM是否寫滿及通知北橋放棄寫過程,判斷是否DPRAM已寫到最后的地址及循環到起始地址等。FPGA還對北橋提供了L/R_SEG_FULL(A、B段寫滿信號)和L/R_INT_README(A、B段讀允許信號),這些信號均連接到GT64240的MPP(multiple purpose pins) interface上,通過以上設計從而實現了基于總線的雙通道循環緩沖區實時開關技術。

由于DPRAM實際可以認為是SDRAM的延續,而系統通過內部地址將其與系統內存SDRAM加以區分。而段地址的切換由FPGA控制完成,所以對于北橋來說,雙端口RAM卡的地址空間大小為2KB。

通過對MIPS網閘雙端口RAM卡的設計,在MIPS網閘中實現了基于SDRAM總線的雙通道循環緩沖區實時開關技術。

采用SDRAM總線通道使得雙端口RAM卡的地址作為內存的一段而存在,北橋GT對其的訪問符合SDRAM規范,因此在MIPS網閘系統進行數據交換時,數據是由內存到內存的搬運,其速度比內存到PCI、Local Bus要快,而且方便以后的軟件設計。而雙端口RAM卡的FPGA控制單元獨立工作保證了系統不會被嵌入式計算機或者其他主機遠程控制,使得網閘系統獲得絕對的安全性。采用新結構-雙通道和循環緩沖區結構提高了系統數據傳輸的速度和實時性。同時雙端口RAM卡的FPGA對ai、bi的控制管理實現了內外部處理單元對存儲單元的互斥讀寫,實現了內外網數據的隔離。

通過采用新技術提高了MIPS網閘的數據交換速度,減少了讀寫沖突的發生。在本設計中,對通道的理論利用效率可以達到99%以上,而SDRAM的速度是133MHz,因此北橋對DPRAM訪問的速度也達到了133MHz,那么MIPS網閘的交換峰值將達到133MHz×64bit×2(雙向雙片),這在性能上是很大的突破。

5.傳輸過程的控制

MIPS網閘系統中數據的處理流程如圖5所示:

圖5 系統數據處理流程

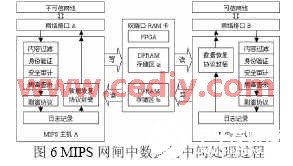

用戶請求發送給服務器,服務器將收到的數據經確認后,通過專門的通訊軟件發給MIPS網閘系統。MIPS網閘收到這些網絡數據后,在MIPS嵌入式主機系統A上對它們進行內容過濾、身份驗證、安全審計、病毒查殺,同時完成協議剝離,獲得純數據。然后將通過審核的純數據寫入內存地址中對應于雙端口RAM卡地址區間。雙端口RAM卡通過L/R_INT_README信號通知MIPS嵌入式主機系統B來讀取數據。MIPS嵌入式主機系統B讀取內存地址中對應于雙端口RAM卡地址區間獲得數據,然后將數據進行重新封裝還原,形成一個安全的網絡數據包,通過網絡端口B發送給服務器。服務器根據該數據包的服務請求從而完成整個服務過程。

數據在MIPS網閘系統的中間處理過程如圖6所示:

圖6 MIPS網閘中數據的中間處理過程

6.結論

分析介紹了物理隔離網閘技術,提出了基于總線的雙通道循環緩沖區實時開關技術,該技術克服了原有技術中存在的數據交換速度低實時性差的問題。給出了網閘中利用FPGA和雙端口RAM在SDRAM總線上實現該技術的具體實現,對該系統中數據傳輸過程的控制和處理也給予了簡要的說明。依據此技術設計實現的物理隔離系統的數據交換速度以及數據的實時性得到了提高,滿足了千兆網絡級的應用。

責任編輯:gt

電子發燒友App

電子發燒友App

評論