從制造的角度來講,FPGA測試是指對FPGA器件內部的邏輯塊、可編程互聯線、輸入輸出塊等資源的檢測。完整的FPGA測試包括兩步,一是配置FPGA、然后是測試FPGA,配置FPGA是指將FPGA通過將配

2011-10-12 15:16:25 1414

1414

大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行。

2019-07-01 17:16:45 16228

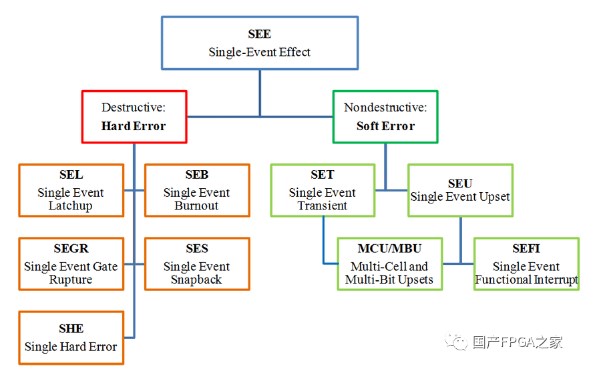

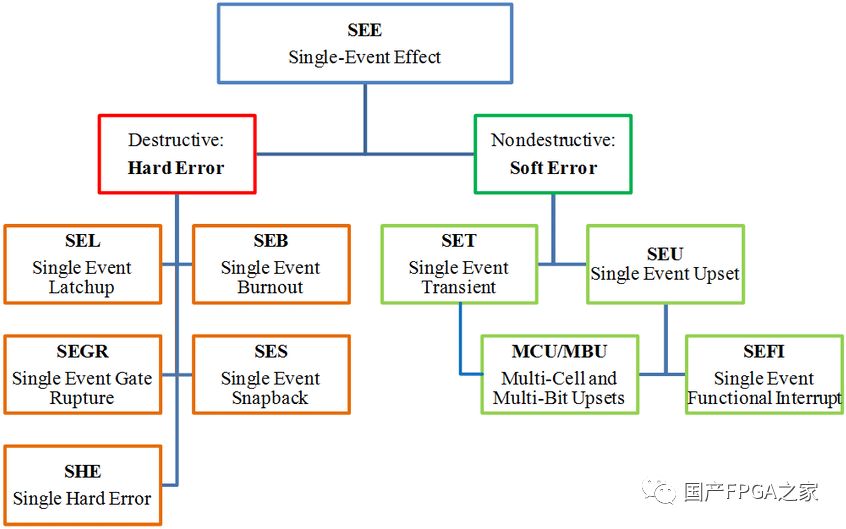

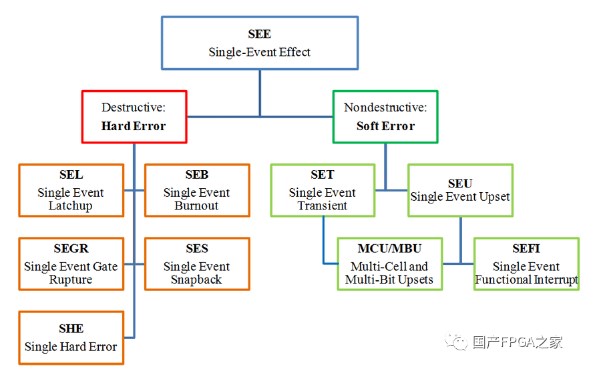

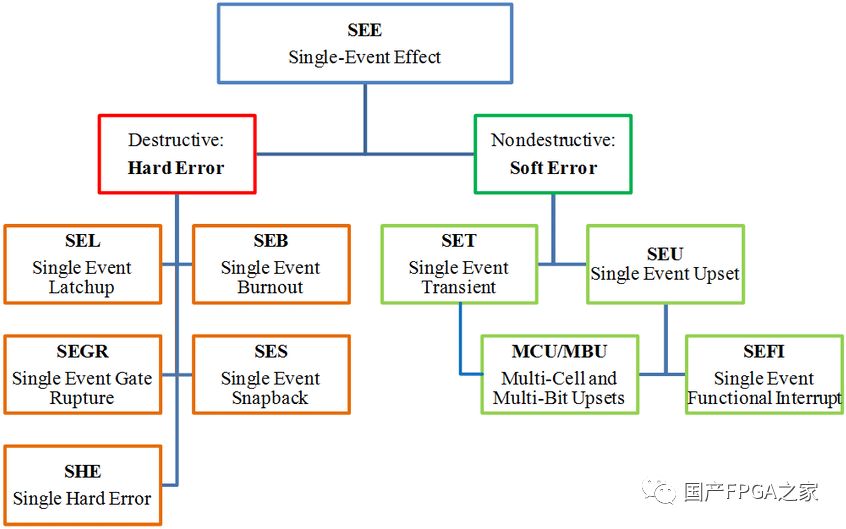

16228 不可靠,尤其是Static RAM(SRAM)型FPGA的配置存儲器受到重離子轟擊時,會導致器件邏輯布線出錯,進而引起模塊故障,甚至導致整個系統的功能中斷。對于SRAM型FPGA,配置存儲器的單粒子翻轉占整個器件翻轉總數的90%以上的比例[1],因此對配置存儲器的單粒子翻轉防護十分重要。

2020-01-26 16:31:00 5656

5656

目前,大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行。

2022-10-24 14:52:00 612

612 比特流是一個常用詞匯,用于描述包含FPGA完整內部配置狀態的文件,包括布線、邏輯資源和IO設置。大多數現代FPGA都是基于SRAM的,包括Xilinx Spartan 和Virtex 系列

2022-11-30 10:59:17 733

733 SRAM型FPGA屬于核心元器件,因此對SRAM型FPGA進行抗輻照加固設計非常必要。今天貧道主要給大家布道一下SRAM型FPGA在軌會遇到的問題及其影響。

2023-08-11 10:32:46 1091

1091

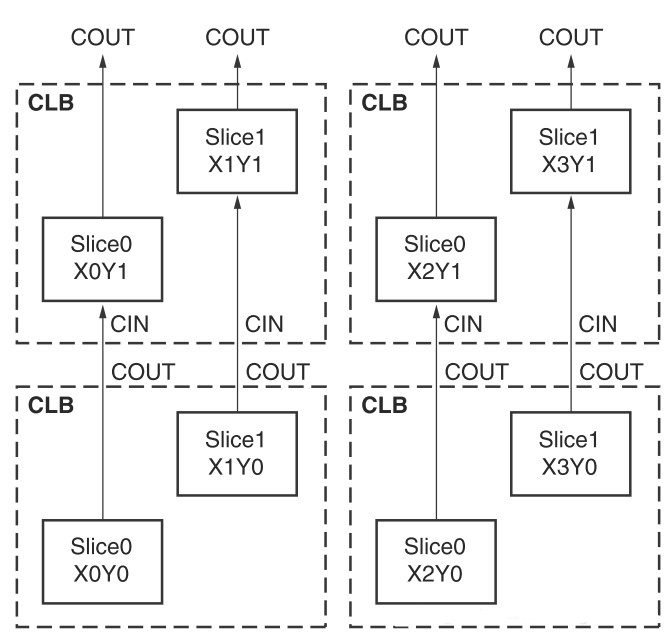

APEX的結構與此基本相同,具體請參閱數據手冊)。

三、查找表結構的FPGA邏輯實現原理

我們還是以這個電路的為例:

A,B,C,D由FPGA芯片的管腳輸入后進入可編程連線,然后作為地址線

2023-11-03 11:18:38

器件,允許系統架構師把安全體系架構規劃在核心層面,而不是放在次要的地位。許多基于SRAM的FPGA器件存在的一個很重要的問題就是每次開機必需從外部存儲器進行配置,這樣通過反向工程很容易獲取你的設計;因此

2019-06-25 08:18:11

時就已將配置數據流固化好了,重新上電后還能夠運行固有的配置數據。FPGA大都是基于SRAM來實現可編程特性,換句話說,通過JTAG實現在線編程時,在保持不斷電的情況下,FPGA能夠正常運行,而一旦掉電

2019-01-30 02:34:52

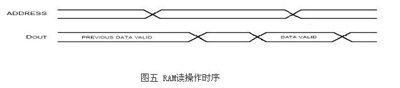

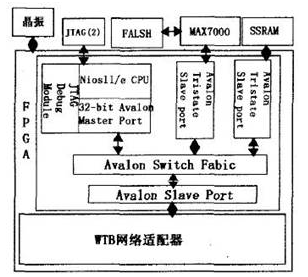

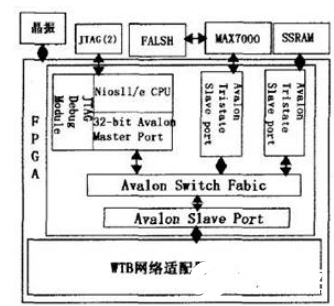

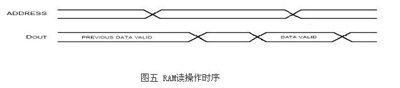

SRAM 在讀寫上有嚴格的時序要求,用 WEOECE 控制完成寫數據,具體時序如圖 7-17所示。圖 7-17 SRAM 的寫時序系統中兩塊 SRAM 分別由 DSP 和 FPGA 控制。當 DSP

2018-12-11 10:14:14

memory)和UFM塊(user flash memory),其實altera的這款CPLD器件和FPGA器件一樣是基于SRAM的,只是其內部嵌入了一塊用于存儲配置數據流的flash存儲器,即

2015-01-27 11:43:10

。 FPGA器件的結構主要有兩種:一是基于反熔絲技術,二是基于SRAM或FLASH編程。用反熔絲開關作基本元件,具有非易失性,編程完成后,FPGA的配置數據不再變化,無法重構。而基于SRAM或

2011-05-27 10:22:36

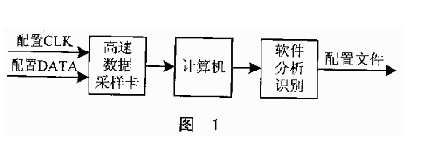

數據的分析來診斷故障。因此,用于FPGA測試的儀器或系統的關鍵技術在于:如何加快單次配置的時間,以節省測試過程中的配置時間開銷;如何實現自動重復配置和測試,將FPGA較快速度的在線配置和快速測試結合起來

2020-05-14 07:00:00

時就已將配置數據流固化好了,重新上電后還能夠運行固有的配置數據。FPGA大都是基于SRAM來實現可編程特性,換句話說,通過JTAG實現在線編程時,在保持不斷電的情況下,FPGA能夠正常運行,而一旦掉電

2015-04-13 12:29:55

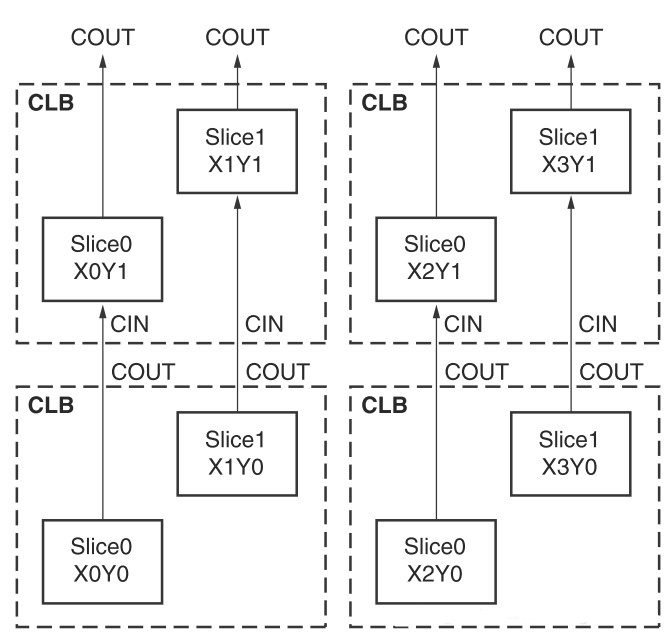

使能的觸發器,也可以配置成為鎖存器。FPGA一般依賴寄存器完成同步時序邏輯設計。一般來說,比較經典的基本可編程單元的配置是一個寄存器加一個查找表,但不同廠商的寄存器和查找表的內部結構有一定的差異,而且

2019-09-24 11:54:53

使能的觸發器,也可以配置成為鎖存器。FPGA一般依賴寄存器完成同步時序邏輯設計。一般來說,比較經典的基本可編程單元的配置是一個寄存器加一個查找表,但不同廠商的寄存器和查找表的內部結構有一定的差異,而且

2016-07-16 15:32:39

使能的觸發器,也可以配置成為鎖存器。FPGA一般依賴寄存器完成同步時序邏輯設計。一般來說,比較經典的基本可編程單元的配置是一個寄存器加一個查找表,但不同廠商的寄存器和查找表的內部結構有一定的差異,而且

2016-08-23 10:33:54

使能的觸發器,也可以配置成為鎖存器。FPGA一般依賴寄存器完成同步時序邏輯設計。一般來說,比較經典的基本可編程單元的配置是一個寄存器加一個查找表,但不同廠商的寄存器和查找表的內部結構有一定的差異,而且

2016-09-18 11:15:11

使能的觸發器,也可以配置成為鎖存器。FPGA一般依賴寄存器完成同步時序邏輯設計。一般來說,比較經典的基本可編程單元的配置是一個寄存器加一個查找表,但不同廠商的寄存器和查找表的內部結構有一定的差異,而且

2016-10-08 14:43:50

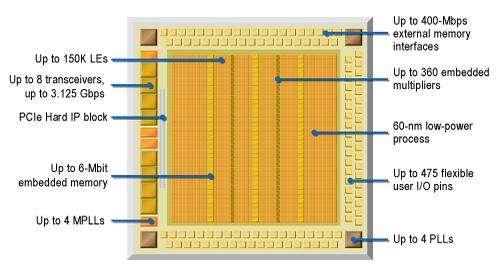

對更高密度和更快速度配置存儲器的需求。現代FPGA在配置期間需要加載多達128MB的數據。這些高密度配置比特流需要更長的時間才能從NOR閃存器件傳輸到FPGA。配置接口不僅針對讀取吞吐量進行了優化,還

2021-09-03 07:00:00

,沒有關聯。通常,可以給FPGA串連一個EPROM來存儲配置數據,實現前后功能的轉化。常規基于SRAM的FPGA的靜態重構均為全局重構。 (2)局部重構:對重構器件或系統的一部分進行重新配置,重構過程中

2011-05-27 10:22:59

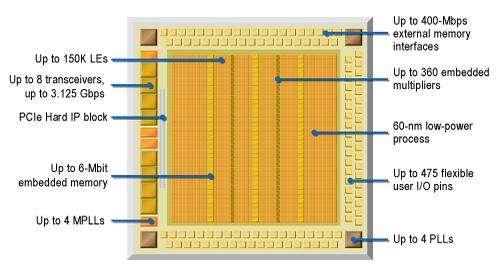

本材料的預期受眾是任何級別的系統設計師,或任何其他具有對深入了解如何選擇單個IP并將其組合成自定義SoC.功率、性能和面積(PPA)分析收集與以下各項相關的數據三個類別。除了成本之外,通常還需要

2023-08-08 06:20:44

本章節介紹了 Cyclone? IV 器件的配置和遠程系統更新。Cyclone IV (Cyclone IV GX和 Cyclone IV E)器件使用 SRAM 單元存儲配置數據。由于 SRAM

2017-11-14 10:13:30

摘要針對FFT算法基于FPGA實現可配置的IP核。采用基于流水線結構和快速并行算法實現了蝶形運算和4k點FFT的輸入點數、數據位寬、分解基自由配置。使用Verilog語言編寫,利用ModelSim

2019-07-03 07:56:53

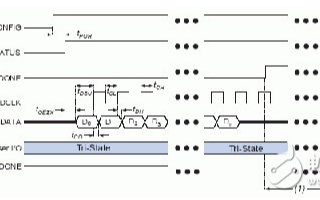

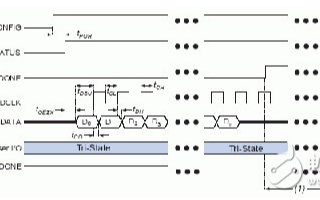

加強型配置器件(EPC16,EPC8,EPC4)等配置器件來完成,在PS配置期間,配置數據從外部儲存部件,通過DATA0引腳送入FPGA。配置數據在DCLK上升沿鎖存,1個時鐘周期傳送1位數據

2023-04-24 15:34:27

NOR閃存廣泛用作FPGA的配置設備。FPGA在工業和通信及汽車ADAS應用中的使用取決于NOR Flash的低延遲和高數據吞吐量特性。快速啟動時間要求的一個很好的例子是汽車環境中的攝像頭系統。點火

2020-09-18 15:18:38

的配置數據。FPGA大都是基于SRAM來實現可編程特性,換句話說,通過JTAG實現在線編程時,在保持不斷電的情況下,FPGA能夠正常運行,而一旦掉電,SRAM數據丟失,FPGA則一片空白,無法繼續運行

2016-07-27 16:45:59

FPGA器件都是基于RAM結構的,當然了,也有基于Flash結構的,但RAM結構的是主流,也是我們討論的重點。而RAM是易失存儲器,在掉電后保存在上面的數據就丟失了,重新上電后需要再次加載配置數據。因此

2016-08-10 17:03:57

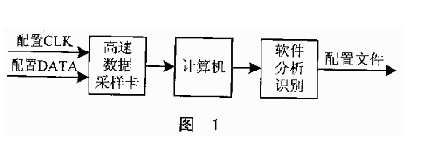

FPGA可重復配置和測試系統結構概述FPGA重復配置和測試的實現

2021-04-29 06:58:20

訪問端口和邊界掃描結構標準。隨著芯片設計和制造技術的快速發展,JTAG越來越多的被用于電路的邊界掃描測試和可編程芯片的在線系統編程。 FPGA器件都支持JTAG進行在線配置,JTAG邊界掃描的基本原理

2017-10-24 21:26:26

的提升。運算速度或者數據路徑寬度都可以進一步提高,另外,時序操作可以在結構上增加一些并行度。這些措施中,每一種都可以提高一定的性能。在利用了目標FPGA器件靈活性的結構中實現算法,會獲得比較大的好處

2021-12-15 06:30:00

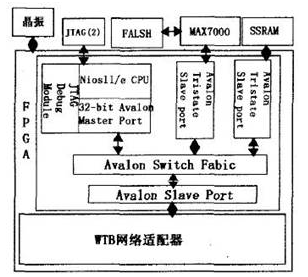

架構,采用的是FPGA+SRAM架構,可實現高速數據采集與處理。頁 碼:39-40頁主 題 詞:FPGA SMAM高速數據采集數據處理學科分類:TP274核心收錄:暫無

2018-05-09 12:09:43

輸入,數據線用作邏輯電路輸出,因為PROM的結構效率低下,無法用于實現復雜的數字邏輯。20世紀70年代開發的器件是PLA,它具有兩級邏輯,用于實現小密度邏輯。在PLA進化之后,可編程邏輯器件發生了真正

2022-10-27 16:43:59

如何實現自動重復配置和FPGA測試,將FPGA較快速度的在線配置和快速測試結合起來。

2021-04-08 06:14:46

對更高密度和更快速度配置存儲器的需求。現代FPGA在配置期間需要加載多達128MB的數據。這些高密度配置比特流需要更長的時間才能從NOR閃存器件傳輸到FPGA。配置接口不僅針對讀取吞吐量進行了優化,還專注

2021-05-26 07:00:00

隨著數字信號處理技術的不斷發展,大容量可編程邏輯器件的不斷涌現,FPGA技術越來越多地應用在大規模集成電路設計中。在此硬件系統設計中,經常會遇到需要大容量的數據存儲的情況,下面我們將針對FPGA中

2019-09-03 07:52:51

采用SRAM工藝的FPGA芯片的的配置方法有哪幾種?用單片機實現SRAM工藝FPGA的加密應用

2021-04-08 06:04:32

隨著大規模集成電路的快速發展,系統設計已從傳統的追求大規模、高密度逐漸轉向提高資源利用率,使有限的資源可以實現更大規模的邏輯設計。利用現場可編程邏輯器件FPGA的多次可編程配置特點,通過重新下載存儲

2019-08-06 07:05:37

存儲配置數據。配置數據決定了PLD內部互連和功能,改變配置數據,也就改變了器件的邏輯功能。SRAM編程時間短,為系統動態改變PLD的邏輯功能創造了條件。但由于SRAM的數據易失的,配置數據必須保存在PLD器件以外的非易失存儲器內,才能實現在線可重配置(ICR)。

2019-08-22 06:31:02

優勢,但是由于SRAM的易失性,掉電以后芯片中的配置信息將丟失,所以每次系統上電時都需要重新配置。這就使得剽竊者可以通過對FPGA的配置數據引腳進行采樣,得到該FPGA的配置數據流,實現對FPGA內部

2019-08-23 06:45:21

近年來,隨著FPGA技術的發展,支持重構的FPGA器件新品迭現。Xilinx、Altera、Lattice的FPGA器件都是SRAM查找表結構。Xilinx支持模塊化動態部分重構的器件族有

2011-05-27 10:23:28

將元器件實現快速的頂底切換,能更加方便高效讓我們去進行布局。1、單個器件在移動命令中,可按L鍵快速實現換層。2、如何實現多個器件快速實現換層。選中多個器件按快捷鍵M+S在移動命令中,可按L鍵快速實現

2018-11-07 13:50:37

采用SRAM工藝的FPGA芯片的的配置方法有哪幾種?如何對SRAM工藝FPGA進行有效加密?如何利用單片機對SRAM工藝的FPGA進行加密?怎么用E2PROM工藝的CPLD實現FPGA加密?

2021-04-13 06:02:13

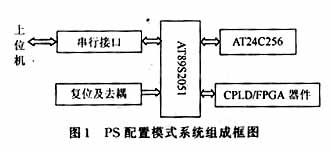

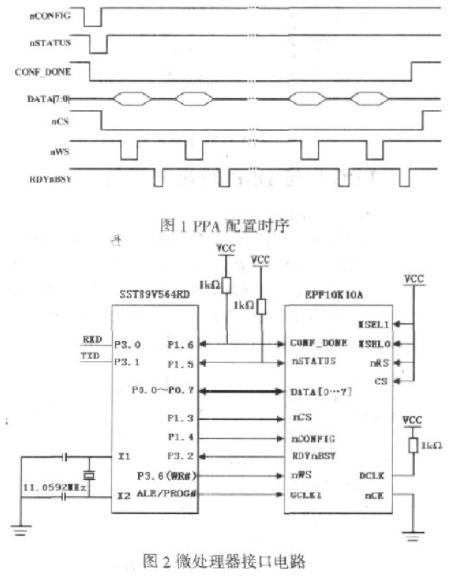

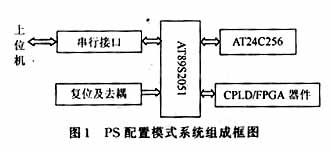

針對基于SRAM工藝的器件的下載配置問題,本文介紹采用AT89S2051單片機配合串行E2PROM存儲器,實現CPLD/FPGA器件的被動串行(PS)模式的下載配置。

2021-04-13 06:25:40

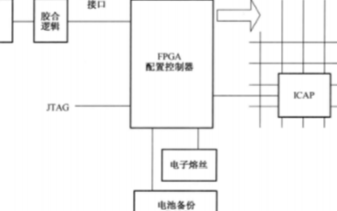

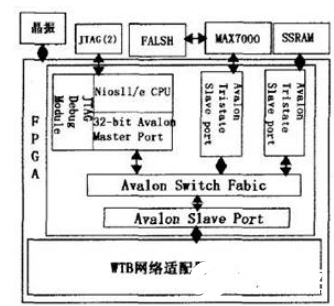

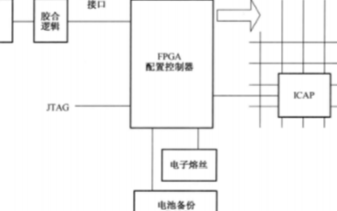

控制FPGA實現的邏輯控制功能包括與上位機軟件iMPACT和串口工具通信、燒寫Flash以及配置FPGA器件。基于模塊化的設計思想將具體功能分解成多個模塊,如圖3所示,數據與地址通道上的下標為其通道寬度

2019-05-30 05:00:05

本文討論了一種可在FPGA 上實現的FFT 結構。該結構采用基于流水線結構和快速并行乘法器的蝶形處理器。乘法器采用改進的Booth 算法,簡化了部分積符號擴展,使用Wallace 樹結構和4-2

2009-09-11 15:46:40 16

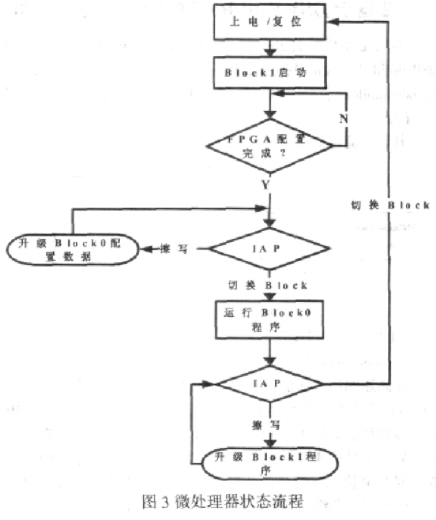

16 針對基于SRAM 結構的FPGA,詳細介紹了一種采用可在線升級的SST89V564RD微處理器對其進行上電PPA(被動并行異步)配置,不僅實現了FPGA 的在線配置,而且通過微處理器的IAP 技術

2009-09-15 16:27:50 23

23 基于SRAM 和DRAM 結構的大容量FIFO 的設計與實現作者:楊奇 楊瑩摘要:本文分別針對Hynix 公司的兩款SRAM 和DRAM 器件,介紹了使用CPLD 進行接口連接和編程控制,來構成低成本

2010-02-06 10:41:10 45

45 乘累加器在DSP算法中有著舉足輕重的地位。現在,很多前端DSP算法都通過FPGA實現。結合FPGA具體的硬件結構,提出了乘累加器在FPGA中實現的改進方法:流水線技術、CSD編碼、DA算法,

2010-08-06 14:41:38 29

29 本文介紹了Cyclone系列基于查找表(LUT)技術、SRAM工藝的FPGA配置方式,完成了用USB控制芯片作為微處理器對FPGA的進行被動態配置。

2010-08-06 15:10:16 48

48 摘要:介紹基于SRAM LUT結構的FPGA器件的上電配置方式;著重介紹采用計算機串口下載配置數據的方法和AT89C2051單片機、串行EEPROM組成的串行配置系統的設計方法及實現

2006-03-13 19:36:49 448

448 基于單片機的復雜可編程邏輯器件快速配置方法

基于SRAM(靜態隨機存儲器)的可重配置PLD(可編程邏輯器件)的出現,為系統設計者動態改變運行電路

2009-03-28 16:47:17 749

749

摘要: 介紹基于SRAM LUT結構的FPGA器件的上電配置方式;著重介紹采用計算機串口下載配置數據的方法和AT89C2051單片機、串行EEPROM組成的串行配置系統的設計方法及

2009-06-20 10:57:26 1062

1062

基于SRAM的可重配置PLD(可編程邏輯器件)的出現,為系統設計者動態改變運行電路中PLD的邏輯功能創造了條件。PLD使用SRAM單元來保存字的配置數據決

2009-06-20 11:05:37 845

845

FPGA 重復配置和測試的實現

從制造的角度來講,FPGA測試是指對FPGA器件內部的邏輯塊、可編程互聯線、輸入輸出塊等資源的檢測。完整的FPGA測試包括

2009-09-03 11:17:08 528

528

FPGA重復配置和測試的實現

從制造的角度來講,FPGA測試是指對FPGA器件內部的邏輯塊、可編程互聯線、輸入輸出塊等資源的檢測。完整的FPGA測試包括兩步,一是配置FPGA

2010-01-26 09:39:56 544

544

SRAM模塊,SRAM模塊結構原理是什么?

RAM 結構框圖如圖1 所示。它主要由存儲矩陣(又稱存儲體)、地址譯碼器和讀/寫電路 3 部分組成。存儲矩陣是存儲

2010-03-24 16:28:39 3895

3895 1 前言

針對FPGA中內部BlockRAM有限的缺點,提出了將FPGA與外部SRAM相結合來改進設計的方法,并給出了部分VHDL程序。

2 硬件設計

這里將主

2010-09-16 10:10:35 1233

1233

FPGA在現代電子系統設計中,由于其卓越性能、靈活方便而被廣泛使用,但基于SRAM的FPGA需要從外部進行配置,配置數據很容易被截獲,故存遮安全隱患。總結了當前FPGA的加密方法;提出了一種基于外部單片機的FPGA加密方法,該方法中使用外部單片機配合FPGA產生

2011-03-16 14:22:24 48

48 針對FPGA中內部BlockRAM有限的缺點,提出了將FPGA與外部SRAM相結合來改進設計的方法,并給出了部分VHDL程序。

2012-01-10 11:51:30 4422

4422

基于FPGA的嵌入式塊SRAM的設計

2017-01-19 21:22:54 15

15 通過SELECTMAP32接口配置和回讀XILINX公司生產的V5系列SRAM型FPGA,被配置的FPGA以下簡稱DUT,產生配置時序的FPGA簡稱配置FPGA。首先硬件上應將M[2:0]接成110

2017-11-17 10:16:01 8730

8730 的兼容性。 這里詳細介紹了Virtex 系列FPGA 芯片的數據流大小及結構。Virtex支持一些新的非常強大的配置模式,包括部分重新配置,這種配置機制被設計到高級應用中,以便通過芯片的配置接口能夠訪問及操作片內數據。但想要配置芯片,對它的數據流結構的了解是必不可少的。

2017-11-18 11:37:38 2027

2027 的應用。在主流的FPGA中,絕大多數都采用了SRAM來存放配置數據,稱為SRAM FPGA。這種FPGA的突出優點是可以進行多次配置。通過給FPGA加載不同的配置數據,即可令其實現不同的邏輯功能.FPGA這種可重配置的能力將給數字系統的設計帶來很大的方便。

2018-07-18 12:50:00 2407

2407

隨著現場可編程門陣列( FPGA)芯片在商業、軍事、航空航天等領域越來越廣泛的應用,其可靠性和可測試性也顯得尤為重要。本文介紹一種基于SRAM結構FPGA邏輯資源的測試編程方法,并以Xilinx公司的XC4000系列為例,在BC3192V50數模混合集成電路測試系統上,通過從串模式,實現數據的配置和測試。

2017-11-23 14:48:02 4583

4583 在FPGA中實現在應用編程(In Application Programming,IAP)有兩種方法:一種是,在電路板上加外電路。例如用MCU或CPLD來接收配置數據,在被動串行(PS)模式

2017-12-13 13:58:10 24009

24009

存儲配置數據。配置數據決定了PLD內部互連和功能,改變配置數據,也就改變了器件的邏輯功能。SRAM編程時間短,為系統動態改變PLD的邏輯功能創造了條件。但由于SRAM的數據易失的,配置數據必須保存在PLD器件以外的非易失存儲器內,才能實現在線可重配置(ICR)。

2020-01-15 07:57:00 2612

2612

本系統可用于配置所有ALTERA公司生產的基于SRAM架構的CPLD器件和XILINX公司生產的基于SRAM架構的FPGA器件以及其他主流器件制造公司生產的基于SRAM架構的器件,具有很強的通用性。由于該電路使用的元器件非常少,也可以將其制作成面積很小、便于攜帶的通用下載配置板使用。

2018-10-08 09:21:00 2654

2654

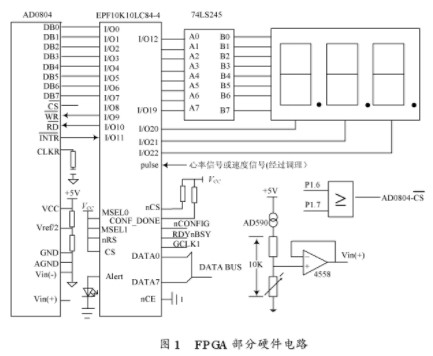

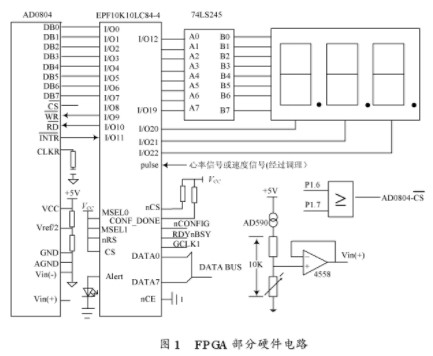

根據課題要求,設計FPGA部分硬件電路如圖1所示。FPGA芯片選用Altera公司的中檔器件FLEX-EPF10K10LC84-4,他是基于SRAM LUT結構的FPGA器件。根據傳送數據的方式

2019-08-21 08:01:00 4908

4908

介紹了采用CPLD和Flash器件對FPGA 實現快速并行配置,并給出了具體的硬件電路設計和關鍵模塊的內部編程思路。

2018-10-24 15:15:49 7

7 單片機是基于FLASH結構的,所以單片機上電直接從本地FLASH中運行。但SRAM 架構的FPGA是基于SRAM結構的,掉電數據就沒了,所以需要借助外部電路來配置運行的數據,其實我們可以借助Vivado來學習FPGA的各種配置模式。

2018-11-05 15:12:57 7298

7298 由于大規模高密度可編程邏輯器件多采用SRAM工藝,要求每次上電,對FPGA器件進行重配置,這就使得可以通過監視配置的位數據流,進行克隆設計。因此,在關鍵、核心設備中,必須采用加密技術保護設計者的知識產權。

2018-11-20 09:28:41 1967

1967

)來實現的,具有可重復編程性,可以靈活實現各種邏輯功能。由于FPGA器件采用的是SRAM 工藝,在斷電的情況下FPGA內的配置數據將丟失。所以,在典型的采用FPGA器件的電子系統中通常將FPGA

2019-01-04 14:15:02 643

643

關鍵詞:PLD , SRAM , 可重配置電路 由于SRAM的可重配置PLD(可編程邏輯器件)的出現,為系統設計者動態改變運行電路中PLD的邏輯功能創造了條件。PLD使用SRAM單元來保存字的配置

2019-02-23 14:30:01 675

675

目前市場上90%以上的FPGA來自于xilinx和altera這兩家巨頭,而這兩家FPGA的實現技術都是基于SRAM的可編程技術,FPGA內部結構基本一致,所以本文僅以xilinx的7系列FPGA介紹。

2019-10-20 09:03:00 2380

2380

目前最大的兩個FPGA廠商Altera公司和Xilinx公司的FPGA產品都是基于SRAM工藝來實現的。這種工藝的優點是可以用較低的成本來實現較高的密度和較高的性能;缺點是掉電后SRAM會失去所有配置,導致每次上電都需要重新加載。

2019-11-25 09:30:43 4029

4029

)來實現的,具有可重復編程性,可以靈活實現各種邏輯功能。由于FPGA器件采用的是SRAM 工藝,在斷電的情況下FPGA內的配置數據將丟失。所以,在典型的采用FPGA器件的電子系統中通常將FPGA

2020-01-21 17:10:00 764

764

FPGA是基于SRAM編程的,編程信息在系統掉電時會丟失,每次上電時,都需要從器件外部的FLASH或EEPROM中存儲的編程數據重現寫入內部的SRAM中。FPGA在線加載需要有CPU的幫助,并且在加載前CPU已經啟動并工作。FPGA的加載模式主要有以下幾種:

2020-04-07 08:00:00 16

16 FPGA 器件結構 1、可編程邏輯門陣列,由最小單元 LE 組成。 2、可編程輸入輸出單元 IOE。 3、嵌入式 RAM 塊,為 M4K 塊,每個的存儲量為 4K,掉電丟失。 4、布線

2020-10-30 13:05:43 530

530 后 SRAM 會失去所有配置,導致每次上電都需要重新加載。重新加載需要外部的器件來實現,不僅增加了整個系統的成本,而且引入了不穩定因素。加載過程容易受外界干擾而導致加載失敗,也容易受“監聽”而破解加載文件的比特流。雖然基于 SRAM 結構的 FPGA 存在這些缺點,但是由于其實

2020-12-16 13:34:00 24

24 及布局布線,并用ModelSim和Matlab對設計作了聯合仿真。結果表明,通過利用FPGA器件中大量的乘法器、邏輯單元及存儲器等硬件資源,采用全并行加流水結構,可在一個時鐘節拍內完成32點FFT運算的功能,設計最高運算速度可達11 ns,可實現對高速A/D采樣數據的實時處理.

2021-03-31 15:22:00 11

11 所有現代FPGA的配置分為兩類:基于SRAM的和基于非易失性的。其中,前者使用外部存儲器來配置FPGA內的SRAM后者只配置一次。 Lattice和Actel的FPGA使用稱為反熔絲的非易失性配置

2021-07-02 16:01:40 2781

2781

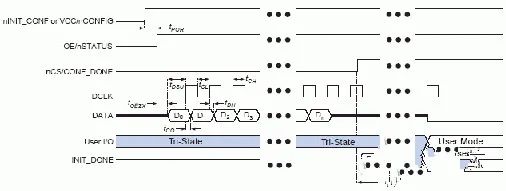

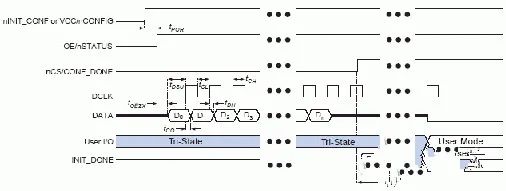

等。 FPGA器件配置方式分三大類:主動配置、被動配置和JTAG配置。 主動配置:由FPGA器件引導配置操作過程。 被動配置:由計算機或控制器控制配置過程。上電后,控制器件或主控器把存儲在外部存儲器中的數據送入FPGA器件內,配置完成之后將對器件I/O和寄存器進行初始化。初始化完成后,進入用戶

2021-09-06 09:41:56 6052

6052 FPGA采用SRAM進行功能配置,可重復編程,但系統掉電后,SRAM中的數據丟失,因此,需要在FPGA外加EPROM,將配置數據寫入其中,系統每次上電自動將數據引入SRAM中。

2022-08-10 10:12:16 1119

1119 目前,大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行。

2022-08-15 09:13:31 1887

1887 中的數據送入FPGA器件內,配置完成之后將對器件I/O和 寄存器 進行初始化。初始化完成后,進入用戶模式,開始正常工作。 一旦設計者選定了FPGA系統的配置方式,需要將器件上的MSEL引腳設定為固定值,以指示當前所采用的配置方式。 常用的配置方式有: PS配

2022-11-17 12:15:10 1141

1141 FPGA 可編程的特性決定了其實現數字邏輯的結構不能像專用 ASIC 那樣通過固定的邏輯門電路來完成,而只能采用一種可以重復配置的結構來實現, 而查找表(LUT)可以很好地滿足這一要求,目前主流的 FPGA 芯片仍是基于 SRAM 工藝的查找表結構。

2022-11-29 10:10:57 2833

2833 FPGA的原理是基于SRAM的查找表結構。通俗的講就是:可以將FPGA看做是一片SRAM,利用開發工具軟件計算出所有的輸入組合排列對應的輸出結果,然后將輸入組合作為SRAM的地址,該地址中存放的是與輸入組合對應的輸出。

2023-03-24 12:15:30 276

276 單元存儲配置數據。配置數據決定了PLD內部互連和功能,改變配置數據,也就改變了器件的邏輯功能。SRAM編程時間短,為系統動態改變PLD的邏輯功能創造了條件。但由于SRAM的數據易失的,配置數據必須保存在PLD器件以外的非易失 存儲器 內,才能實現在線可重配置(

2023-05-30 11:00:01 434

434 存儲配置數據。配置數據決定了PLD內部互連和功能,改變配置數據,也就改變了器件的邏輯功能。SRAM編程時間短,為系統動態改變PLD的邏輯功能創造了條件。但由于SRAM的數據易失的,配置數據必須保存在PLD器件以外的非易失存儲器內,才能實現在線可重配置(ICR)。

2023-05-30 10:59:00 449

449

SRAM型FPGA屬于核心元器件,因此對SRAM型FPGA進行抗輻照加固設計非常必要。今天貧道主要給大家布道一下SRAM型FPGA在軌會遇到的問題及其影響。

2023-08-11 10:30:45 1264

1264

電子發燒友App

電子發燒友App

評論