1.引言

隨著現代通信向著多業務方向發展,為了節省信道資源、降低調制解調設備的復雜度,數據復接設備得到了更充分的利用。它能將多路不同類型的數據流復接成一路高速數據流,通過信道傳輸,在收端分接出發端對應的數據流,以實現多業務雙向通信。

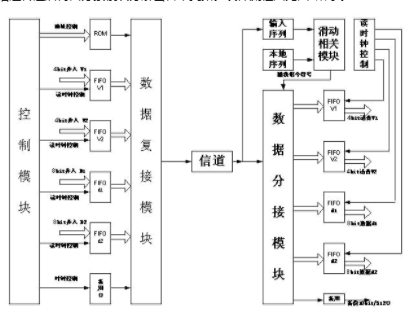

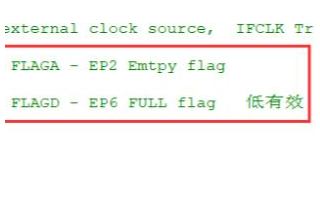

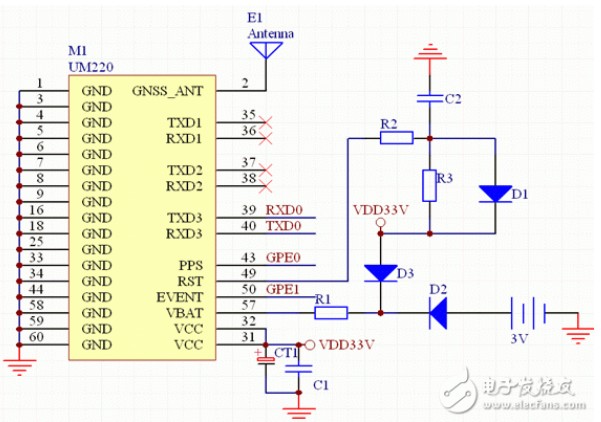

這里利用了XILINX公司的VIRTEX-ⅡPRO系列FPGA實現了數據復接、數據分接及幀同步過程。之所以選用FPGA完成設計功能,是由于數據復接、分接涉及大量的時序過程,FPGA綜合工具應用了廣泛的時序調整與流水處理技術以改善時序電路性能。巧妙地應用流水處理技術,可以實現輸入輸出端口之間寄存器的移動和均衡實現邏輯的分隔,并且不會對原有設計引入額外的處理等待延遲,可以實現高性能設計的高效率綜合,確保最優的時序性能。該設備輸入端是8路話音,16路數據,其中8路并行輸入的話音均分為V1、V2,16路并行輸入的異步數據均分為d1、d2,設備完成將并行輸入復接為一路高速數據流(復接后的幀格式見圖3)經過信道傳送后再由分接模塊分解出各個支路。設計流程圖見圖1所示。

本文結構安排如下:首先,介紹引言部分;其次,對數據復接分接、幀頭同步捕獲以及由DDS進行時鐘分頻做了詳細的設計分析,并給出了相應的設計流程圖和原理圖;再次,分析仿真結果,從結論對設計過程進行驗證;最后,總結全文。

2.數據復接方法與實現

數字復接的方法主要有按位復接、按字復接和按幀復接三種。按位復接又叫比特復接,即復接時每支路依次復接一個比特。按位復接方法簡單易行,設備也簡單,存儲器容量小,目前被廣泛采用,其缺點是對信號交換不利。按字復接,一個碼字有8位碼,它是將8位碼先儲存起來,在規定時間對各個支路輪流復接,這種方法比較復雜,具體原因后續分析。還有一種是按幀復接,這種方法的存儲容量要求太大,而且不適用于同步與異步復接情況。這里選用按字復接,原因是經過ADPCM編碼后進入的話音數據為4bit并入(共2路),這里將一組V1,V2看為8bit(1個字),數據異步接收后出來的數據,每組也為8bit。

在設計數據復接與分接設備過程中,主要有用DDS生成所需時鐘、幀結構定義、碼速調整、控制模塊設計、幀同步頭捕獲設計幾大難點,現分別做一說明:

1) DDS生成時鐘:本設計的晶振為30MHz,由總體考慮所需的話音時鐘為8kHz,異步數據為117kHz。所以可以先由30MHz時鐘源由DDS得到4.096MHz的時鐘,再由4.096MHz這個時鐘進行512分頻得到8kHz時鐘,由4.096MHz時鐘進行35分頻得到117kHz時鐘,具體原理圖見圖2。對于DDS控制字的求解針對此設計可由以下公式得到32位碼字:(見書P50)

其中gen_constant為生成控制字的模塊,clk_512和clk_35為分頻模塊。

2) 幀結構定義:對于輸入話音V1和V2其寫入時鐘為8kHz的同步時鐘,數據d1和d2其寫入時鐘為117kHz的異步時鐘。幀同步頭選用2個255bit的m序列后補一個0作為256bit同步頭,并存放在ROM中。他們經過復接后得到117kHz的高速數據流,送入信道,接收端通過同步頭捕獲模塊進行幀同步,捕獲后由數據分接模塊進行分路,得到發端對應的8路話音,16路數據。由于本設計輸入端還需要插入數據指示、話音信令等碼元(以供區分業務類別),在此,我分析了復接端多路輸入時鐘與合路后讀取時鐘的關系,同時綜合考慮同步話音的解復接后的連續性以及異步數據的重要性等問題,定義如圖2的幀格式。

這里需要強調的是異步數據在幀格式里的定義,數據是突發性質的異步數據,雖然數據的傳輸速率很高為117kbps,但是其平均速率很低,經過實際分析其平均速率約0.6K×8bps,而且該數據作為控制指令所以在幀格式設計時要特別注意,此處定義幀格式時對數據每字重復傳送3次以提高可靠性。

3) 碼速調整:碼速調整部分主要是緩沖存儲器,還包括一些必要的控制電路,這里緩沖器選用Asynchronous FIFO。在很多設計中,是通過扣除一個讀取脈沖的方法來防止緩存器的信息被取空,這樣做的問題是需要判斷寫入寫出時鐘的相位關系,并且輸出同類型數據將存在不連續性。在設計中通過利用幀定義格式以及設計一個讀時鐘控制模塊來避免緩沖讀空問題,保證了各類數據的連續性。緩沖的深度與輸入有很大關系。現計算FIFO要求具備的最低深度(其寬度話音為4bit,數據為8bit):

首先對FIFO的工作過程做一個簡要說明,Asynchronous FIFO是一個先入先出存儲器,并具有支持讀寫時鐘不同步的功能,在輸出口有empty指示(empty=1,表示下一時鐘所讀的數據為無效數據,反之為有效)。這里在控制模塊中要求在最后一位即第211個bit處對設備中所有FIFO復位,目的是防止緩沖存儲器被取空。

輸入端單路話音是以8×4(Kbit)傳送,成幀后每個數據包512(bit)中包含單路話音40×4(bit),數據包以117kbps傳送,則話音寫入FIFO的速率與讀取FIFO的速率可以表示為(1)、(2)兩式所示。

V話音=8×4(kbps) (2)

Vread=[40/(512/117)]×4=9.14×4(kbps) (3)

ΔV=1.14×4(kbps) (4)

設緩沖區深度為X,則在7個數據包完成時間內由速率差完成的深度為:

ΔX=1.14×7×512/117=34.92 (5)

這個即話音FIFO的最小深度,這里選擇深度為64,寬度為4bit的Asynchronous FIFO。

對于異步數據在每個數據包512bit中留出了8×3×3bit空間,由于數據量很小,且考慮到每幀開始會對設備所有FIFO復位一次,在此不需要考慮寫入讀出的時鐘問題,FIFO的深度只要大于7×3就可以。對于加強數據可靠性,重傳3次的問題在FIFO中不加考慮,由控制模塊完成。最后定義數據FIFO深度32,寬度8bit的Asynchronous FIFO。

4) 控制模塊的設計:這部分設計關鍵是對時鐘的控制以及時隙的安排,這個也是整個復接設備設計的主要難點,同步報頭的插入使能信號、幀格式的定義都有控制模塊中一個12位計數器來統一控制。對于異步數據每個字節重復3次傳送這個過程的設計,這里主要引入模塊設計,它通過前后時隙空余期間,利用時鐘上升沿與下降沿一起促發,將FIFO的輸出擴展為1個與FIFO輸出同相的信號并存入本地RAM,這樣解決了FIFO的先入先出的工作特點(同個數據無法返回再讀)。對于分接模塊,難點同樣也是在異步數據部分,由于在幀格式中預定了數據重復3次發送,所以在分解模塊中采取的是3中取2的方法,對異步數據進行判決。

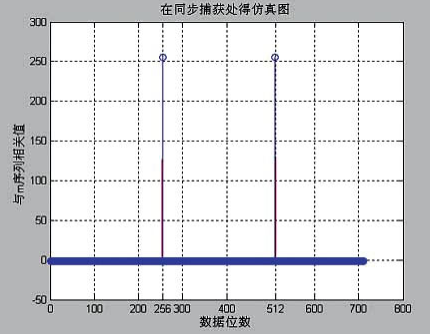

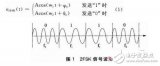

5) 幀頭同步捕獲模塊的設計:由于m序列具有很強的自相關性,利用255的m序列末尾加1個0作為同步頭。當輸入序列匹配與本地碼相匹配時將出現相關峰值(輸入序列存放在移位寄存器中),當不匹配時相關值很小。這里用2個上述碼字,分別作為幀同步頭和保密機同步頭,其相關捕獲過程的MATLAB仿真圖如圖3所示。這里在256和512處出現了相關峰值,即在這2點處本地碼與寄存器中數據匹配相關。相關檢測技術在很多文獻都有介紹,這里采取的也是通用的方法,只是在具體實現時,根據256bit來設計了一個移位寄存方法,采取2個4×64bit的移位寄存器作為輸入序列的存放地點,分別用于幀同步頭和保密機同步頭捕獲時輸入序列與本地碼元的自相關。由于在設計中需要捕獲成功的使能信號提前一個時鐘周期,因此本文的解決方法是將本地碼沿著輸入序列的反方向循環移動1bit,這樣可以在序列進入255bit時得到相關峰,以提前1個時鐘周期給出捕獲成功的使能信號。

由于信道中存在干擾,在控制模塊中不可以用m序列的自相關大小作為捕獲判斷基準值,這里設置的捕獲環路的基準值,它是通過相關峰值加上一定的偏移值而定的,這樣可使得同步的誤判率減小。用戶還可以通過設定軟基準值,即通過信噪比來自適應決定偏移值,這樣可以更加可靠的達到同步狀態。

3.仿真結果分析

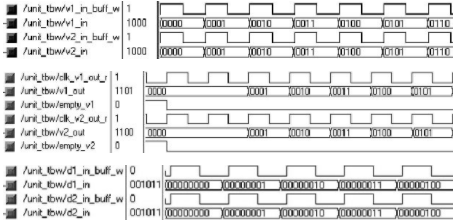

通過在ISE軟件中編寫UCF文件,把程序下載到xc2vp20-fg676中測試通過,已經作為總體設計的一部分投入使用,并使用正常。在此,對整個設計用Modesim進行仿真一下,并給出結果:當話音輸入為圖5所示,從0000到0110,寫入FIFO時鐘如圖v_in_buff_w為8kHz,則輸出見圖6所示,當時鐘下降沿促發得empty為0后,下一時鐘下降沿所抽取的數據為開始的有效值。

需要說明的是話音是同步的,必須保證話音輸出要連續,確保這個連續性跟定義的幀格式大小以及信道傳送的速據速率等因數有關。

對于異步數據部分需要不斷的對empty信號進行判斷,以確定下個時鐘下降沿抽取的數據是否有效,根據FIFO工作特點輸出指示empty為0后,下一個時鐘下降沿取得的數據有效,輸入數據見圖7,相應的輸出結果見圖8。

4.總結

數據復接在多業務通行中應用廣泛,它能將多路不同類型的數據流復接成一路高速數據流,通過信道傳輸,在收端分接出發端對應的數據流,以實現多業務雙向通信。數據復接設備的設計方法多樣,這里所做的設計方法具有一定的通用性與實用性,給出了同步、異步合路的解決方案,并且介紹了利用DDS進行產生所需時鐘的方法。在設計幀結構以及FIFO深度方面,本文也做了較詳細的推理。由于在設計數據復接、分解過程中,大量涉及進程概念,時序性很強,所以選用FPGA去完成軟過程,這相比其他器件可以進行更有效的時序調整與流水處理技術,進而改善時序電路性能。

責任編輯:gt

電子發燒友App

電子發燒友App

評論