1、鎖存器和觸發(fā)器的定義和比較

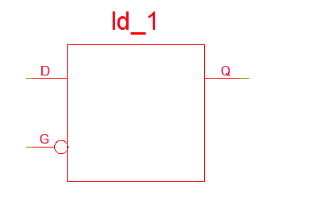

鎖存器(latch)---對脈沖電平敏感,在時鐘脈沖的電平作用下改變狀態(tài),當(dāng)Gate輸入為高電平時,輸入D透明傳輸?shù)捷敵鯭;當(dāng)Gate從高變低或者保持低電平時,輸出Q被鎖存保持不變。鎖存器是電平觸發(fā)的存儲器。

應(yīng)用場合:數(shù)據(jù)有效遲后于時鐘信號有效。這意味著時鐘信號先到,數(shù)據(jù)信號后到。在某些運算器電路中有時采用鎖存器作為數(shù)據(jù)暫存器。

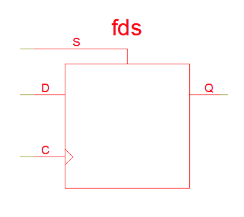

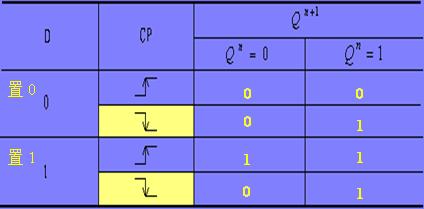

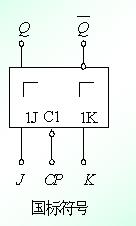

觸發(fā)器(flip-flop)---對脈沖邊沿敏感,其狀態(tài)只在時鐘脈沖的上升沿或下降沿的瞬間改變。當(dāng)時鐘信號C上升沿時刻(或者下降沿時刻),輸入D被賦值到輸出Q,其他情況保持鎖存。觸發(fā)器是邊沿觸發(fā)的存儲器。

應(yīng)用場合:時鐘有效遲后于數(shù)據(jù)有效。這意味著數(shù)據(jù)信號先建立,時鐘信號后建立。在CP上升沿時刻打入到寄存器。

比較:

1)、latch和flip-flop都是時序邏輯,所以輸出不但同當(dāng)前的輸入相關(guān)還同上一時間的輸出相關(guān);

2)、latch由電平觸發(fā),異步控制。在使能信號有效時latch相當(dāng)于通路,在使能信號無效時latch保持輸出狀態(tài)。觸發(fā)器由時鐘沿觸發(fā),同步控制。所以說,觸發(fā)器是一個同步版鎖存器;

3)、FPGA主要有觸發(fā)器和查找表組成,沒有標(biāo)準(zhǔn)的latch單元,一個latch需要更多資源才能實現(xiàn);

4)、一般的設(shè)計規(guī)則是:在絕大多數(shù)設(shè)計中避免產(chǎn)生latch。latch最大的危害在于不能過濾毛刺。這對于下一級電路是極其危險的。所以,只要能用D觸發(fā)器的地方,就不用latch;

5)、if語句或者case語句不全很容易產(chǎn)生latch。在RTL描述中,如果一個信號在一個條件的分支中被賦值,而不是在所有分支中被賦值,則該信號的前一個值就要被保留。

同步情況下(敏感列表時時鐘邊沿)用觸發(fā)器實現(xiàn),保留到下一個時鐘邊沿為止,異步情況下(即敏感列表中是電平而非時鐘的邊沿)需要由鎖存器來實現(xiàn),保留到下一個已列出的分支情況的電平有效為止。

2、鎖存器的有與無

推導(dǎo)出鎖存器的一般規(guī)則是:

1)、如果在電平觸發(fā)的always語句所有可能的執(zhí)行過程(如if/case語句)中變量沒有全部被賦值,就會產(chǎn)生鎖存器;

2)、如果在邊沿觸發(fā)的always語句所有的可執(zhí)行過程中變量沒有被全部復(fù)制,會產(chǎn)生觸發(fā)器;

3)、如果在always語句中變量在if/case的所有分支中都被賦值則綜合成組合邏輯;

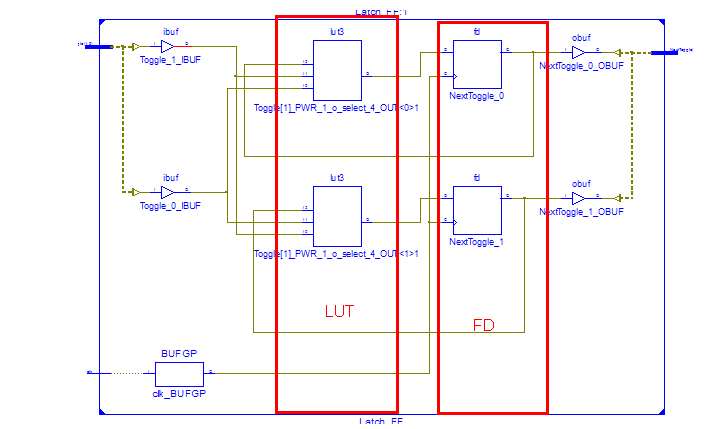

always @ (Toggle)

case (Toggle) //synthesis full_case

2‘b01: NextToggle = 2’b10;

2‘b10: NextToggle = 2’b01;

endcase

always @ (Toggle)

case (Toggle)

2‘b01: NextToggle = 2’b10;

2‘b10: NextToggle = 2’b01;

endcase

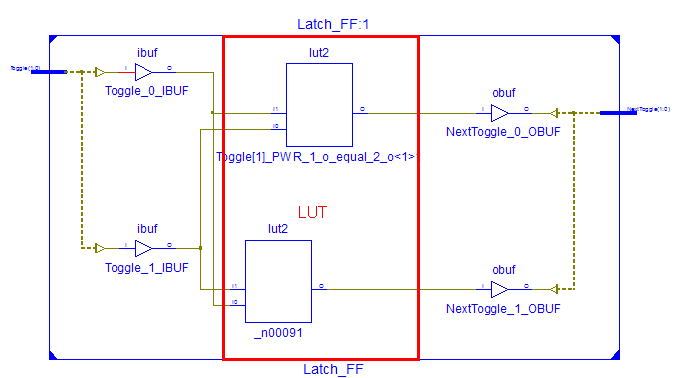

第一種寫法用編譯命令synthesis full_case把case語句補全,效果和default語句或?qū)ase列舉出所有情況類似。

此時沒有鎖存器,只用兩個2輸入的LUT完成2輸入2輸出的邏輯功能,純粹的組合邏輯。

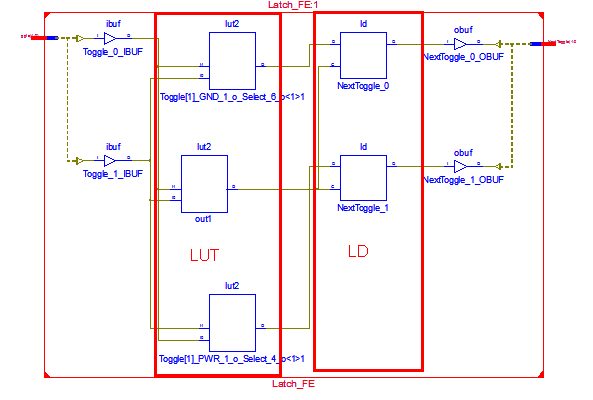

第二種寫法沒有將case的所有情況列舉出,就產(chǎn)生了鎖存器LD。

查看Xilinx的庫手冊,LD是透明鎖存器,當(dāng)G使能的時候,Q輸出D的值;當(dāng)G不使能的時候,Q保持上一狀態(tài)的值。

以下改用的時鐘的上調(diào)沿觸發(fā),生成了兩個D觸發(fā)器,當(dāng)時鐘上調(diào)沿來臨時用輸入端D更新輸出端Q的數(shù)據(jù)。

always @ (posedge clk)

case (Toggle)

2‘b01: NextToggle = 2’b10;

2‘b10: NextToggle = 2’b01;

endcase

這說明邊沿觸發(fā)的always塊中,即使if.。.else或者case沒寫全也不會出現(xiàn)鎖存器。

電子發(fā)燒友App

電子發(fā)燒友App

評論