,從而能夠降低成本,實(shí)現(xiàn)傳統(tǒng)的在線仿真器和邏輯分析儀器的功能,并在一定的條件下實(shí)現(xiàn)實(shí)時(shí)跟蹤和分析,進(jìn)行軟件代碼的優(yōu)化。一、邊界掃描技術(shù)(JTAG)邊界掃描技術(shù)是為了滿足當(dāng)今深度嵌入式系統(tǒng)調(diào)試的需要而被

2020-08-17 16:23:25

8使用邏輯分析儀解決常見調(diào)試問題的提示(AN 1326)

2019-10-22 12:31:31

Analyzer Interface,即邏輯分析儀接口。這里的邏輯分析儀接口是針對(duì)于外部邏輯分析儀的。調(diào)試者可以設(shè)置FPGA器件內(nèi)部多個(gè)信號(hào)映射到一個(gè)預(yù)先保留或者暫時(shí)不使用的I/O接口上,從而通過較少的I

2015-09-02 18:39:49

出問題出現(xiàn)的位置。然后有的放矢,很快就可以找出該模塊的問題所在。通過FPGA內(nèi)部各模塊的關(guān)鍵計(jì)數(shù)分析,來定位分析問題,在設(shè)計(jì)上沒有任何難度。不過需要外部CPU或者FPGA嵌入式CPU的配合使用。

2018-06-07 17:57:14

如今,隨著IT行業(yè)的火熱,嵌入式成了IT行業(yè)熱門之一,嵌入式技術(shù)執(zhí)行專用功能并被內(nèi)部計(jì)算機(jī)控制的設(shè)備或者系統(tǒng)。嵌入式系統(tǒng)不能使用通用型計(jì)算機(jī),而且運(yùn)行的是固化的軟件,用術(shù)語表示就是固件

2019-10-17 06:41:08

嵌入式塊ram使用為rom(只讀存儲(chǔ)器)使用PC端的signaltap ii軟件與FPGA內(nèi)部搭建的片上邏輯分析儀連接,時(shí)刻查看FPGA內(nèi)部的信號(hào)。使用Quartus II軟件中提

2021-12-17 08:00:26

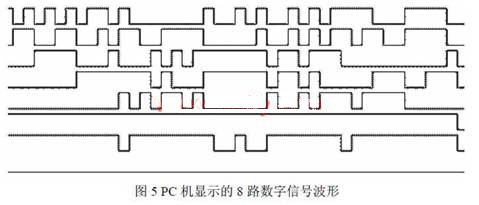

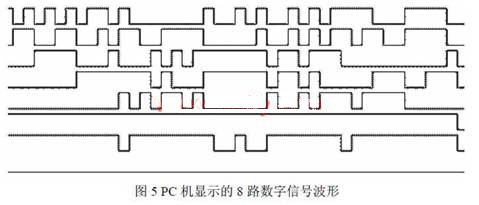

孕龍PC-Based邏輯分析儀是基于PC機(jī)使用的、專門分析IC數(shù)字信號(hào)的便攜式邏輯分析儀,相對(duì)于臺(tái)式邏輯分析儀和示波器而,基于PC機(jī)的PC-Based邏輯分析儀更由于其價(jià)格低、分析全面、分析能力強(qiáng)等

2015-08-05 17:30:06

和Mobileye的輔助駕駛系統(tǒng)等產(chǎn)品都非常重視嵌入式視覺技術(shù)的發(fā)展?jié)摿Α=Y(jié)果,很多嵌入式系統(tǒng)設(shè)計(jì)人員開始思考如何實(shí)現(xiàn)嵌入式視覺功能。本文研究嵌入式視覺的發(fā)展機(jī)遇,對(duì)比實(shí)現(xiàn)這一技術(shù)的各種處理器選擇,介紹幫助工程師在其設(shè)計(jì)中采用視覺功能的業(yè)界聯(lián)盟。

2019-08-22 06:43:16

嵌入式邏輯分析儀。 擁有這些工具可得到最佳的結(jié)果,而不是用與先前工具相同的方法。資源、靜態(tài)參數(shù)和動(dòng)態(tài)參數(shù)通常約束了內(nèi)部邏輯分析儀和外部邏輯分析儀。本文對(duì)這兩種類型工具的約束進(jìn)行了比較,考察如何最佳

2010-01-08 15:05:27

調(diào)試FPGA時(shí),TD軟件是否支持內(nèi)部邏輯分析(抓波形)功能?

2023-08-11 10:32:27

邏輯分析儀可以用啥軟件啊?

2016-05-27 17:19:32

讓嵌入式研發(fā)工程師人手一機(jī)邏輯分析儀———專訪***孕龍科技儀器事業(yè)處業(yè)務(wù)部業(yè)務(wù)經(jīng)理鄭銘國

2010-03-17 16:29:43

分析儀和示波器既在融合,也在測試原理上發(fā)生了較大的差異;再加上IT技術(shù)發(fā)展,基于計(jì)算機(jī)接口技術(shù)和處理技術(shù)的采集式虛擬邏輯分析儀出現(xiàn),邏輯分析儀已逐漸在降低成本,走入普通研究室,邏輯分析儀和示波器一樣已逐漸

2017-09-28 09:30:56

分析儀在嵌入式系統(tǒng)的研發(fā)過程量測當(dāng)中,是占有極大的關(guān)鍵地位,但是在目前市場整個(gè)產(chǎn)品研發(fā)當(dāng)中,示波器和邏輯分析儀其實(shí)是要相輔相成的,如此在產(chǎn)品的研發(fā)時(shí)間才會(huì)更加快速,也才會(huì)更加縮短產(chǎn)品的上市時(shí)間,進(jìn)而為公司

2015-08-06 13:49:11

主要用來測試以微處理器為核心的數(shù)字系統(tǒng),在硬件電路、嵌入式系統(tǒng)和監(jiān)控軟件的研制和調(diào)試過程中,都是一個(gè)必備的優(yōu)秀工具。邏輯分析儀具有豐富的觸發(fā)條件,不管被測系統(tǒng)多么復(fù)雜,邏輯分析儀都能準(zhǔn)確地找到那些隱蔽

2017-08-07 10:27:22

發(fā)生了“什么”事件。定時(shí)分析通常用波形顯示數(shù)據(jù),狀態(tài)分析通常用列表顯示數(shù)據(jù)。小結(jié)邏輯分析儀主要用來測試以微處理器為核心的數(shù)字系統(tǒng),在硬件電路、嵌入式系統(tǒng)和監(jiān)控軟件

2017-08-18 10:06:38

通道總共的存儲(chǔ)點(diǎn)數(shù)。時(shí)鐘電路:根據(jù)需要選擇外部時(shí)鐘或者內(nèi)部時(shí)鐘對(duì)輸入信號(hào)進(jìn)行采集和存儲(chǔ)。根據(jù)采樣時(shí)鐘的來源不同,邏輯分析儀可以有兩種工作模式。當(dāng)使用內(nèi)時(shí)鐘時(shí)叫Timing 模式,也叫異步分析,通常

2018-04-02 09:53:16

相應(yīng)的性能,但是卡式虛擬邏輯分析儀也有很大缺點(diǎn),它需要配備電腦才能使用,尤其數(shù)字測試中,工程師往往會(huì)陷入一堆PCB板中,采用旋轉(zhuǎn)按鈕的儀器要比在屏幕上移動(dòng)鼠標(biāo)更加方便。技術(shù)的發(fā)展也逐漸把示波器和邏輯

2016-01-11 17:10:27

數(shù)字電路的高速發(fā)展,邏輯分析儀的需求量越來越大,并逐步作為調(diào)試數(shù)字電路的終極工具。邏輯分析儀的發(fā)展邏輯分析儀剛出來的那幾年,價(jià)格不菲,沒幾個(gè)人聽過邏輯分析儀這東西,買的起的企業(yè)都是大牌子,能夠研發(fā)這種

2016-08-23 16:31:00

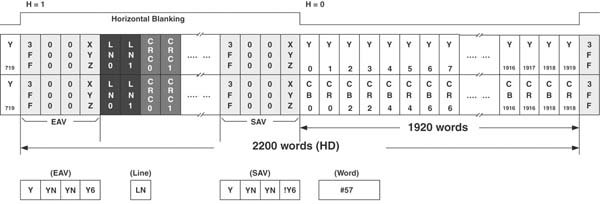

,或者在設(shè)計(jì)出現(xiàn)問題時(shí),快速定位和解決問題。結(jié)果表明,邏輯分析儀在數(shù)字電路的設(shè)計(jì)、調(diào)試和分析中,起著很重要的作用。關(guān)鍵字:LCD、邏輯分析儀、總線分析、觸發(fā)一、引言邏輯分析儀是數(shù)字設(shè)計(jì)驗(yàn)證與調(diào)試過程中公認(rèn)

2017-10-19 09:07:43

您需要同時(shí)觀看 16 位計(jì)數(shù)器的輸入和輸出信號(hào),以確定定時(shí)錯(cuò)誤時(shí),選用不正確的工具將會(huì)耗費(fèi)大量時(shí)間。采用邏輯分析儀是對(duì)于上述問題的最好解決方案。本文將詳細(xì)講述邏輯分析儀的基本原理以及它的功能。關(guān)鍵詞

2008-11-27 08:19:21

邏輯分析儀在數(shù)字電路測試中的觸發(fā)選擇延遲觸發(fā)有哪幾種類型?邏輯定時(shí)分析儀和邏輯狀態(tài)分析儀的區(qū)別是什么?

2021-04-12 06:55:10

的不斷融合中尋求發(fā)展方向,依托不斷進(jìn)步的計(jì)算機(jī)技術(shù),虛擬邏輯分析儀吸收融合了諸如邏輯筆、協(xié)議分析儀等眾多數(shù)字測量儀器的功能,使用Windows系統(tǒng)平臺(tái),配以簡單易用的用戶界面,進(jìn)一步化簡了觸發(fā)的難題

2018-03-16 15:57:00

ELA-500嵌入式邏輯分析儀是用于調(diào)試硬件相關(guān)問題的組件。

調(diào)試信號(hào)從正在調(diào)試的IP連接到ELA-500,ELA-500將信號(hào)與目標(biāo)值進(jìn)行比較并驅(qū)動(dòng)操作。有一個(gè)可選的跟蹤功能,可用于在任何時(shí)間點(diǎn)生成調(diào)試信號(hào)的歷史記錄。

2023-08-02 08:30:37

ELA-600嵌入式邏輯分析儀是用于調(diào)試硬件相關(guān)問題的組件。

調(diào)試信號(hào)從被調(diào)試的IP連接到ELA-600,ELA-600將信號(hào)與目標(biāo)值進(jìn)行比較并驅(qū)動(dòng)操作。有一個(gè)可選的跟蹤功能,可用于在任何時(shí)間點(diǎn)生成調(diào)試信號(hào)的歷史記錄。

ELA-600可以被配置為跟蹤到集成SRAM或通過ATBv4接口。

2023-08-02 10:22:10

入門級(jí)的邏輯分析儀的特點(diǎn)主要有以下幾個(gè)方面 ● 256Mbit的板載內(nèi)存保證高達(dá)1.6Gbps采樣數(shù)據(jù)的實(shí)時(shí)存儲(chǔ)。入門級(jí)邏輯分析儀大都會(huì)對(duì)帶寬或者存儲(chǔ)深度的指標(biāo)進(jìn)行妥協(xié),而大大降低此類邏輯分析儀的實(shí)用性

2016-07-21 15:38:26

標(biāo)號(hào)的兩個(gè)晶振也會(huì)有一定的誤差。我們可以利用邏輯分析儀(也就是利用FPGA的時(shí)鐘)去測量一下PC發(fā)送UART時(shí)的bit時(shí)間寬度。由于波特率為115200,在采樣時(shí),一般采用16倍頻采樣。此時(shí)采樣頻率比較

2023-03-17 20:37:18

TLA系列邏輯分析儀說明書應(yīng)用:硬件調(diào)試和校驗(yàn)處理器/總線高度和校驗(yàn)嵌入式軟件集成,調(diào)試和校驗(yàn)[hide]TLA系列邏輯分析儀說明書.pdf[/hide] [此貼子已經(jīng)被作者于2009-12-14 11:47:42編輯過]

2009-12-14 11:47:03

定時(shí)分析儀、二是狀態(tài)分析儀。邏輯分析儀的主要技術(shù)指標(biāo)為以下六個(gè)方面:通道數(shù)、定時(shí)采樣速率、最高帶寬、狀態(tài)分析速率、每通道記錄長度、測試連接夾具。邏輯分析儀與示波器類似,但兩者在使用和性能上還是有區(qū)別

2017-07-05 09:21:17

`邏輯分析儀的連接如圖,運(yùn)行后可以看到燈在閃,也就是有方波出來,可是邏輯分析儀卻沒有任何東西出來,是我連接的不對(duì)還是需要按下哪些按鈕才可以工作,請(qǐng)教大家一下,謝謝...!`

2013-07-16 15:19:36

。Ⅲ、外接邏輯分析儀有改變FPGA設(shè)計(jì)中信號(hào)原來狀態(tài)的可能,因此難以保證信號(hào)的正確性。Ⅳ、傳統(tǒng)的邏輯分析儀價(jià)格昂貴,將會(huì)加重設(shè)計(jì)方的經(jīng)濟(jì)負(fù)擔(dān)。嵌入式邏輯分析儀 :SignalTap II基本上采用

2019-12-04 10:30:42

AES有哪些應(yīng)用實(shí)例?嵌入式邏輯分析儀是如何加速SoPC設(shè)計(jì)的?

2021-04-26 06:40:55

今天用邏輯分析儀分析一個(gè)iic協(xié)議,發(fā)現(xiàn)不用分析儀時(shí) 傳感器通訊過程沒問題,加上分析儀時(shí),通訊過程發(fā)現(xiàn)有時(shí)會(huì)發(fā)錯(cuò)數(shù)據(jù),數(shù)據(jù)有個(gè)別錯(cuò)誤。最后找半天才發(fā)現(xiàn),51單片機(jī)驅(qū)動(dòng)能力不夠,用的是P3口,內(nèi)部上拉能力不夠,需要外部再上拉電阻。上拉電阻后,加上邏輯分析儀程序也沒問題了。

2019-09-24 23:36:02

分析儀對(duì)下降沿進(jìn)行測量時(shí),其結(jié)果如圖1.2所示。圖1.2 邏輯分析儀測量下降沿結(jié)果邏輯分析儀的測量原理是采用一定的頻率,對(duì)輸入信號(hào)與設(shè)定的門限電壓進(jìn)行比較,當(dāng)輸入電平大于門檻電壓時(shí)為邏輯1,當(dāng)輸入電平

2017-10-13 09:23:54

做嵌入式驅(qū)動(dòng)開發(fā),會(huì)使用邏輯分析儀是必不可少的技能。什么情況需要使用邏輯分析儀當(dāng)你編寫驅(qū)動(dòng)與設(shè)備通信讀寫數(shù)據(jù)遇到問題時(shí),可以用邏輯分析儀排除硬件問題,這樣我們就可以安心找軟件的bug了。這里我以

2021-08-06 08:41:40

什么是邏輯分析儀?邏輯分析儀的工作原理是什么?邏輯分析儀有哪些分類?邏輯分析儀的功能是什么?邏輯分析儀有那些技術(shù)指標(biāo)?

2021-06-15 06:59:00

使用,尤其數(shù)字測試中,工程師往往會(huì)陷入一堆PCB板中,采用旋轉(zhuǎn)按鈕的儀器要比在屏幕上移動(dòng)鼠標(biāo)更加方便。技術(shù)的發(fā)展也逐漸把示波器和邏輯分析儀的功能融合在一起,成為混合式的儀器(MSO),也稱混合信號(hào)測試儀

2010-04-26 14:23:57

什么是基于LabVIEW的邏輯分析儀,到底是干什么用的呀?有誰知道嗎?

2011-04-20 19:54:41

是一件困難而又讓人畏縮的任務(wù)。許多工程師用慣了示波器,同時(shí)為了節(jié)約時(shí)間,可能會(huì)選擇購買三四臺(tái)示波器,以便一次探測多個(gè)信號(hào)。邏輯分析儀可以探測多個(gè)數(shù)字信號(hào),但調(diào)試任務(wù)非常復(fù)雜,使用邏輯分析儀所帶來的設(shè)置

2008-11-26 09:56:14

摘要介紹一種16通道便攜式邏輯分析儀,通過FPGA將高速數(shù)據(jù)采樣并緩存,采用USB控制芯片和FPCA協(xié)同控制將數(shù)據(jù)通過USB接口發(fā)送到電腦的上位機(jī)上顯示,簡化了以往邏輯分析儀硬件電路部分,降低

2019-06-18 07:56:45

FPGA的特點(diǎn): (1)采用FPGA設(shè)計(jì)ASIC電路(專用集成電路),用戶不需要投片生產(chǎn),就能得到合用的芯片。 更多嵌入式學(xué)習(xí)可以加75463 4522 (2)FPGA可做其它全定制或半定制ASIC

2017-07-07 09:44:22

各位朋友,請(qǐng)問一下哪些行業(yè)會(huì)使用到邏輯分析儀!謝謝了!

2011-03-30 16:06:07

由于項(xiàng)目需要,我需要申購一臺(tái)邏輯分析儀,在此問下各位同學(xué)幾個(gè)問題:1、邏輯分析儀主要看哪幾個(gè)參數(shù)2、一般的邏輯分析儀在什么價(jià)位3、哪個(gè)品牌的邏輯分析儀性價(jià)比高些謝謝大家啦!

2014-05-12 16:29:44

本帖最后由 eehome 于 2013-1-5 09:50 編輯

基于FPGA的簡易邏輯分析儀

2012-07-19 19:01:30

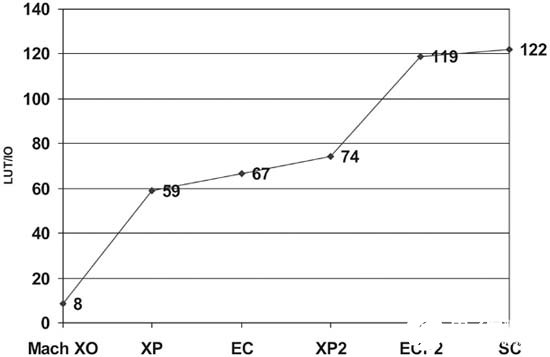

所示。 隨著可編程邏輯器件的發(fā)展,Altera公司研發(fā)了可以嵌入軟 CPU核的 Cyclone系列和 Stratix系列的 FPGA芯片。嵌入式軟核與普通硬核的昀大差別在于它的可裁減性,設(shè)計(jì)者可根據(jù)

2019-07-24 06:31:45

的發(fā)展而迅速發(fā)展起來。分析當(dāng)前存在的各種嵌入式移動(dòng)數(shù)據(jù)庫系統(tǒng)的體系結(jié)構(gòu),我們考慮采用一種總體上采用組件方式設(shè)計(jì)、組件內(nèi)部采用模塊化方式設(shè)計(jì)的嵌入式移動(dòng)數(shù)據(jù)庫。

2019-10-11 06:44:28

邏輯分析儀探頭的負(fù)荷模型請(qǐng)問如何使用邏輯分析儀來探測高速數(shù)字系統(tǒng)?

2021-04-13 06:03:19

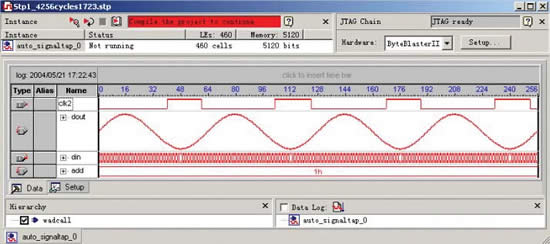

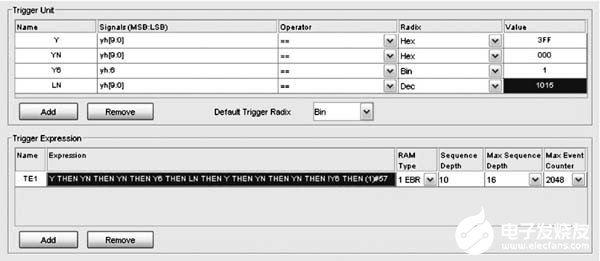

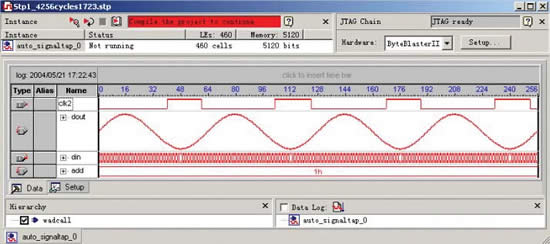

本文將介紹SignalTap II邏輯分析儀的主要特點(diǎn)和使用流程,并以一個(gè)實(shí)例介紹該分析儀具體的操作方法和步驟。

2021-04-29 06:12:52

怎樣使用keil邏輯分析儀啊

2020-05-22 14:47:47

復(fù)雜高速嵌入式系統(tǒng)的設(shè)計(jì)、開發(fā)、測試和調(diào)試面臨著新的挑戰(zhàn),如何利用最新的邏輯分析儀功能解決這些棘手問題?

2021-04-14 06:00:07

基于虛擬儀器技術(shù)的邏輯驗(yàn)證分析儀該怎樣去設(shè)計(jì)?

2021-05-12 06:22:35

推動(dòng)FPGA調(diào)試技術(shù)改變的原因是什么外部邏輯分析儀受到的限制是什么如何用內(nèi)部邏輯分析儀調(diào)試FPGA

2021-04-30 06:44:08

示波器邏輯分析儀在電子測試領(lǐng)域,示波器主要用于信號(hào)波形的采集和再現(xiàn),主要用于對(duì)模擬信號(hào)和模擬電路的測試。隨著數(shù)字技術(shù)發(fā)展,對(duì)數(shù)字信號(hào)測試越來越重要,最早的數(shù)字信號(hào)測試,往往借助于示波器,后來出現(xiàn)了

2010-04-26 14:25:06

ARM CoreSight ELA-500嵌入式邏輯分析儀提供對(duì)ARM IP和第三方IP的低電平信號(hào)可見性。

當(dāng)與處理器一起使用時(shí),它提供加載、存儲(chǔ)、推測性獲取、緩存活動(dòng)和事務(wù)生命周期的可見性,這些

2023-08-16 07:15:13

是能夠通過高級(jí)跟蹤總線(ATB)獲取跟蹤數(shù)據(jù),并且有可能具有8個(gè)觸發(fā)狀態(tài)而不是只有5個(gè)。

有關(guān)ELA-600的更多信息可在ARM CoreSight ELA-600嵌入式邏輯分析儀產(chǎn)品頁面和本教程參考資料部分的ELA-600技術(shù)參考手冊(cè)(TRM)中找到

2023-08-12 06:51:59

link logic邏輯分析儀調(diào)試器有哪些優(yōu)點(diǎn)呢?link logic邏輯分析儀調(diào)試器有哪些功能呢?

2022-02-24 06:13:38

怎么DIY邏輯分析儀?

2021-05-07 07:04:16

什么情況下需要使用邏輯分析儀呢?怎樣去使用LA1010邏輯分析儀呢?

2021-11-10 07:10:17

公司要我們提需求,我是做邏輯的,問我需要不需要邏輯分析儀,我們FPGA外接很多驅(qū)動(dòng)芯片,這種情況下是不是會(huì)大量用到邏輯分析儀呢?還請(qǐng)有經(jīng)驗(yàn)的人解惑啊!

2014-04-23 19:46:34

探頭在邏輯分析儀中作用是什么?邏輯分析儀由那幾部分組成?

2021-05-07 06:57:28

與傳統(tǒng)的邏輯分析儀相比,虛擬邏輯分析儀有什么優(yōu)勢?虛擬邏輯分析儀的工作原理是什么?怎樣去設(shè)計(jì)虛擬邏輯分析儀的觸發(fā)模塊?USB2.0接口該怎樣去設(shè)計(jì)?

2021-04-15 06:48:27

虛擬FPGA邏輯驗(yàn)證分析儀的工作原理是什么?虛擬FPGA邏輯驗(yàn)證分析儀有哪幾個(gè)主要工作環(huán)節(jié)?

2021-04-29 07:07:24

邏輯分析儀是什么? 邏輯分析儀有什么作用? 邏輯分析儀有什么功能? 邏輯分析儀是分析數(shù)字邏輯關(guān)系的一種分析儀器,將被測信號(hào)通過比較器進(jìn)行判定,高于參考電壓者為High,低于參考電壓者為Low,在

2015-11-05 11:43:56

邏輯分析儀是常用的電子儀器之一,主要應(yīng)用于做數(shù)字電路測試,FPGA調(diào)試,CPU/DSP調(diào)試,數(shù)字IQ/IF分析,無線通信/雷達(dá)接收機(jī)測試等場合。邏輯分析儀由模塊和計(jì)算機(jī)組成(當(dāng)然還有探頭),模塊負(fù)責(zé)

2019-06-28 07:51:30

深入了解邏輯分析儀入門手冊(cè)引言與許多電子測試和測量工具一樣,邏輯分析儀是一種針對(duì)特定類型問題的解決方案。它是一種通用工具,可以幫助您調(diào)試數(shù)字硬件、檢驗(yàn)設(shè)計(jì)和調(diào)試嵌入式軟件。對(duì)設(shè)計(jì)數(shù)字電路的工程師來說

2009-11-19 11:40:22

I2C 是嵌入式領(lǐng)域最常用的串行通信接口之一,讀寫時(shí)序較復(fù)雜,調(diào)試時(shí)常因時(shí)序問題導(dǎo)致通訊不暢。 1、示波器和邏輯分析儀測試信號(hào)波形與邏輯 調(diào)試時(shí)將示波器和邏輯分析儀的探頭同時(shí)連接MCU

2017-10-19 09:11:23

在調(diào)試MCU 的SPI 接口時(shí),偶爾發(fā)現(xiàn)通信不成功的情況,為了找出問題原因,使用MI1062 抓取了數(shù)字信號(hào)和模擬信號(hào)進(jìn)行對(duì)比分析。 1、邏輯分析儀測試信號(hào)邏輯 啟動(dòng)MI1062 邏輯分析儀功能

2017-07-27 09:51:02

第10章 SignalTapⅡ嵌入式邏輯分析儀的使用 96頁 1.9M

2016-09-27 08:48:04

讓嵌入式研發(fā)工程師人手一機(jī)邏輯分析儀———專訪***孕龍科技儀器事業(yè)處業(yè)務(wù)部業(yè)務(wù)經(jīng)理鄭銘國

2010-04-26 14:32:24

公司10年前太克的已經(jīng)報(bào)廢,因?yàn)榇蠹叶紤械勉^現(xiàn)在的 FPGA 都有內(nèi)建軟核邏輯分析儀,每次測都上百點(diǎn)...16~32點(diǎn)邏輯分析儀能做什么? FPGA 運(yùn)行都破百 MHZ..不知道號(hào)稱n百M(fèi)HZ邏輯分析儀抓的到嗎?

2019-09-04 23:50:44

基于LabVIEW的嵌入式瞬態(tài)記錄分析儀的軟件如何去設(shè)計(jì)?

2021-04-27 06:05:42

請(qǐng)問一下怎么實(shí)現(xiàn)嵌入式電網(wǎng)分析儀中雙CPU間的通信?

2021-06-03 06:10:11

一種基于FPGA技術(shù)的虛擬邏輯分析儀的研究與實(shí)現(xiàn):邏輯分析儀的現(xiàn)狀" 發(fā)展趨勢及研制虛擬邏輯分析儀的必要性, 論述了基于FPGA技術(shù)的虛擬邏輯分析儀的設(shè)計(jì)方案及具體實(shí)現(xiàn)方法,介紹

2008-11-27 13:13:04 29

29 本文介紹了可編程邏輯器件開發(fā)工具Quartus II 中SingalTap II 嵌入式邏輯分析器的使用,并給出一個(gè)具體的設(shè)計(jì)實(shí)例,詳細(xì)介紹使用SignalTap II對(duì)FPGA調(diào)試的具體方法和步驟。關(guān)鍵字 : S

2009-11-01 14:49:39 45

45 邏輯分析儀入門手冊(cè):與許多電子測試和測量工具一樣,邏輯分析儀是一種針對(duì)特定類型問題的解決方案。它是一種通用工具,可以幫助您調(diào)試數(shù)字硬件、檢驗(yàn)設(shè)計(jì)和調(diào)試嵌入式軟件

2009-11-15 22:34:18 64

64 文章介紹了如何在Cyclone 芯片中嵌入和定制NiosⅡ軟處理器,嵌入觸發(fā)模塊、數(shù)字鎖相環(huán)和數(shù)據(jù)緩存模塊,從而設(shè)計(jì)高速邏輯分析儀。分析儀能夠采集速率高達(dá)50MBs 的8 路邏輯信號(hào),并

2010-01-20 15:45:32 15

15 TLA邏輯分析儀原理與應(yīng)用 -硬件調(diào)試基礎(chǔ)教程。

2010-08-05 15:08:02 49

49 使用邏輯分析儀調(diào)試定時(shí)問題

在今天的數(shù)字世界, 嵌入式系統(tǒng)比以往任何時(shí)候都更為復(fù)雜。 使用速度更快、 功耗更

2010-08-06 07:49:46 24

24 介紹了大規(guī)模可編程邏輯器件開發(fā)工具Quartus II中嵌入式邏輯分析儀Signal Tap II的基本用法;并結(jié)合一個(gè)具體的應(yīng)用實(shí)例來說明了Signal Tap II在系統(tǒng)硬件調(diào)試過程中的優(yōu)點(diǎn)及其強(qiáng)大功能

2010-08-06 16:35:44 28

28 最新嵌入式系統(tǒng)數(shù)字邏輯測試解決方案:TLA6000系列邏輯分析儀。

嵌入式系統(tǒng)技術(shù)、市場發(fā)展趨勢基于TLA6000的模擬、數(shù)字聯(lián)合測試系統(tǒng)動(dòng)態(tài)FPGA內(nèi)部信號(hào)完整性測試方案

2010-12-17 11:50:12 40

40 摘 要 :本文介紹了可編程邏輯器件開發(fā)工具Quartus II 中SingalTap II 嵌入式邏輯分析器的使用,并給出一個(gè)具體的設(shè)計(jì)實(shí)例,詳細(xì)介紹使用SignalTap II對(duì)FPGA調(diào)試的具體方

2009-06-20 10:42:18 1366

1366

使用邏輯分析儀調(diào)試時(shí)序問題

在今天的數(shù)字世界,嵌入式系統(tǒng)比以往任何時(shí)候都更為復(fù)雜。使用速度更快、功耗更低的設(shè)備和功能更強(qiáng)大的電路,

2009-08-26 12:09:14 1389

1389

基于NiosⅡ的嵌入式高速邏輯分析儀

由于數(shù)字信號(hào)只有高電平和低電平兩種情況,因此,用單片機(jī) (MCU)就可直接實(shí)現(xiàn)多路數(shù)字信號(hào)進(jìn)行采集和邏輯分

2009-10-06 08:25:54 700

700

邏輯分析儀自1973年問世以來,在短短幾十年的時(shí)間內(nèi)得到了迅速的發(fā)展。傳統(tǒng)邏輯分析儀利用芯片的引腳對(duì)信號(hào)采樣,并送到顯示部分對(duì)系統(tǒng)進(jìn)行分析,但對(duì)于無引腳的封裝類型,傳統(tǒng)邏輯分析儀很難有效的監(jiān)測系統(tǒng)內(nèi)部信號(hào)。而在FPGA測試中,嵌入式邏輯分析儀(ELA

2011-03-15 14:52:53 38

38 嵌入式開發(fā)調(diào)試中,開發(fā)人員的調(diào)試手段包括斷點(diǎn)、觸發(fā)和跟蹤三種。在線調(diào)試器(I(、I))與邏輯分析儀(IA)協(xié)調(diào)工作,為調(diào)試新一代嵌入式處理器的開發(fā)人員提供了上述三種調(diào)試手段。

2011-11-07 15:58:09 33

33 FPGA概述FPGA調(diào)試介紹調(diào)試挑戰(zhàn)設(shè)計(jì)流程概述■FPGA調(diào)試方法概述嵌入式邏輯分析儀外部測試設(shè)備■使用 FPGAVIEW改善外部測試設(shè)備方法■FPGA中高速O的信號(hào)完整性測試和分析

2020-09-22 17:43:21 9

9 1 推動(dòng)FPGA調(diào)試技術(shù)改變的原因 進(jìn)行硬件設(shè)計(jì)的功能調(diào)試時(shí),FPGA的再編程能力是關(guān)鍵的優(yōu)點(diǎn)。CPLD和FPGA早期使用時(shí),如果發(fā)現(xiàn)設(shè)計(jì)不能正常工作,工程師就使用“調(diào)試鉤”的方法。先將要觀察

2023-12-20 13:35:01 147

147

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論