老wu發現,很多硬件菌在設計PCB上的電源供應系統時,喜歡在各個電源軌之間加入磁珠隔離一下,據說能防止干擾。硬件菌們很喜歡加磁珠,貌似磁珠能包治百病,就好像我們覺得自己頭疼、嗓子疼,感覺自己肯定是感冒了,就要馬上嗑阿莫匹林抗生素一樣,磁珠也被硬件菌給濫用了。

磁珠這玩意雖好,但也不能貪杯喲,硬件菌在決定服用磁珠之前,老wu建議先看看下這份 Altera 公司的鐵氧體磁珠應用筆記。

這是一篇來自業界著名 FPGA 供應商 Altera 公司的FPGA 電源設計應用筆記,這份應用筆記提供了設計鐵氧體磁珠濾波器網絡來為Stratix? IV FPGA隔離共用電源軌的一些設計指南。

FPGA 技術的發展使數據速率提高到了 10 Gbps 以上。為了達到這種數據速率,FPGA 廠商一般要求提供多個隔離的數字和模擬電源層,以單獨為 FPGA 的內核,I/O,敏感的鎖相環 (PLL) 和千兆收發器模塊供電。因此,電路板上電源分配系統的復雜性大大增加。

由于電路板空間、層數以及成本預算均有限,電路板設計人員發現在這些系統限制內設計其 FPGA 電路板越來越困難。對于 Stratix IV GX 和 GT 系列千兆位收發器 FPGA 系列,一種常用的簡化電源設計的方法是,對于具有相同電壓要求的部分,能夠共用電源軌,并保持彼此之間的隔離,避免電源噪聲干擾。常用的策略是使用鐵氧體磁珠。

本應用手冊介紹了如何正確選擇磁珠以及一些設計方面的考慮,例如:anti-resonance、避免 LC 諧振效應、傳輸阻抗分析和直流IR壓降最小化,同時還要滿足去耦的目標阻抗要求。另外,還介紹了某些情況下使用 PCB 布局結構來替代鐵氧體磁珠功能的秘技。PCB 結構與鐵氧體磁珠的性能對比仿真結果,可用于評估驗證 PCB 結構濾波器網絡的效果,同時可以了解其諸多局限性。

鐵氧體磁珠的選擇

一般而言,鐵氧體磁珠分為兩類:

高Q值鐵氧體磁珠——一般用作諧振器,不得用于電源隔離電路中

低Q值鐵氧體磁珠——也稱作吸收鐵氧體磁珠,損耗較大,可構成較好的電源濾波器網絡,因為設計它們的目的是吸收高頻噪聲電流并將其以熱的形式散發掉。這種鐵氧體磁珠在寬高頻帶下具有高阻抗,從而使其成為理想的低通噪聲濾波器。

廠商一般會給出鐵氧體磁珠的阻抗-頻率曲線圖的特性,并說明額定最大直流電流和直流電阻。這取決于鐵氧體磁珠的設計和所用材料,阻抗曲線圖中的幅度也在一個較寬的頻譜范圍急劇變化,從而對正確選擇鐵氧體磁珠帶來麻煩。

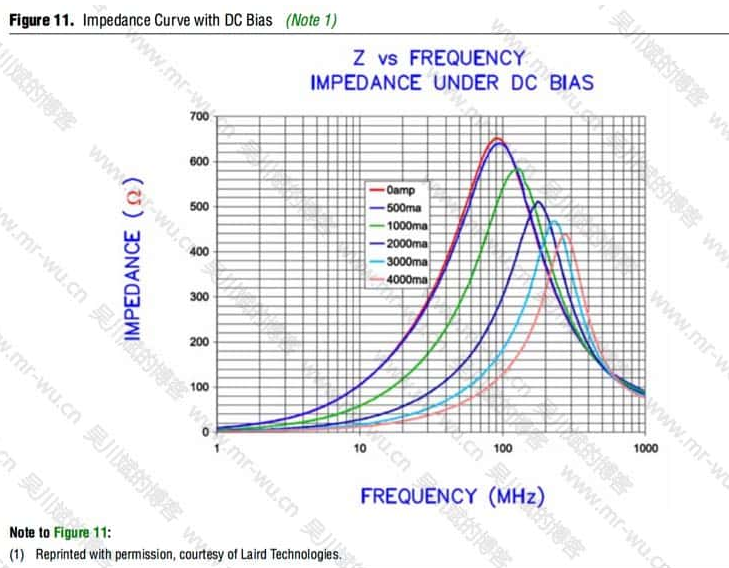

圖 1 顯示了 1 GHz 頻率范圍內 5 條交錯在一起的鐵氧體磁珠阻抗曲線的例子,旨在對比可用于電源噪聲濾波的各種低Q值鐵氧體磁珠的性能情況。

鐵氧體磁珠建模與仿真

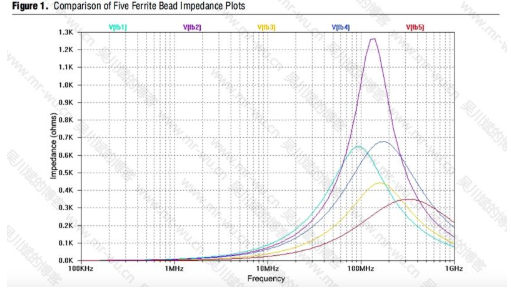

鐵氧體磁珠廠商通常提供其器件的等效 SPICE 電路模型,以用于系統仿真。當無法從廠商那里獲得鐵氧體磁珠模型的情況下,可以將鐵氧體磁珠建模成一個由 R、L和 C 元件組成的簡單網絡,如圖 2 所示

盡管該模型為 first-order approximation,但是您仍然可以將其有效地用于 sub-GHz 的仿真。

Rbead 和?Lbead 為鐵氧體磁珠的直流電阻和有效電感。

Cpar 和?Rpar 為鐵氧體磁珠相關的并聯電容和電阻。

低頻條件下,Cpar 為開路,而?Lbead 為短路,從而只有?Rbead 作為鐵氧體磁珠的直流電阻。隨著的頻率增加,Lbead 的阻抗開始隨頻率 (jωLbead) 線性上升,而?Cpar 的阻抗隨頻率 (1/jωCpar) 反比例下降。鐵氧體磁珠的阻抗-頻率曲線圖的上升斜率主要由?Lbead 的電感決定。

從某個高頻點開始,Cpar 的阻抗開始占主導,而鐵氧體磁珠的阻抗開始下降,從而降低其電感效應。這種情況下,阻抗-頻率曲線圖的下降斜率主要由鐵氧體磁珠的寄生電容?Cpar 決定。Rpar 有助于減緩鐵氧體磁珠的 Q 因子。然而,過大的?Rpar 和?Cpar 值會增加鐵氧體磁珠的 Q 因子,并降低其有效帶寬。形成高Q鐵氧體磁珠,導致電源分配網絡 (PDN)上出現不期望的瞬態振鈴響應。

要想觀察這些參數對鐵氧體磁珠頻率響應產生的影響,您可以使用 SPICE 來仿真用于隔離的鐵氧體磁珠的交流響應。圖 2(右)顯示了用于獲取一個鐵氧體磁珠樣本的交流響應的 SPICE 電路設置, 其中DC電阻為 0.15Ω,有效電感為 54nH,并聯電容和電阻分別為 178fF 和 70Ω。

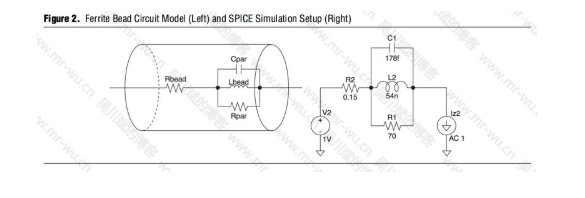

圖 3 顯示了 SPICE 中,施加一個 1V 電源和 1A AC電流負載,100 Hz 到 1 GHz范圍內掃描的交流分析,得到的該鐵氧體磁珠的特征阻抗-頻率曲線圖。在一些廠商沒有提供 SPICE 模型的情況下,通過在模型中單獨改變每一個 R、L 和 C 元件,可用曲線擬合方法來近似描述某個特定的鐵氧體磁珠。

Stratix IV GX 設計實例

對許多應用而言,高速時鐘、數據以及其它 I/O 開關速率可達到數百兆赫到幾千兆赫。每一個開關信號相應的基本頻率和諧波很容易污染敏感的電源層面,從而導致電壓紋波和輸出抖動增高,特別是在它們與其它噪聲較大的數字電源層共用時。例如,在 Stratix IV GX 器件中,0.9V VCC核心電壓被用于向 FPGA內核中的的數字邏輯單元 (LE)、存儲器單元以及 DSP 模塊等供電,這些模塊有很大噪聲。另一方面,0.9V VCCD_PLL 被用于向產生時鐘倍頻且對噪聲更敏感的 PLL 供電。盡管在 PCB 上將 VCC 與 VCCD_PLL 電源層合并很簡單(由單個電源穩壓器供電),但是這樣做會使內核耦合噪聲對 PLL 性能產生負面影響。

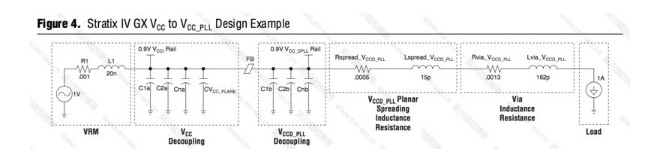

圖 4 顯示了 Stratix IV EP4SGX230KF40 器件的一個設計實例,其使用一個鐵氧體磁珠隔離 VCC 和 VCCD_PLL。本例所選用的鐵氧體磁珠為萊爾德科技 (Laird Technologies) 的 LI0805H121R-10。

VCC 電源層去耦(由 C1a 和 C2a 到 Can 表示)設計是通過 Altera 的 PowerPlay 早期功耗估算器 (EPE) 和 PDN 去耦工具實現從直流到25 MHz的頻帶內達到 9 mΩ 的阻抗目標。同樣地,VCCD_PLL 去耦(由 C1b 和 C2b 到 Cnb 表示)的目的是,利用相同的目標阻抗方法在至少 70 MHz頻帶內達到 0.45Ω 目標阻抗。

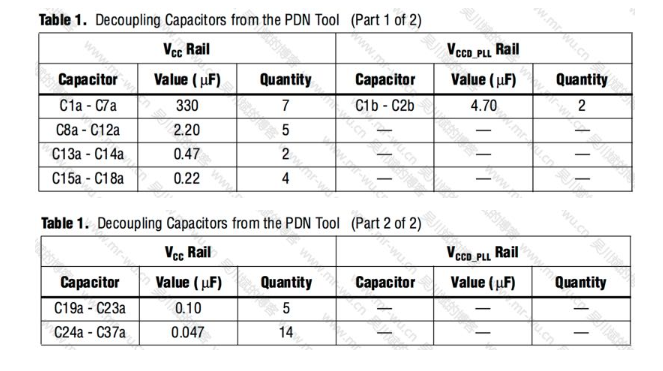

表 1 對通過PDN 去耦工具得出的每個電源層面要達到各自阻抗目標所需的去耦電容進行了總結。該 PDN 工具估算得到的平面擴展電阻和電感以及 BGA 過孔電阻和電感,也都包括在 SPICE 界面中,旨在給出一個擴展至器件 BGA 焊球的完整 PDN 狀況。

反諧振 (Anti-Resonance)

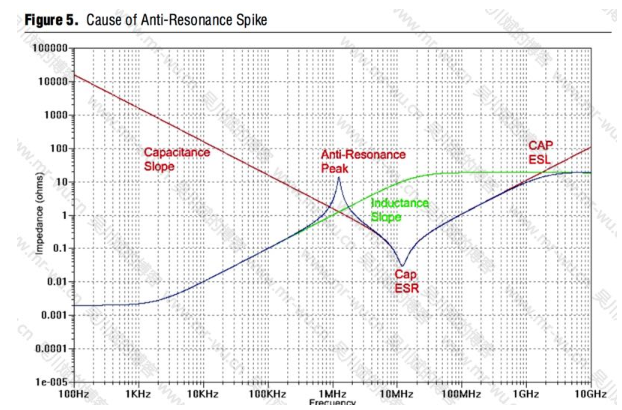

使用鐵氧體磁珠時,注意可能出現的反諧振峰值,其可能會導致超出目標阻抗限制的阻抗曲線。下降的電容特性斜率與鐵氧體磁珠的上升的電感特性斜率交錯在一起時,便會出現這些反諧振峰值,如圖 5 所示。

如果目標阻抗較低,這些峰值極易超出目標阻抗限制。使用 SPICE 或者類似的電路仿真器來確保這些反諧振峰值不會超出目標阻抗。

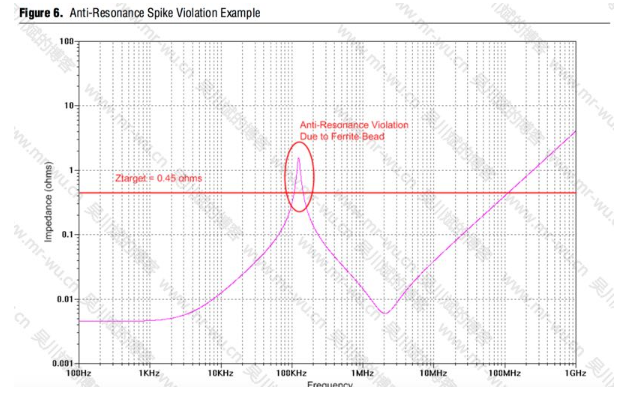

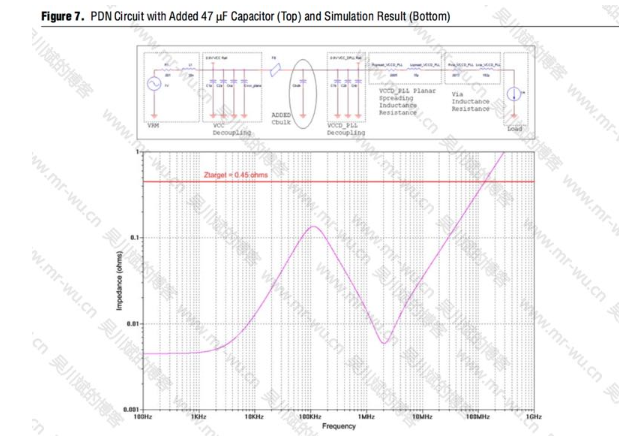

就上述 Stratix IV GX VCC 到 VCCD_PLL 隔離例的子而言,PDN 工具沒有體現出鐵氧體磁珠的效應。因此,SPICE 被用于驗證使用鐵氧體磁珠后是否會引入不期望的反諧振從而改變 PDN 特性曲線。

在SPICE中,將一個穩壓器源建模成一個簡單的電阻-電感串聯網絡,驅動一個 1A 的負載,并將其運用到建模的 PDN 電路上。在100Hz 到 1GHz頻譜范圍內做AC掃描來仿真該電路,以獲得以 Ω 為單位的去耦網絡阻抗曲線圖。如圖 6 所示,PDN 工具估算得到的 VCCD_PLL 電源的去耦電容器以及選用的萊爾德科技 LI0805H121R-10 鐵氧體磁珠一起在124 KHz 處會引起一個約為 1.5Ω 的嚴重的反諧振峰值。因其超出了 0.45Ω 的 VCCD_PLL 阻抗目標,必須解決該問題。

要想消除這種低頻反諧振峰值,可為 VCCD_PLL 增加一個大容值的Bulk去耦電容,如圖 7(頂部)所示。圖 7(底部)顯示了為 VCCD_PLL 電源層增加一個 47μF 大電容后的 PDN 曲線圖。該增加的Bulk去耦電容有助于減輕這種反諧振超標。

LC 諧振振蕩

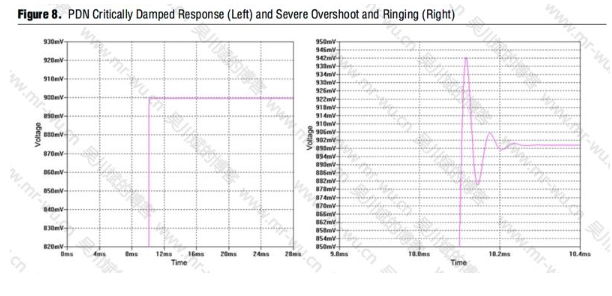

使用鐵氧體磁珠的另一個問題是 LC 諧振振蕩。只要您在 PDN 電路中使用電感和電容,存儲于電感和電容中的能量就會在這兩種能量存儲元件之間來回轉移,從而可能導致不需要的電路振蕩。這種負面影響表現為在時域的電壓過沖甚至電壓振鈴。

使用一個具有瞬態分析的 SPICE 仿真器或者類似工具,來對您的設計進行檢查,看是否所有的過沖或振鈴都得到了較好的抑制并且在容許限制范圍內。前面的 Stratix IV GX VCC 到 VCCD_PLL 例子中,萊爾德科技的 LI0805H121R-10 鐵氧體磁珠沒有引起電壓過沖或振鈴,如圖 8(左)所示。如果出現過沖或振鈴,對于 0.9V VCCD_PLL 電源而言,請確保其在 ±30 mV 操作規范以內。通常情況下,如果鐵氧體磁珠的電感非常高,如圖 8(右)的假設情況所示,則過沖或振鈴會更加嚴重,從而導致器件的失效或者錯誤運行。如果出現嚴重的過沖或振鈴,請選擇更低電感值的鐵氧體磁珠。

傳輸阻抗

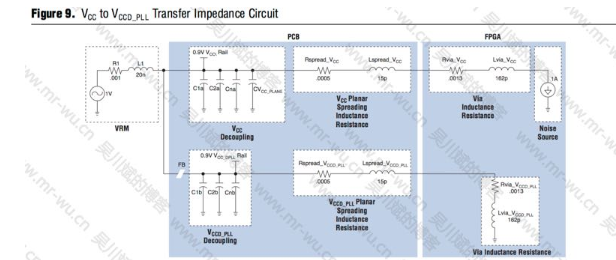

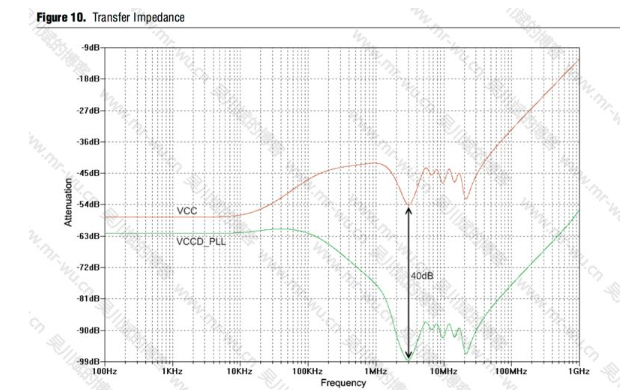

評估電路噪聲抗擾度的一種常用方法是分析其傳輸阻抗。要確定上述例子 VCC 到 VCCD_PLL 隔離的傳輸阻抗,您可以從鐵氧體磁珠的 VCC 端來仿真 PDN 電路,通過加上1A的電流源,以對 FPGA 器件中來自 VCC 電源的模擬噪聲進行評估,如圖 9 所示。

圖 10 顯示了VCC電源層鐵氧體磁珠前和隔離的VCCD_PLL電源在FPGA 器件 BGA 球柵上的最終傳輸阻抗。由于鐵氧體磁珠和 VCCD_PLL去耦網絡的作用,在3 MHz以上頻段上,VCCD_PLL 比 VCC 低大約 40 dB。

盡管該應用手冊給出的例子均專門針對 VCCD_PLL 電源層面,但是 Stratix IV GX 和 GT 器件的其它一些電源,例如:VCCL_GXB 、VCCAUX 和 VCCA 等,也都可以受益于文中描述的相同隔離技術和分析方法。

DC 電流和 IR 壓降考慮因素

鐵氧體磁珠可通過的電流量由其產品說明書中規定的最大額定 DC 電流決定。超出該最大額定電流就會損壞鐵氧體磁珠。但是,甚至低于該最大額定 DC 值的電流也會導致鐵氧體磁珠極大地降低其效果,因為鐵氧體磁珠的芯材可能會變得飽和。

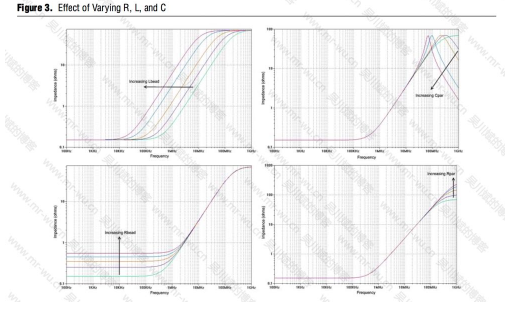

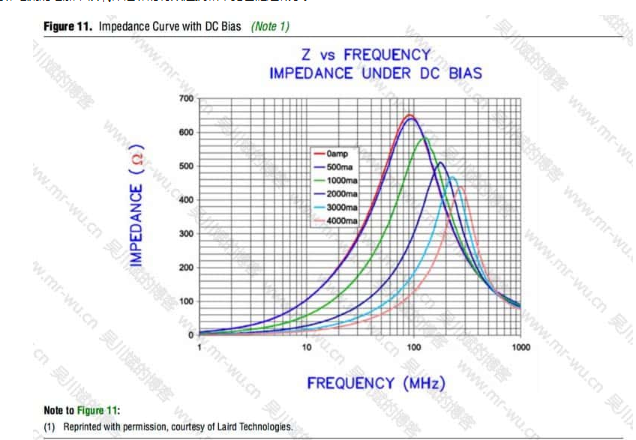

圖 11 顯示了改變 DC 電流偏置條件下鐵氧體磁珠的阻抗-頻率曲線例子。隨著通過鐵氧體磁珠電流的增加,鐵氧體磁珠的有效阻抗和帶寬也隨之減小。

為了避免內核飽和與鐵氧體磁珠性能下降,請選擇額定 DC 電流兩倍于目標電源所需電流的鐵氧體磁珠。另外,選擇一個低 DC 電阻鐵氧體磁珠來使相關 DC IR 壓降最小化。確定所有壓降都不會使目標電源降至 FPGA 建議操作環境以下,具體規范見器件產品說明書。

PCB 結構

使用磁珠的另一種方法是構建一個小電感 PCB 布局結構,來連接兩個隔離電源層。這種方法要求精確的建模并提取PCB 結構相關的 DC 電阻和 AC 環路電感,并利用 SPICE 仿真來檢查結構濾波器性能,以代替鐵氧體磁珠。DC 電阻決定了由于該結構走線長度帶來的壓降。AC 環路電感有助于提供兩個互聯電源層的隔離。

在下列例子中,Altera 使用 Ansoft Q3D Extraction 軟件來建模、評估并調節幾種 PCB 結構,其對隔離 Stratix IV GX VCC 和 VCCD_PLL 電源層面很有效。利用 Q3D,可抽取出每種結構的 DC 電阻和 AC 環路電感。之后,在 SPICE 中對這些值進行重新仿真,以獲得與前面鐵氧體磁珠性能相對比的結構性能。

例子1:直線走線結構

在圖 12 所示直線走線結構中,一條 20 mil 寬、1 oz 銅厚的電源走線被用于代替鐵氧體磁珠來連接考慮中的兩個電源層。采用這種結構的走線可以承載約 3.7A 的電流。您必須設計走線,來處理期望的電流負載。直接影響走線電感的參數主要是走線的長度、距離參考層的高度,以及走線下方挖空 (cutout) 面積的大小。

一般而言,走線長度越長,走線離參考層越遠,或者挖空面積越大,走線電感越大。因為這些因素會帶來更大的電流回流面積。但是,每一個參數過大都會占用寶貴的電路板空間。更好的拓撲結構是使用一種盤繞走線方法。

示例 2:盤繞走線結構

為了盡可能增大走線環路電感同時最小化電路板空間使用,可使用一種盤繞走線結構,如圖 13 所示。 因為繞組中的電流在繞組的并聯走線部分總是以相同方向流動,因此沒有電流抵消發生,并且在一個較小區域實現最大電感。但是,使用盤繞結構要求一個逃逸過孔(逃逸過孔這個名字比較奇怪,老wu不解釋,看圖你就會秒懂),以允許走線能夠走到另一個層。正因如此,需考慮過孔的電流承載能力。一般而言,一個 1 mil 孔壁厚度、12 mil 直徑的過孔可通過大約 2.5A 的電流。

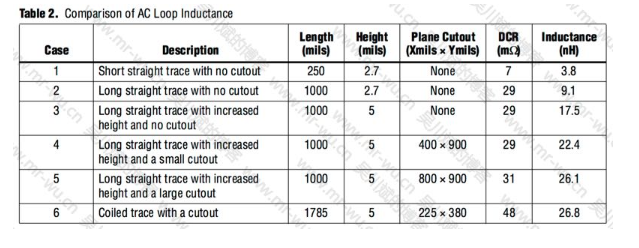

表 2 列舉了通過 Q3D 得到的不同直線及盤繞走線長度、距參考層高度以及層挖空面積大小情況下對 DC 電阻和走線電感的影響。在給定走線寬度條件下,DC 電阻主要取決于走線的長度,如表 2 所示。

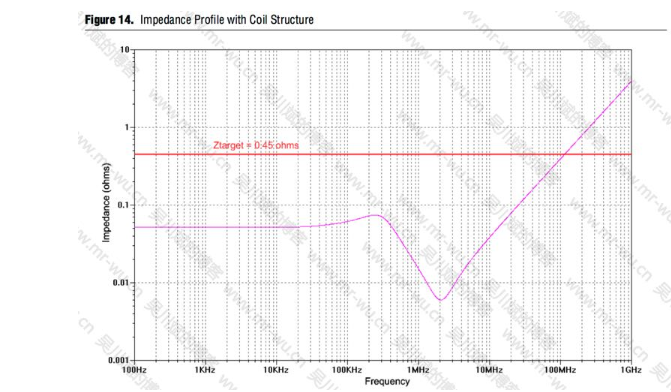

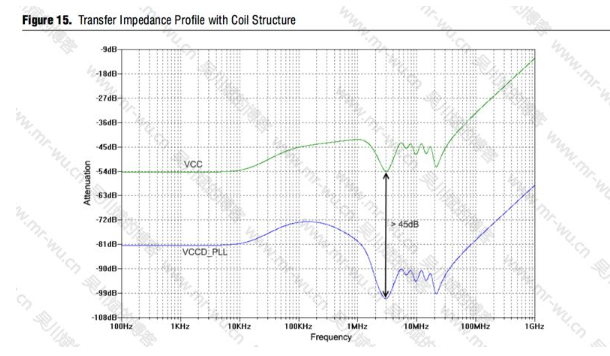

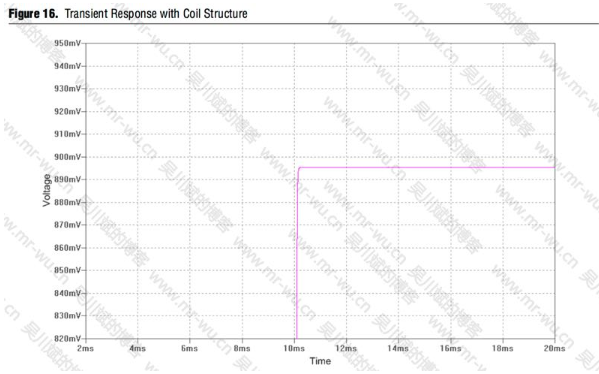

仿真結果

使用 Q3D 從盤繞走線結構提取的 48 mΩ DC 電阻和 26.8 nH AC 環路電感,并在前面 VCC 到 VCCD_PLL SPICE 例子中再次仿真這些值,可得到下列阻抗曲線(請參見圖 14)、傳輸阻抗(請參見圖 15)和瞬態響應(請參見圖 16)的結果。這三幅圖表明,如果結構的 DC 壓降保持在產品說明書規定的建議器件操作環境范圍內,則您可以使用盤繞走線PCB 布局結構來代替鐵氧體磁珠。 (老wu注 一個磁珠多少錢,相應的通過繞線產生的等效于磁珠的走線的多層板pcb增加的成本多少錢?真的有人會用這種糾結的用法嗎?除非你找不到同等規格的磁珠咯)

EMC 標準

但要注意的是,這種結構會成為強輻射源,其可能會影響聯邦通信委員會 (EMC) 和其它國際監管機構頒布的電磁標準 (EMC) 規定。把這種結構放在兩個地層之間,并用過孔聯結在一起,可幫助屏蔽輻射。Altera 還沒有對這些結構進行額外的 EMC 標準仿真和測試,其超出了本應用手冊的范圍。

設計建議

Altera 對您的設計提出如下建議:

選用一個鐵氧體磁珠或設計 PCB 濾波結構,使其可以承載去耦電源所需的電流負載。

為了避免內核飽和,選擇一個額定電流至少兩倍于目標電源預計電流的鐵氧體磁珠。

需最小化鐵氧體磁珠或 PCB 結構的 DC 電阻,以減少 DC IR 壓降

確定所有壓降都沒有導致目標電源低于器件的建議操作環境。

使用 SPICE 或其它類似工具,以確保所有鐵氧體磁珠或 PCB 電感結構帶來的反諧振峰值均沒有超出目標阻抗限制。

如果出現反諧振超標,向電源層添加大的Bulk去耦電容來減少或消除峰值。

使用 SPICE 或其它類似工具對有過大電壓過沖或振鈴的 PDN 電路進行瞬態響應分析,這種過沖或振鈴可能會超出器件建議操作環境。

使用 SPICE 或其它類似工具對被隔離的電源相對于未濾波的父電源層的傳輸阻抗進行分析,以獲得充分衰減。

結論

Stratix IV GX 和 GT 系列高性能 FPGA 要求多個電源為器件內各種電路模塊供電。為了讓器件達到最大額定性能并具有最低抖動,某些敏感電源層要求非常潔凈的電源。要在系統設計限制范圍內滿足這些電源要求,您可以將鐵氧體磁珠或自定義 PCB 結構用作濾波器元件來隔離一些共用電源。本應用手冊介紹了如何選擇正確的鐵氧體磁珠以及如何設計 PCB 結構,來滿足基于 Stratix IV GX 及 GT 的 PDN 設計的一些電源濾波器要求。

電子發燒友App

電子發燒友App

評論