初始化時存入數據。那在IP核rom中存放大量數據對FPGA有什么影響,比如我想存65536個16位的數,然后在64M或者128M的時鐘下讀出來。會不會導致FPGA速度過慢?

2013-01-10 17:19:11

,因為FPGA之間的高速互聯特性,也可以方便地在不同FPGA、不同FPGA板卡間部署完整的相關應用方案。成本方面,高畫質IP雖然通道數量上并不占優勢,但是帶來的bitrate的大幅降低,可以顯著降低

2019-03-08 10:47:22

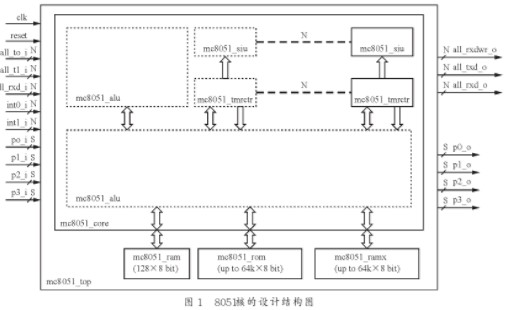

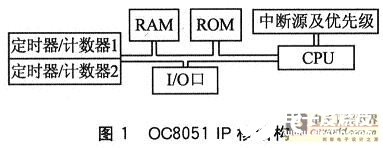

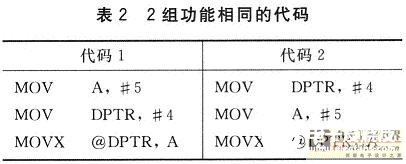

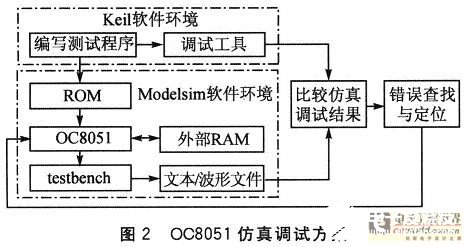

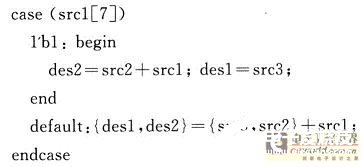

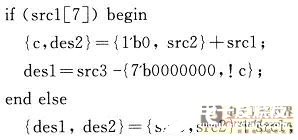

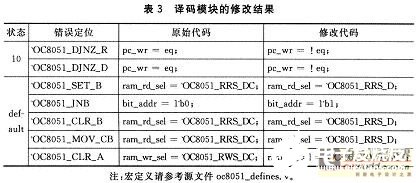

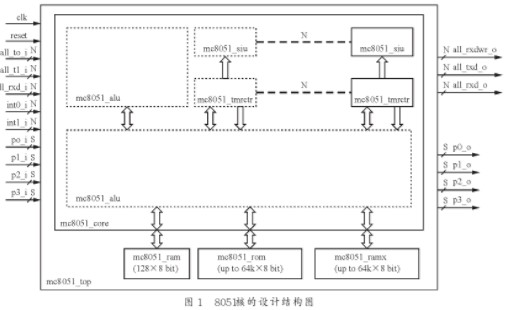

的基礎上,給出了一種仿真調試方 案;利用該方案指出了其中若干邏輯錯誤并對其進行修改,最終完成了修改后IP核的FPGA下載測試。1 OC8051結構分析OpenCores網站提供的OC8051 IP核

2012-08-11 11:41:47

II中捕捉到LA的數據為1h,LD上的數據為1h后ConfigStart寄存器置高,配置開始。配置速度測試實驗軟硬件具體方案設計完畢后,軟件在Visual C++6.0環境下實現并調試。硬件在

2020-05-14 07:00:00

;wave->all items in design。這樣就可以查看中間變量了。2.仿真帶有ip核的工程總出錯。大部分原因是因為你沒有把支撐ip核的仿真的文件添加到工程中。對于verilog來說,要把

2017-04-15 21:46:29

FPGA嵌入8051單片機 IP核編程,編寫的c語言矩陣鍵盤程序可以在stc89c54單片機上正常工作,但是下載到FPGA中8051單片機ip核的rom中,不能正常工作,求指教

2013-07-25 21:27:44

本帖最后由 jf_25420317 于 2023-11-17 11:10 編輯

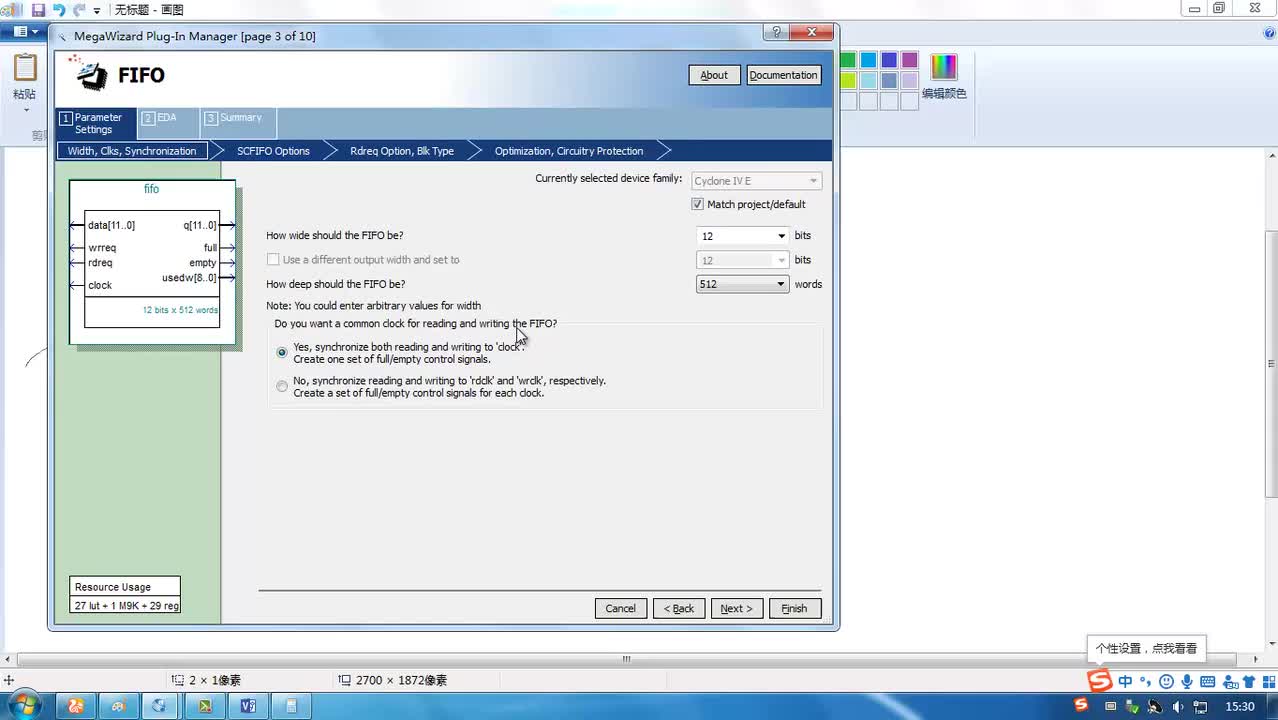

FPGA開發過程中,利用各種IP核,可以快速完成功能開發,不需要花費大量時間重復造輪子。

當我們面對使用新IP核

2023-11-17 11:09:22

哪位大神能給我發一下FPGA的8051核的完整工程文件,verilog語言的,或者教我怎么把這些文件搭建成一個工程,紅包答謝,我企鵝2052341362

2017-03-14 13:22:11

有誰知道現在國內外有哪些公司賣FPGA的圖像處理相關的IP核?

2015-04-28 21:34:24

是IP 核應用最廣泛的形式。 固核(Firm IP Core) :固核在EDA 設計領域指的是帶有平面規劃信息的網表;具體在FPGA 設計中可以看做帶有布局規劃的軟核,通常以RTL 代碼和對應具體

2018-09-03 11:03:27

我使用fpga跑一個arm的軟核,測試點亮一個led燈的程序。仿真結果與自己想要的結果是吻合的(頂層led的port是有輸出的),但是下載到fpga開發板上后,運行就沒有結果(連接頂層led的port測試沒有輸出)。請問如何去調試找出問題出在哪里?

2017-06-13 17:06:52

我調用了一個ip核 在下載到芯片中 有一個time-limited的問題 在完成ip核破解之后 還是無法解決 但是我在Google上的找到一個解決方法就是把ip核生成的v文件加到主項目文件中就是上面

2016-05-17 10:28:47

我研究了在設計中實現HDMI,DVI和Displayport的可行性。在這種設計中,FPGA將具有用于HDMI,DVI和DisplayPort的接收器,以接收來自外部源的信號。現在我不確定以下

2019-02-19 10:09:29

可以移植到不同的半導體工藝中去生產集成電路芯片。隨著CPLD/FPGA的規模越來越大,設計越來越復雜,使用IP核是一個趨勢。 本文研究了ATM流量控制的原理,并給出了一種IP核的實現方法,該IP核不僅可以用于獨立芯片,還可以作為系統的一個子模塊直接調用。

2011-09-27 11:54:25

功能也正常。現在將子板扣在VXI接口的母版上,只有在仿真模式下才正常工作,下載到FLASH之后,就不工作了,檢查發現,DDR2的IP 核local_init_done信號一直不拉高, 有沒有人遇到過類似問題,或者哪位大神幫忙分析一下原因?

2017-12-12 09:53:34

劃分為幾個主要模塊,分別介紹各個模塊的功能,用VHDL語言對其進行描述,用FPGA實現并通過了仿真驗證。該IP核具有良好的移植性,可驅動不同規模的LCD電路。 關鍵詞:LCD;驅動電路;IP 引言

2012-08-12 12:28:42

使用LabVIEW FPGA模塊中的CORDIC IP核,配置arctan(X/Y)算法,配置完成之后,IP核只有一個輸入。我參考網上VHDL CORDIC IP核,說是將XY合并了,高位X低位Y。不知道在LabVIEW中如何將兩個值X、Y合并成一個(X、Y均為定點數)。具體情況如下圖:

2019-09-10 20:07:07

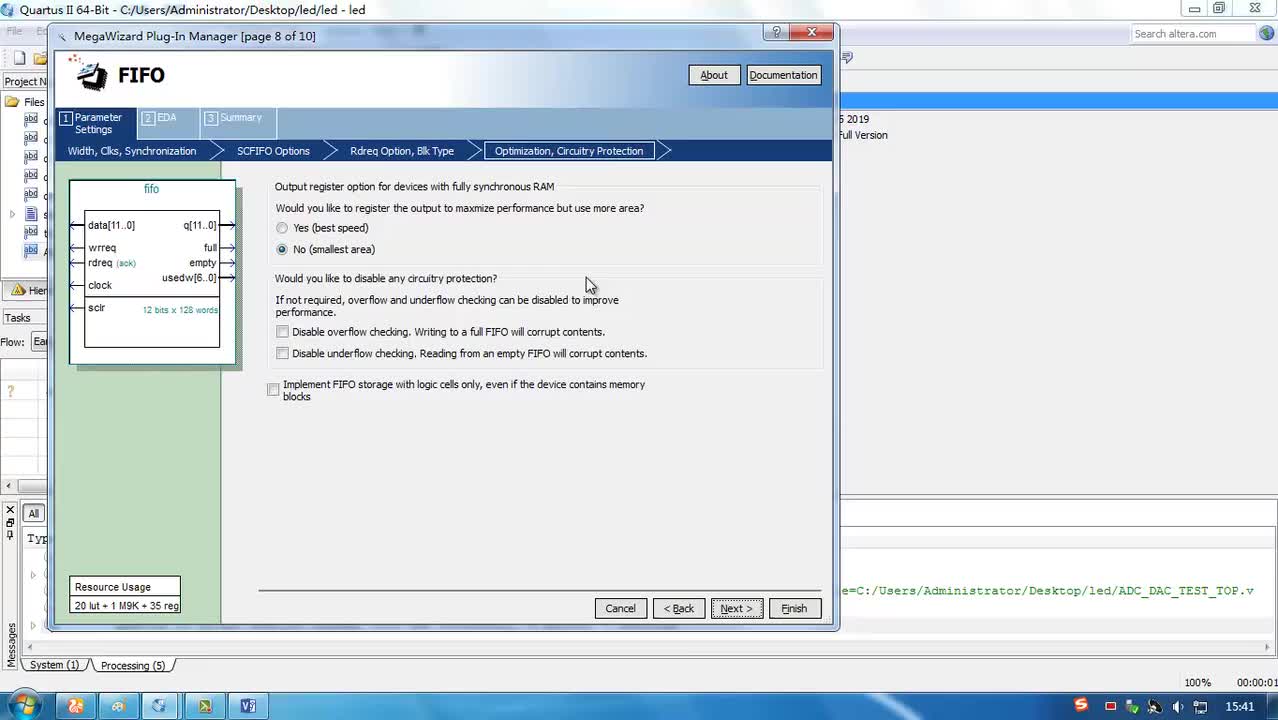

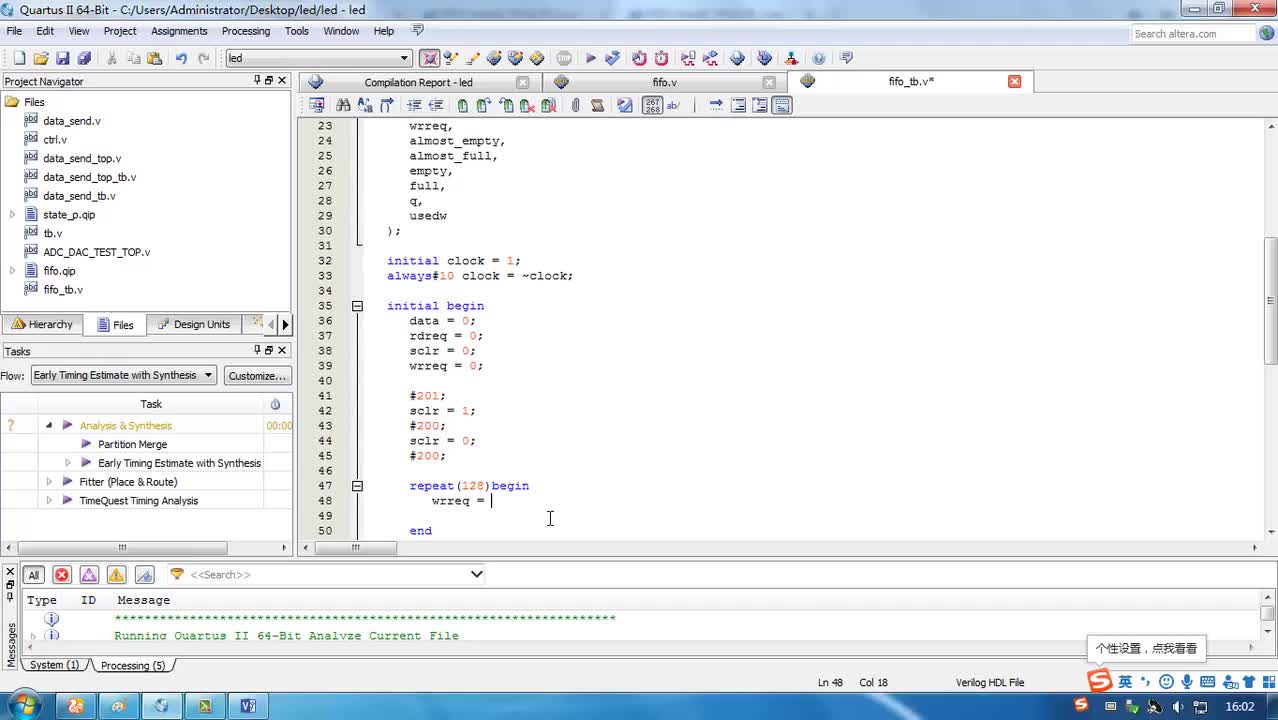

8051Core 綜合、編譯應用。包括 Quartus II軟件的基本應用,ROM、RAM 模塊的生成,8051Core 的封裝及應用測試。 附錄 A 為 MC8051 IP Core 的指令集。 在閱讀

2019-05-24 04:35:33

的SOPC系統中設計了LCD顯示驅動IP核,并下載到Cyclone系列的FPGA中,實現了對LCD的顯示驅動。

2019-08-06 08:29:14

很多人都說QUARYUSII中的IP核是收費的,不可以直接用的,其實不然,下面我以FIR濾波器的核的使用來給大家介紹IP核的使用,希望對大家有點幫助。 1.使用 (1)首先建立工程,這個就不

2019-06-03 09:09:51

Code + gcc環境編譯后,那么就可以根據以下的環境搭建實現下載及在線調試了。目錄一、軟件下載二、搭建調試鏈接三、下載配置四、調試配置五、DEBUG調試一、軟件下載OpenOCD:一個開源的片上調試器(Op

2022-01-25 08:03:30

USB_OTG_IP核中AMBA接口的設計與FPGA實現

2012-08-06 11:40:55

網上能找到的資料都是用altera的FPGA做的,有人用過xilinx FPGA搭建8051核嗎?請與我聯系

2017-06-03 14:59:23

最近在使用altera的FIR IP核做半帶濾波器,quartus ii軟件也破解了,firIP核也破解了,modelsin仿真也通過了,但是下載不了.sof文件到開發板,大家有用FIR IP核成功實現下板的經驗嗎,求大神指點呀。謝謝!

2018-05-11 16:01:15

在仿真fft ip核時 輸出信號一直為0,檢查了輸入波形,應該沒有問題,大家幫忙看看吧輸入是由rom里面的mif文件產生的信號。

2017-11-21 10:44:53

有沒有大神可以提供xilinx FPGA的FFT IP核的調用的verilog 的參考程序,最近在學習FFT的IP核的使用,但是仿真結果有問題,所以想找些參考設計,謝謝

2016-12-25 17:05:38

在較大工程中由于其局限性使用的越來越少,不推薦再學習;Verilog HDL為當今主流的設計方式;用IP核代替用戶自己設計的邏輯,可以大大縮短開發周期,提供更加有效的邏輯綜合和實現。Altera IP

2016-12-22 23:37:00

十、MC8051軟核在FPGA上的使用本教程內容力求以詳細的步驟和講解讓讀者以最快的方式學會 MC8051 IP core 的應用以及相關設計軟件的使用,并激起讀者對 SOPC 技術的興趣。本實驗

2017-02-17 19:54:23

: (1) 在工程頂層中例化mc8051核(2) 在工程頂層中例化pll(3) 對工程進行分析和綜合(4) 分配引腳(5) 編譯并生成FPGA配置文件 (6) 使用USB Blaster配置FPGA打開

2017-02-17 22:17:50

8051Core 綜合、編譯應用。包括 Quartus II軟件的基本應用,ROM、RAM 模塊的生成,8051Core 的封裝及應用測試。 附錄 A 為 MC8051 IP Core 的指令集。 在閱讀

2016-03-11 17:59:02

,手把手演示工程創建,IP核調用、Testbench編寫以及仿真驗證,讓每一個0基礎的朋友都能快速跟上節奏。另外,有一定基礎的朋友,其實也可以觀看,因為在設計中,我已經將很多的設計小技巧穿插在視頻中了。請

2015-09-22 14:06:56

內建的示波器。SignalTapⅡ的使用要新建一個仿真調試文件。SignalTapⅡ可以設定信號的觸發方式。其他請補充。另,FPGA的IP核并不是只有這幾種,從新建IP核的界面可以看到,IP核還有很多。

2016-10-11 22:24:16

摘要針對FFT算法基于FPGA實現可配置的IP核。采用基于流水線結構和快速并行算法實現了蝶形運算和4k點FFT的輸入點數、數據位寬、分解基自由配置。使用Verilog語言編寫,利用ModelSim

2019-07-03 07:56:53

在較大工程中由于其局限性使用的越來越少,不推薦再學習;Verilog HDL為當今主流的設計方式;用IP核代替用戶自己設計的邏輯,可以大大縮短開發周期,提供更加有效的邏輯綜合和實現。Altera IP

2019-03-04 06:35:13

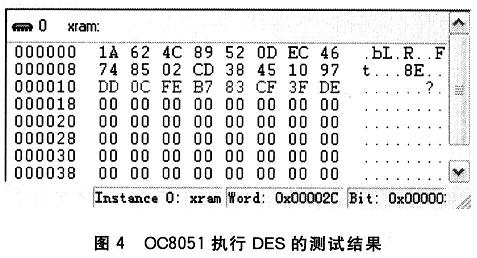

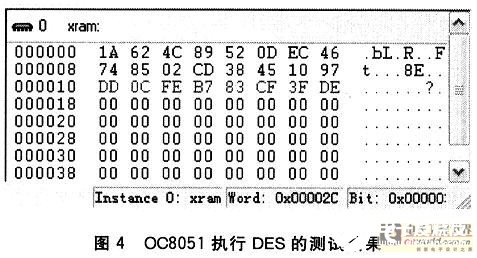

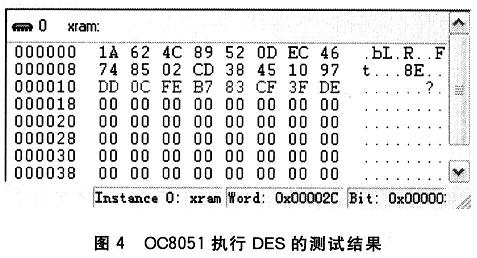

為機器碼十六進制文件。將機器碼作為RAM的初始化內容,即可進行仿真,在Modelsim軟件中觀察SoC工作時各個信號的波形。若將機器碼通過工具下載到由FPGA實現的SoC中,那么就可以讓SoC執行編寫的程序

2022-04-01 17:48:02

最近研究凌陽的61單片機,可苦于61板是用并口實現下載,在線調試。可本人用的是本子并沒有并口,每次都找臺機下載是件非常的不方便。 于是在網上找了下凌陽單片機用USB實現下載的原理,可網上資料

2021-12-02 06:35:18

和朋友開發了幾個基于 FPGA 的高速存儲 IP 核,考慮到工業相機等應用場合需要有文件系統以方便做數據管理,所以將 NVMe 和 exFAT 兩大IP核集成一起,可以實現將數據寫入SSD后,拔下

2022-06-03 11:35:06

基于FPGA中8051 IP CORE 的數字電子鐘設計求大神指導啊啊啊!

2015-05-05 22:49:09

基于FPGA的IP核8051上實現TCPIP的設計

2012-08-06 12:18:28

我畢業設計要做一個基于FPGA的IP核的DDS信號發生器,但是我不會用DDS的IP核,有沒有好人能發我一份資料如何用IP核的呀。我的瀏覽器下載不了網站上的資料,所以只能發帖求幫忙了。

2015-03-10 11:46:40

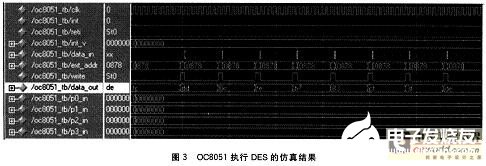

受到業內人士的青睞。本文在分析OpenCores網站提供的一款OC8051IP核的基礎上,給出了一種仿真調試方案;利用該方案指出了其中若干邏輯錯誤并對其進行修改,最終完成了修改后IP核的FPGA下載測試。

2019-07-04 06:02:19

FFT IP核進行運算,輸出FFT結果的實部和虛部分別存儲在fft_result_real.txt和fft_result_image.txt文本中(仿真測試結果位于at7_img_ex05

2019-08-10 14:30:03

取出下一條指令。圖3 取指令電路5、匯編匯編程序是為了調試軟核而開發的,手工編寫機器碼很容易出錯并且工作量很大。在調試過程中修改指令集時,匯編程序也要作相應的修改。所以要求編譯器的結構簡單性能可靠,在

2021-07-11 08:00:01

此提供了新的解決方案。IP核(IP Core)是具有特定電路功能的硬件描述語言程序,可較方便地進行修改和定制,以提高設計效率[3]。本文研究了基于FPGA的數據采集控制器IP 核的設計方案和實現方法,該IP核既可以應用在獨立IC芯片上,還可作為合成系統的子模塊直接調用,實現IP核的復用。

2019-07-09 07:23:09

核的分類和特點是什么?基于IP核的FPGA設計方法是什么?

2021-05-08 07:07:01

實現的RTL級設計,與具體實現工藝無關,相比于固核和硬核具有較大的靈活性,在FPGA中定制PCI接口軟核實現PCI接口控制具有明顯的優勢:可以在單片FPGA中同時完成PCI接口和用戶邏輯的設計,縮減成

2018-12-04 10:35:21

【摘要】:Viterbi譯碼器在通信系統中應用非常普遍,針對采用DSP只能進行相對較低速率的Vit-erbi譯碼的問題,人們開始采用FPGA實現高速率Viterbi譯碼。本文首先簡單描述了

2010-04-26 16:08:39

工具,經面向硬件電路的仿真驗證,本文的方法可實現OC-48接口(2.5Gb/s)上線速分組的IP碎片重組,并具有硬件開銷小,可擴展性好的特點。關鍵詞: IP碎片;FPGA;RLDRAM控制器;最大傳輸

2008-10-07 11:00:19

設計重用中的關鍵技術。如何保證IP核的高測試覆蓋率,如何保證IP核在集成到SoC中后的可測試性.是該階段分析的主要目標。所以在IP核實現之前.要檢查IP核設計中是否違反了可測性設計規則; 低功耗分析

2021-09-01 19:32:45

結構相同,采用CMOS工藝,因而常用80C51系列來指代所有具有8051指令系統的單片機。在80C51系列中,OC8051以架構清晰、取指帶寬大、時鐘效率高等諸多優點受到業內人士的青睞。

2019-08-13 07:34:07

(IntellectualProperty)核。IP核由相應領域的專業人員設計,并經反復驗證。IP核的擁有者可通過出售IP獲取利潤。利用IP核,設計者只需做很少設計就可實現所需系統。基于IP核的模塊化設計可縮短設計周期,提高設計質量。現場

2019-09-03 07:44:22

信號,所有的信號都是在時鐘上升沿采樣,是完全的同步設計。OCP接口信號包括數據信號、邊帶信號和測試信號。數據信號又分為基本信號、簡單擴展信號、猝發信號和多線程擴展信號。所有IP核都需要基本數據信號中

2018-12-11 11:07:21

結構相同,采用CMOS工藝,因而常用80C51系列來指代所有具有8051指令系統的單片機。在80C51系列中,OC8051以架構清晰、取指帶寬大、時鐘效率高等諸多優點受到業內人士的青睞。

2019-08-13 06:10:46

本文在分析OpenCores網站提供的一款OC8051IP核的基礎上,給出了一種仿真調試方案;利用該方案指出了其中若干邏輯錯誤并對其進行修改,最終完成了修改后IP核的FPGA下載測試。

2021-05-08 06:22:32

我的目標是實現一個給定的C算法是一個FPGA。所以,我最近得到了一個Zedboard,目標是實現該算法是PL部分(理想情況下PS中的頂級內容)。我在FPGA領域和編寫VHDL / Verilog方面

2020-03-24 08:37:03

怎么才能在嵌入FPGA的IP核8051上實現TCP/IP的設計?

2021-04-29 06:51:27

的其它設計部分盡量不相關。為了滿足上述的要求, 在FPGA中嵌入一個比較理想的選擇, 而這個即通用又控制簡單的IP核最好選擇8051微處理器。

2019-08-26 06:27:15

在EDA軟件中如何實現IP保護?在FPGA中如何實現IP保護?

2021-04-29 06:06:18

我在論壇下了8051IP核源代碼,他是每個模塊的代碼。怎么把它綜合到一個文件。弄成下圖的樣子

2015-04-24 15:15:18

中用測試腳本的形式,將matlab生成的1000個點cos數據time_domain_cos.txt文本導入,送給FFT IP核進行運算,輸出FFT結果的實部和虛部分別存儲在

2020-01-07 09:33:53

* b = 56。行為仿真驗證.png (11.39 KB, 下載次數: 0)下載附件昨天 11:35 上傳框圖(Block Design)中調用IP核這里舉一個簡單的例子,通過調用乘法器IP核,產生

2018-05-16 11:42:55

基于RTD2271CW開發一款產品,datasheet中描述包含DW8051核,有哪位朋友知道市面上的C8051仿真器(比如EC5)是否可用于程序的仿真調試,和仿真器具體是怎么連接的,這個datasheet太坑人,竟然連個典型連接電路也沒有。

2019-10-08 07:04:32

(Intellectual Property)核。IP核由相應領域的專業人員設計,并經反復驗證。IP核的擁有者可通過出售IP獲取利潤。利用IP核,設計者只需做很少設計就可實現所需系統。基于IP核的模塊化設計可縮短

2019-07-29 08:33:45

USB-Blaster的特性: 支持USB Blaster下載仿真調試,通過計算機的USB接口可對Altera的FPGA/CPLD以及配置芯片進行編程、調試等操作

2022-07-27 10:31:29

8051系列單機編輯調試仿真器(8051模擬器)

2009-08-05 08:21:02 177

177 在FPGA上對OC8051IP核的修改與測試

引 言

20世紀80年代初,Intel公司推出了MCS-51單片機,隨后Intel以專利轉讓的形式把8051內核發布給許多半導體廠家,從而出

2010-01-07 11:23:57 1585

1585

文中在FPGA芯片中嵌入MC8051 IP Core,作為控制核心,利用Verilog HDL語言進行編程,設計了以MC8051 IPCore為核心的控制模塊、計數模塊、鎖存模塊和LCD顯示模塊等模塊電路,采用等精度測量法

2013-01-07 11:17:31 4566

4566

MC8051_IP核簡單指令的仿真步驟。

2016-05-06 11:47:41 0

0 在FPGA中植入8051后, 還可在上面實現簡單的TCP/IP協議, 以支持遠程訪問或進行遠程調試, 這只是在嵌入FPGA的8051上的一個應用。為了保證用戶能夠對8051實現不同的控制操作,設計時

2019-08-01 08:01:00 1229

1229

介紹了在大型工業模擬仿真系統中,利用FPGA和軟IP核實現數據采集及收發控制的方案,并對其進行設計實現。重點闡述了在發送指令和采集接收兩種數據流模式下.該IP核的控制處理邏輯及工作狀態機的設計及實現

2018-11-07 11:14:19 20

20 在FPGA中植入8051后, 還可在上面實現簡單的TCP/IP協議, 以支持遠程訪問或進行遠程調試, 這只是在嵌入FPGA的8051上的一個應用。為了保證用戶能夠對8051實現不同的控制操作,設計時

2020-12-31 10:55:00 1186

1186

核的不同模塊進行實體/塊的仿真。前文回顧如何測試與驗證復雜的FPGA設計(1)——面向實體或塊的仿真在本篇文章中,我們將介紹如何在虹科IP核中執行面向全局的仿真,而這也是測

2022-06-15 17:31:20 389

389

電子發燒友App

電子發燒友App

評論