作者:胡修林;席向濤;張蘊玉

介紹一種在嵌放式系統中使用微處理器被動串行配置方式實現對FPGA配置的方案,將系統程序及配置文件存在系統Flash中,利用微處理器的I/O口產生配置時序,省去配置器件;討論FPGA的各種配置方式及各種配置文件的使用;詳述被動串行配置的時序及在嵌入式系統中實現的軟硬件設計;說明本方案的優越性及應用前景。

隨著信息時代的到來,嵌入式系統成為繼IT網絡技術之后又一個新的技術發展方向。嵌入式系統以其功能強、體積小、功耗低、可靠性高以及面向行業應用的突出特征,廣泛應用于各個領域。

現場可編程門陣列FPGA(Field Programmable Gate Array)是一種高密度可編程邏輯器件,其邏輯功能的實現是通過把設計生成的數據文件配置進芯片內部的靜態配置數據存儲器(SRAM)來完成的,具有可重復編程性,可以靈活實現各種邏輯功能。FPGA的這種特性使其在現代電子系統設計中得到了廣泛應用。基于SRAM工藝的FPGA是易失性的,系統掉電以后其內部配置數據將丟失,因此需要外接ROM保存其配置數據。FPGA的配置是有時序要求的,如果FPGA本身不能控制配置時序,就需要有外部配置器件來進行時序控制。以Altera公司的系列FPGA為例,其本身不能控制配置時序,就有專用的EPC系列配置器件供其使用。在含有微處理器(MPU或MCU)的系統中(如嵌入式系統),可以使用微處理器產生配置時序,將保存在系統RO風吹草動的配置數據置入FPGA。與前面一種方案相比,該方案不僅節省了成本,更縮小了系統體積。在對成本和體積敏感的系統中,該方案非常適用。

在某手持式通信設備的設計中,使用了嵌入式系統和FPGA完成了系統功能。嵌入式微處理器采用Samsung公司的ARM7TDMI系列處理器S3C44B0X;FPGA采用Alrera公司的APEX 20K系列EP20K200E,使用S3C44B0X完成了對EP20K200E的配置,取得了良好效果。本文對其實現方法予以介紹。

1 ARM嵌入式處理器S3C4480X簡介

S3C44B0X是Samsung公司專為手持設備和一般應用而設計的高性價比和高性能的嵌入式處理器。其突出特點它的CPU核采用ARM公司的16/32位ARM7TDMI RISC內核,0.25μm CMOS工藝制造,主頻最高可達66MHz,存儲器尋址空間達256MB。由于其成本和功耗低,特別適合對成本敏感和功能敏感的應用場合,如PDA、GPS、LCD Game、E-Book等。

2 APEX 20K系列FPGA配置方式及配置文件

2.1 配置方式介紹

Altera公司的APEX 20K系列FPGA可以使用以下方式進行配;

①使用專用配置器件,如EPC16、EPC8、EPC2、EPC1、EPC1441;

②被動串行方式(PS),使用微處理器的串行步接口或ByteBlaster下載電纜;

③被動并行同步方式(PPS),使用微處理器的并行同步接口;

④被動并行異步方式(PPA),使用微處理器的并行異步接口;

⑤邊界掃描方式(JTAG),使用JTAG下載電纜。

使用方式①時,需要首先使用下載電纜將計算機生成的FPGA配置文件燒入EPC配置器件中,然后由EPC配置器件控制配置時序對FPGA進行配置,一次燒寫即可重復使用。使用方式②、③、④時,配置文件事先以二進制形式保存在系統ROM中,可以脫離開計算機重復使用。若使用方②、③、④時,配置文件事先以二進制形式保存在系統ROM中,可以脫離開計算機重復使用。若使用方式②,微處理器將配置數據以串行(比特流)方式送給FPGA,在配置時鐘驅動下完成配置。若使用方式③,微處理器將配置數據以并行(字節)方式送給FPGA,由FPGA在其內部將并行數據轉換成串行數據,該串行化的過程需要外部配置時鐘的驅動。在配置時鐘速率相同的情況下,方式②、③所用的配置時間幾乎相同,但方式②的接口要比方式③簡單,若使用方式④,微處理器仍將配置數據以并行方式送給FPGA,在FPGA內部完成數據串行化;與方式③不同的是,該過程不需要外部配置時鐘的驅動,但其接口更復雜,并且需要進行地址譯碼,增加了系統的復雜程度,一般很少采用。使用方式⑤時需要計算機的配合,無法在最終的實際系統中脫機使用,此處不予討論。

通過上述討論可以看出,在使用APEX 20K系列FPGA開發實際應用系統,特別是要形成某種產品時,如果系統中不含微處理器,只能使用方式①;若系統中含有微處理器,方式①、②、③、④都可以使用,但②、③、④可以發現,方式②的接口最簡單,實現起來比其它兩種方式都方便因而在含有微處理器的系統中得到了廣泛應用,本通信系統的設計中即采用了該方式。

2.2 配置文件的使用

Altera公司的開發工具Quartus II及MAX+PLUS II可以生成多種格式的配置文件,針對不同的配置方式要使用不同格式的配置文件。設計項目編譯以后會自動生成.sof文件和.pof文件。其中.pof文件在配置方式①使用專用配置器件時使用,.sof文件用于通過連接在計算機上的下載電纜直接對FPGA進行配置的場合,配置方式可以是JTAG方式或PS方式中使用ByteBlaster下載電纜的情況。基于.sof文件還可以生成.hex、.rbf和.ttf文件。.hex文件是Intel Hex格式的ASCII碼文件,第三方的編程器可以使用這種格式的文件對Altera公司的配置器件進行編程。.rbf文件是二進制文件,1字節的rbf數據包含8bit的配置數據,使用時將其存入ROM中。微處理器人ROM使用這種格式的文件。.ttf文件是列表文本文件,.rbf文件的ASCII碼存儲形式,并且各個字節之間用逗號進行了分隔。如果系統中有其它程序,可以將.ttf文件作為系統程序源代碼的一部分,和其它程序一起編譯。本系統中采用了.ttf文件作為系統程序的一個頭文件使用,其配置數據以數組形式被配置程序使用。對于某種特定型號的FPGA,無論其設計有多復雜,在相同版本的開發工具下生成的配置文件大小是一樣的。

3 被動串行方式(PS)配置時鐘

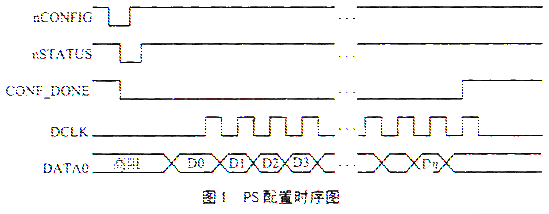

使用PS方式對FPGA進行配置時,只需要5根信號線,其配置時序如圖1所示。

配置時這五根信號線都接至微處理器的I/O上,其中nCONFIG、DCLK、DATA0設置成輸出態,由微處理器對FPGA進行操作;nSTATUS/CONF_DONE設置成輸入態,由微處理器對FPGA的配置狀態進行檢測。微處理器首先在nCONFIG信號線上產生一個寬度大于8μs的負脈沖,然后開始檢測nSTATUS信號的狀態。FPGA檢測到nCONFIG信號的下降沿后會迫使nSTATUS和CONF_DONC信號拉低,并且在nCONFIG信號重新抬高之間保持為低電平。NCONFIG信號抬高后,nSTATUS將在1μs之內隨之抬高,微處理器檢測到此變化后就認為FPGA已經做好準備可以開始配置。配置第一個上升沿與nSTATUS的上升沿之間要求至少有1μs的時間間隔。由于配置數據是與配置上升沿同步的,在配置時鐘的上升沿來之間應當將1bit的配置數據在數據線上準備好,配置數據按低位在先高位在后的順序從數據線上送出。當全部配置數據送出以后,CONF_DONE信號將被抬高,表明配置結束。微處理器檢測到CONF_DONE信號抬高,就結束配置過程。如果配置過程中出錯,FPGA將迫使nSTATUS信號拉低,微處理器檢測到此變化將重新開始配置。

配置結束以后,FPGA還需要個初始化的過程才能進入正常工作狀態。在Quartus II或MAX+PLUS II生成的配置文件中已經包含了額外的初始化比特,只需將配置文件 數據在配置時鐘的同步下全部送出就已經完成了初始化,用戶不必另外加以考慮。

4 硬件電路設計

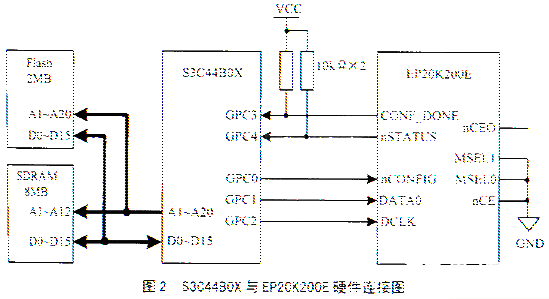

系統的硬件電路設計如圖2所示。

由于S3C44B0X內部只有8KB的SRAM作CPU的Cache使用,無法滿足系統程序存儲及運行的需要,因此需要外掛存儲器作為程序保存和運行的空間。系統中使用1片2MB的Flash作為程序存儲器,系統的整個應用程序,包括EP20K200E配置程序及配置文件都固化于其中保存。另外使用1片9MB的SDRAM作為系統程序運行空間,S3C44B0X、Flash和SDRAM構成了一個最小的嵌入式系統。Flash、SDRAM與S3C44B0X的連接方法可參考S3C44B0X用戶手岫。

使用PS配置地需要將EP20K200E的MSEL0、MSEL1、nCE三個引腳接地,然后將EP20K200E的nCONFIG、DATA0、DCLK、CONF_DONE、nSTATUS引腳分別接至S3C44B0X的GPC0、GPC1、GPC2、GPC3、GPC4引腳上。S3C44B0X的I/O口均為多功能口,可以根據應用的需要通過內部寄存器將其設置成輸入口、輸出口或特別功能口。此處將GPC0、GPC1和GPC2設置成輸出口,將GPC3和GPC4設置成輸入口。

5 軟件設計

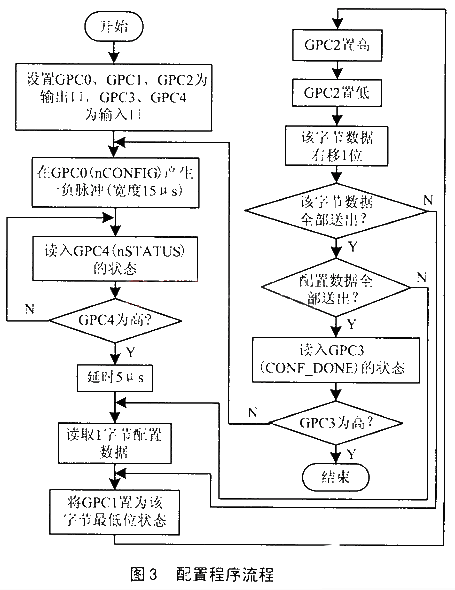

配置時根據配置時序要求,首先在GPC0引腳(對應nCONFIG)產生一個負脈沖,啟動配置,然后檢測GPC4引腳的nSTATUS信號。NSTATUS信號正常后就在GPC2引腳(對應DCLK)上送配置時鐘,在GPC1引腳(對應DATA0)上同步送出配置數據。配置數據以字節為單位從SDRAM中讀出,通過移位操作以串行比特流方式從GPC1引腳送出。全部數據送出后,檢測GPC3引腳(對應CONF_DONE)的狀態,如為高電平說明配置成功,否則配置失敗,需要重新進行配置。配置程序流程如圖3所示。

程序實現使用了C語言。在GPC0引腳產生負脈沖可以通過對其先寫0后寫1來實現,延時使用簡單的循環語句即可,其語句為

rPDATC=rPDATC%26;amp;0xfffe; //*GPC0置低

for(i=0;i《150;i++); //延時15μs

rPDATC=rPDATC|0x0001|; //GPC0置高

其中rPDATC為C端口的數據寄存器。

讀入某個引腳的狀態并判斷其高低可以使用一條語句實現,如讀入GPC4的狀態并判斷其高低為

while(!rPDATC%26;amp;0x0010));

如果GPC4為低電平,該語句就會一直此處循環,直至其變為高電平。

配置時鐘通過在GPC2引腳循環置0、置1來實現,其實現語句為rPDATC=rPDATC|0x0004;//GPC2置高rPDATC=rPDATC%26;amp;0xfffb;//GPC2置低

在GPC2由低變高之前,將1bit的配置數據在GPC1引腳上準備好。

如果配置過程中出錯,EP20K200E將會迫使nSTATUS引腳拉低來通知S3C44B0X。在本程序中為了主加快配置速度,沒有對此進行判斷,而是在程序最后通過CONF_DONE信號否抬高來判斷配置成功與否。如果配置出錯,該信號將不會抬高,從而可以重新開始配置。

本國程序、配置文件和系統的其它程序統一編譯成一個應用程序存在Flash中,系統加電以后首先運行位于Flash 0地址的引導程序,引導程序完成CPU的初始化,然后將應用程序從Flash復制到SDRAM中,從SDRAM中開始運行。在本系統中使用了實時多任務操作系統(RTOS),在軟件設計時將配置程序放在第一個運行的任務中,保證在開機手首先完成FPGA配置。配置所需要的時間與微處理器的運行速度及配置文件的大小有關。在本系統中,微處理器運行在64MHz,配置文件的二進制形式有240KB,配置所需的時間在3s左右。

本文所討論的在嵌入式系統中利用微處理器實現對FPGA配置的方案不僅在系統成本上有優勢,而且在系統體積上也有優勢,已經在實際系統中得到了應用,取得了良好效果。本方案雖然是針對APEX 20K系列FPGA的,但對于Altera公司其它系列的FPGA產品,只需稍做改動即可加以應用。另外,由于FPGA具有可重復配置的靈活性,可以在系統中包含多個不同功能的配置文件,使用時根據功能需要進行相應的配置,實現了一機多能。這一點在日益興起的軟件無線電系統中具有廣闊的應用前景。

責任編輯:gt

電子發燒友App

電子發燒友App

評論