低于+3V時,③腳又輸出高電平,如此不斷反復而使輸出電壓值穩定于額定輸出電壓12V上。 由R1、R2、C1、D1組成啟動電路,使電路在剛接通時向BG3提供基極電流,促使開關管BG1、BG2導通,并向

2009-03-06 22:13:04

管BG3、BG1、BG2均截止。當②腳所接電容的電壓低于+3V時,③腳又輸出高電平,如此不斷反復而使輸出電壓值穩定于額定輸出電壓12V上。 由R1、R2、C1、D1組成啟動電路,使電路在剛接通時向

2021-05-12 07:30:10

如何用FPGA實現串行算法?我想用FPGA做一個隨機數發生器,然后想用李世剛那個超素數法,但是要生成1024bit的01序列,它們是用第一bit順推第二bit 的產生。請問大神 ,有沒有沒有好的辦法

2013-03-11 19:23:49

、IPC_FRAMS_OUT0這些任務,我的問題是1、OSD以及SCD具體分別是什么算法,完成什么功能?如何可以禁用掉?2、IPC_FRAMS_IN0、IPC_FRAMS_OUT0這些任務又在DSP上負責什么任務? 謝謝~

2020-04-17 09:57:11

。 XC2V1000-4FGG456C Virtex-II已經成為過去,更高的Virtex-早也已經誕生了,但xilinx的中文資料比較少, 供大家參考學習下更多資料參考http

2013-09-06 16:28:27

IC FPGA 328 I/O 575BGA

2023-04-06 16:01:50

IC FPGA 328 I/O 575PBGA

2023-04-06 16:01:53

IC FPGA 392 I/O 575BGA

2023-04-06 16:01:49

IC FPGA 392 I/O 575MBGA

2023-04-06 16:01:16

IC FPGA 392 I/O 575BGA

2023-04-06 16:01:16

IC FPGA 392 I/O 575BGA

2023-03-23 07:49:01

IC FPGA 392 I/O 575BGA

2023-04-06 16:01:24

IC FPGA 392 I/O 575BGA

2023-03-23 07:48:35

IC FPGA 392 I/O 575BGA

2023-04-06 16:01:24

IC FPGA 408 I/O 575PBGA

2023-04-06 16:01:46

IC FPGA 408 I/O 575BGA

2023-04-06 16:01:53

各位大神,小弟做FPGA不久,最近設計了一個XC3S1500的FPGA板子,經測試電源供電沒問題,但是JTAG鏈路建立不起來,初步懷疑是FPGA芯片和配置芯片(XCF08P)的VCCO不一致

2013-04-03 16:30:12

`XC6SLX16-2FTG256C FPGA 產品介紹 XC6SLX16-2FTG256C特征Spartan-6 FPGA功能摘要?Spartan-6家庭:?Spartan-6 LX FPGA

2019-09-26 11:22:07

EP2C5型 FPGA/SOPC(NiosII)學習開發套件 V3.0 一、FPGA核心板:多種核心板供選擇,所采用的FPGA分別

2009-10-23 15:15:24

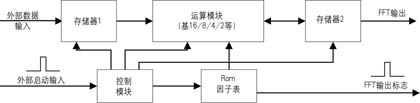

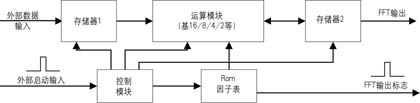

FPGA實現的 FFT 處理器的硬件結構。接收單元采用乒乓RAM 結構, 擴大了數據吞吐量。中間數據緩存單元采用雙口RAM , 減少了訪問RAM 的時鐘消耗。計算單元采用基 2 算法, 流水線結構, 可在

2017-11-21 15:55:13

在信號處理中,FFT占有很重要的位置,其運算時間影響整個系統的性能。傳統的實現方法速度很慢,難以滿足信號處理的實時性要求。針對這個問題,本文研究了基于FPGA芯片的FFT算法,把FFT算法對實時性

2010-05-28 13:38:38

確的色彩平衡。 功能描述(續) 通道有自己獨立的控制管腳,0V至4V控制范圍。一個4V的輸入沒有衰減輸入0V時,衰減12分貝。驅動衰減器級的輸出進入逆變輸入A2。由于這是第二個反轉階段,A2的輸出

2020-07-08 11:46:28

=25?C,VCC1=VCC2=12V;V4=0V。手動調節視頻輸出引腳18、20和23至交流試驗用4V直流電,除非另有說明(注15) OSD電氣特性 見直流試驗電路(圖5),TA=25

2020-07-14 14:41:02

RC4加密算法的FPGA設計與實現 RC4算法是一種密匙長度可變的加密算法.因其實現方便,安全性高,廣泛應用于無線網絡通信. 信息加密隨著計算機網絡的普及,傳統的軟件加密已經越來越不能滿足日常的需求

2012-08-11 11:48:18

RC4加密算法的FPGA設計與實現.pdf

2011-03-21 17:26:28

labview如何實現間隔索引功能,比如有在循環里有10個數,1 2 3.。.。8 9 10,我想索引1 3 5 7 9或者 2 4 6 8 10,請大神指導

2020-07-07 11:05:57

求FPGA算法,具體如下: 上位機每隔一段時間(約10秒)向下位機發送一段數據,數據格式為M[16],V[16],target(M為16個64bit的數據,V為16個64bit的數據,target為

2017-07-25 20:13:31

FPGA算法工程師職責:1. 基于FPGA的圖像處理算法設計實現;2. 與團隊配合,對FPGA實現算法進一步優化;3. 根據整體工程分配子任務,進行詳細方案設計并寫入文檔;4. 根據詳細方案進行

2017-06-08 15:36:18

摘要針對FFT算法基于FPGA實現可配置的IP核。采用基于流水線結構和快速并行算法實現了蝶形運算和4k點FFT的輸入點數、數據位寬、分解基自由配置。使用Verilog語言編寫,利用ModelSim

2019-07-03 07:56:53

功率。

STA575 200瓦功率音頻放大器電路可通過Stby/靜音引腳設置為三種狀態:待機(Vpin 4V)。

在待機模式下,信號路徑中涉及的所有電路都處于關閉狀態,而在靜音模式下,電路偏置,但揚聲器

2023-09-11 16:56:14

以及相鄰的八個點都是‘1’f(x,y)的值才是‘1’。這樣就完成了二值圖像的膨脹。3 FPGA膨脹算法實現圖3 二值圖像膨脹FPGA模塊架構圖3中我們使用串口傳圖傳入的是二值圖像。FPGA源碼

2018-08-14 09:08:57

,7c/4]范圍內時,可以采用 FPGA 的 IP CORE(CORDIC 算法)實現雙曲正弦函數和雙曲余弦函數,因此在 FPGA 內部求以 2 為底的指數函數時,可以先將自變量歸一化在[0,1]內,然后將自

2020-08-14 09:06:10

系列中以18Kbits 為一塊,在規模最小的型號XC3S100E 上集成了4 塊這樣的內存,如圖2 所示:圖2 Spartan-3E 系列FPGA 集成的Block RAM

2012-05-14 12:37:37

碼力分享基于FPGA的可變祖沖之(ZUC)算法的設計與實現1:概述基于FPGA的可變祖沖之(ZUC)算法的設計與實現軟件:ISE語言:Verilog HDL,C語言 2:功能通過加入可配置模塊(如S

2015-10-14 21:56:52

文章第一篇:基于FPGA的靜態圖片顯示第二篇:基于FPGA彩色圖像轉灰度算法實現第三篇:基于FPGA的Uart發送圖像數據到VGA顯示`

2017-08-28 11:34:10

本文重點討論了如何根據射頻前端的輸出設計全數字AGC以擴展接收機的動態范圍,并給出了基于FPGA的外部AGC電路算法。

2021-04-30 06:57:26

基于FPGA的多路回聲消除算法的實現中文期刊文章作 者:尹邦政 朱靜 毛茅作者機構:[1]廣州廣哈通信股份有限公司,廣東廣州510663;[2]廣州大學實驗中心,廣東廣州510006出 版 物

2018-05-08 10:23:36

FPGA(XC3S200),經PID調節器控制電流環;同樣,斬波電壓電流經濾波通過A/D轉換也進人FPGA。圖2所示為FPCA的最小系統電路,XCF02S為FPGA XC3S200的配置芯片

2016-02-01 14:44:30

`大家好,給大家介紹一下,這是基于FPGA的膚色識別算法實現。我們今天這篇文章有兩個內容一是實現基于FPGA的彩色圖片轉灰度實現,然后在這個基礎上實現基于FPGA的膚色檢測算法實現。將彩色圖像轉化

2017-10-28 08:48:57

、資料以及更多FPGA的學習資料哦! 圖像處理系列文章第一篇:基于FPGA的靜態圖片顯示第二篇:基于FPGA彩色圖像轉灰度算法實現第三篇:基于FPGA的Uart發送圖像數據到VGA顯示第四篇

2017-09-22 13:20:55

Step1,否則繼續下一步; Step4:若增量序列未結束,則從指針位置取一增量項(y1,y2,y3),否則,取前一象素的索引作為當前象素的匹配結果,轉Step1; Step5:求出修正后的待匹配

2009-09-19 09:34:49

的變慢會降低整個流水的吞吐率[3,4]。[/url]這樣分解后,被旋轉向量與K的乘轉化為簡單的移位加減運算,從而可以解決乘法器一級速度變慢而降低整個流水線吞吐率的問題。其硬件實現結構如圖2所示。這種結構

2011-07-11 21:32:29

本文基于這種算法理論基礎,使用xilinx公司規模較大的XC4VLXl5系列FPGA,實現了紅外圖像的實時處理。

2021-04-29 06:54:30

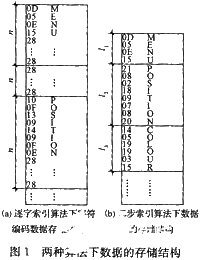

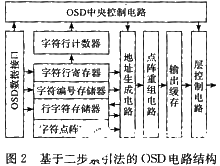

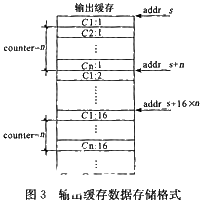

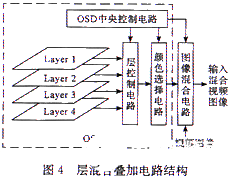

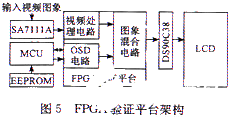

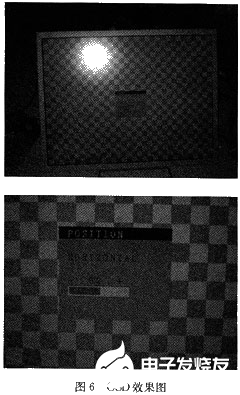

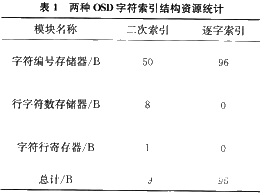

存儲器資源的使用情況,因此采用更優化的字符索引算法可以達到降低存儲器資源需求量的目的。作者在逐字符索引法的基礎上,針對該算法的缺點,提出了二步索引法。在保證OSD功能完整的同時,大大地降低了系統對存儲器資源的需求。

2019-08-13 06:39:33

二步索引算法的原理及特點是什么?如何去實現二步索引法OSD電路?如何去驗證OSD電路?

2021-05-06 07:08:58

OSD是什么?OSD包含的基本元素有哪些?如何去實現一種OSD?有什么方法嗎?

2021-06-02 06:04:06

FFT算法的實現為了提高FFT工作頻率和節省FPGA資源,采用3級流水線結構實現64點的FFT運算。流水線處理器的結構如圖2所示。每級均由延時單元、轉接器(SW)、蝶形運算和旋轉因子乘法4個模塊組成

2019-06-17 09:01:35

請問一下如何用FPGA實現FFT算法?

2021-04-08 06:06:26

主要內容包括:1. 為什么很多人覺得學習FPGA很困難,以及HDL學習的一些誤區;2. 軟件和硬件在算法實現上的區別;3. 通過具體例子詳細講解了從算法的行為級建模向RTL級建模的轉換思想和底層電路

2015-09-18 15:44:39

怎么實現STM32步進電機S型加減速算法?

2021-10-11 07:57:55

現在思路亂了,不知道改怎么做了。我想實現一個excel對比功能,第一步 導入表格1+表格2第二步 對比表格1和表格2第三步 把表格1和表格2不同的部分導入一個新的表格求指點,謝謝重點是第二步

2014-02-28 11:13:24

怎么實現步進電機S型曲線加減速算法?

2021-10-12 10:02:51

本文研究的就是在FPGA設計平臺上設計硬件電路,實現數字圖像的空域濾波算法。

2021-04-30 06:29:41

近年來,數字視頻監控系統在銀行、高速公路、樓宇等各個領域取得了廣泛的應用。在數字視頻監控系統中,OSD(OnScreenDisplay)技術是不可或缺的部分。OSD為用戶提供友好的人機界面,能夠使用戶獲得更多的附加信息。

2019-08-27 07:09:20

本文以實現抽取率為2的具有線性相位的3階FIR抽取濾波器為例,介紹了一種用XC2V1000型FPGA實現FIR抽取濾波器的設計方法。

2021-05-07 06:02:47

`怎么讓直流電源執行時 一步一步執行,比如:第一步輸出5V 、2A、 工作10秒、再執行第二步、第二步輸出3V、1A、工作30秒再執行第三步,求幫助,不知道怎么做!`

2018-03-08 09:02:35

用FPGA硬件實現。 現在我沒有FPGA硬件實現的經驗,不知道如何用FPGA硬件實現小波算法。 懇請賜教!謝謝!

2012-11-20 21:35:16

據,A1、A2、A3、A4是3個比較器,輸出的值分別是第i-1行3個值、第i行3個值、第i+1行3個值的中值。以這3個中值再輸入A4就可以選出9個點的中值。這樣大大提高了算法的效率。5 二值化 經過中值

2009-09-19 09:38:11

謝謝各位。。各位大神。。用fpga實現FFT算法,最好是verilog hdl的。。或者推薦一些好書。。

2013-05-06 00:24:19

:FPGAVirtex?系列Virtex-E:XCV50E - XCV600E Virtex-II:XC2V40 - XC2V600 Virtex-II Pro:XC2VP2 - XC2VP7 Virtex-4

2020-06-05 09:23:59

就已經出現,隨著FPGA芯片價格的不斷降低,其在工業領域的應用正在飛速發展,采用FPGA來實現SVPWM調制算法也將層出不窮2. 系統任務分析及實現SVPWM調制算法相對比較復雜,在完成系統控制任務

2022-01-20 09:34:26

的工作量。PXA270處理器具有領先的高性能和低功耗功能,宏芯T128D具有強大的視頻處理功能,同時集成了兩層OSD處理引擎,兩者通過I2C總線連接可以大大提高車載導航設備的多媒體處理功能,本文陳述了在兩者基礎上通過I2C總線連接實現OSD顯示驅動的方法。

2019-06-21 06:15:02

針對當前圖索引算法存在的問題,提出一種基于對比子圖索引框架,開發冗余感知機制,選擇一個小型的具有明顯區分力的索引特征集,改善索引性能。實驗結果表明,該算法對不

2009-03-20 14:28:45 20

20 小波盲源分離算法的仿真及FPGA實現:提出了一種基于小波變換的盲源分離方法,在理論分析和仿真結果的基礎上,給出了FPGA 的實現方案。針對傳統盲分離算法對源信號統計特征敏

2009-06-21 22:44:09 21

21 介紹了基于Xilinx Spartan- 3E FPGA XC3S250E 來完成分辨率為738×575 的PAL 制數字視頻信號到800×600 的VGA 格式轉換的實現方法。關鍵詞: 圖像放大; PAL; VGA; FPGA

目前, 絕大多數監

2010-09-22 10:29:16 174

174 介紹了AES中,SubBytes算法在FPGA的具體實現.構造SubBytes的S-Box轉換表可以直接查找ROM表來實現.通過分析SubBytes算法得到一種可行性硬件邏輯電路,從而實現SubBytes變換的功能.

2010-11-09 16:42:48 25

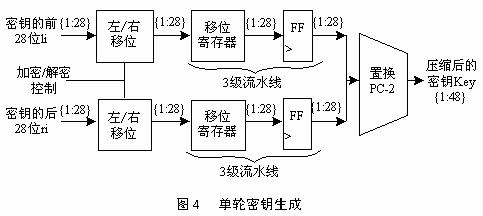

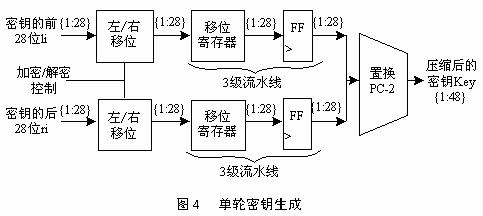

25 摘要:介紹3-DES算法的概要;以Xilinx公司SPARTANII結構的XC2S100為例,闡述用FPGA高速實現3-DES算法的設計要點及關鍵部分的設計。引 言

2006-03-13 19:36:42 651

651

用FPGA實現FFT算法

引言 DFT(Discrete Fourier Transformation)是數字信號分析與處理如圖形、語音及圖像等領域的重

2008-10-30 13:39:20 1426

1426

摘要:介紹3-DES算法的概要;以Xilinx公司SPARTANII結構的XC2S100為例,闡述用FPGA高速實現3-DES算法的設計要點及關鍵部分的設計。

關鍵詞:3-DES

2009-06-20 14:22:00 1317

1317

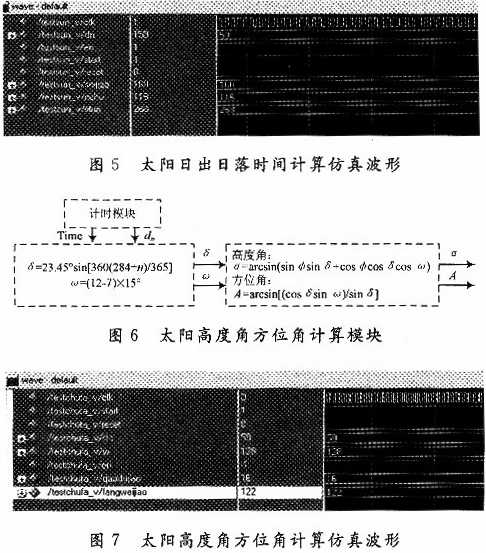

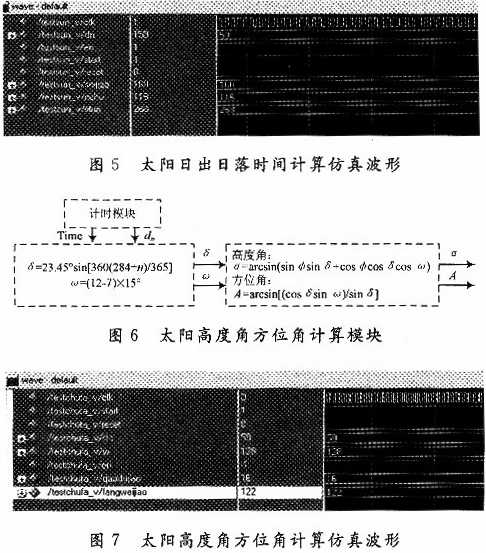

本設計采用傳統的視日運動跟蹤法,利用Xilinx公司提供的FPGA開發環境ISE,設計完成了基于XC3S1500開發板的

2010-09-29 09:42:21 1167

1167

介紹了一種適于TUD 系統的SHA256算法和HMAC算法! 給出了在FPGA上實現SHA256算法和HMAC 算法的一種電路設計方案!并對算法的硬件實現部分進行了優化設計! 給出了FPGA的實現結果

2011-05-16 16:50:45 141

141 MIDI合成算法及其FPGA實現.

2012-04-16 13:57:38 44

44 基于FPGA的SM3算法優化設計與實現的論文

2015-10-29 17:16:51 4

4 ECT圖像重建算法的FPGA實現

ECT圖像重建算法的FPGA實現

2015-11-19 14:59:41 1

1 基于FPGA的三相SVPWM調制算法的實現。

2016-04-18 09:47:49 23

23 利用FPGA的IP核設計和實現FFT算法

2016-05-24 14:14:47 36

36 Xilinx FPGA工程例子源碼:在FPGA上實現CRC算法的程序

2016-06-07 15:07:45 28

28 基于FPGA的JPEG解碼算法的研究與實現

2016-08-29 16:05:01 11

11 新的自調整多叉樹RFID防碰撞算法的FPGA實現_任少杰

2017-01-08 15:15:59 2

2 LMS自適應算法的FPGA設計與實現_陳亮

2017-03-19 11:27:34 5

5 本文是基于FPGA實現Cordic算法的設計與驗證,使用Verilog HDL設計,初步可實現正弦、余弦、反正切函數的實現。將復雜的運算轉化成FPGA擅長的加減法和乘法,而乘法運算可以用移位運算代替

2018-07-03 10:18:00 2349

2349

基于SOC技術的模塊化設計要求各功能模塊盡可能小地占用電路資源,以滿足芯片系統對資源使用和面積的控制。對于OSD功能模塊而言,存儲器資源為主要開銷。因此,減少存儲器資源的使用對降低OSD模塊電路資源需求有著重要的意義。

2019-01-15 09:47:00 1290

1290

本文檔的主要內容詳細介紹的是xc7z020和xc7z010 FPGA芯片的電路原理圖免費下載。

2019-02-12 17:20:24 471

471 介紹了3DES 數據加密算法(DDA)的原理,針對利用FPGA 硬件實現3DES 算法,給出了一種可進化IP 核的具體設計思想,采用可重構電路節省器件內部資源,并采用有限狀態機設計技術從而實現數據

2020-01-16 10:58:00 17

17 基于FPGA的定點LMS算法的實現講解。

2021-04-28 11:17:25 10

10 FPGA算法是指在FPGA(現場可編程門陣列)上實現的算法。FPGA是一種可重構的硬件設備,可以通過配置和編程實現各種不同的功能和算法,而不需要進行硬件電路的修改。

FPGA算法可以包括

2023-08-16 14:31:23 1604

1604

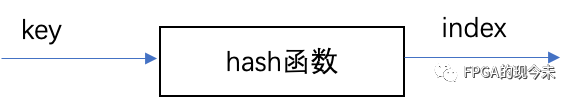

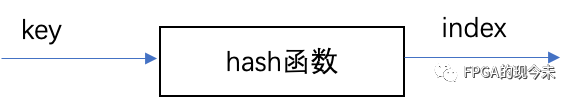

在FPGA的設計中,尤其是在通信領域,經常會遇到hash算法的實現。hash算法在FPGA的設計中,它主要包括2個部分,第一個就是如何選擇一個好的hash函數,減少碰撞;第二個就是如何管理hash表。本文不討論hash算法本身,僅說明hash表的管理。

2023-09-07 17:01:32 471

471

![]()

電子發燒友App

電子發燒友App

評論