大多數(shù)存儲(chǔ)器接口都是源同步接口,從外部存儲(chǔ)器器件傳出的數(shù)據(jù)和時(shí)鐘/ 選通脈沖是邊沿對(duì)齊的。在 Virtex-4 器件采集這一數(shù)據(jù),需要延遲時(shí)鐘/ 選通脈沖或數(shù)據(jù)。利用直接時(shí)鐘控制技術(shù),數(shù)據(jù)經(jīng)延遲,并與內(nèi)部 FPGA 時(shí)鐘實(shí)現(xiàn)中心對(duì)齊。在這個(gè)方案中,內(nèi)部 FPGA時(shí)鐘采集傳出的數(shù)據(jù)。存儲(chǔ)器傳出的時(shí)鐘/ 選通脈沖用于決定與數(shù)據(jù)位相關(guān)的延遲值。因此,與選通脈沖相關(guān)的數(shù)據(jù)位的數(shù)量不受限制。由于無需將選通脈沖分配給相關(guān)數(shù)據(jù)位,所以不需要其他時(shí)鐘資源。

時(shí)鐘/ 選通脈沖和數(shù)據(jù)位使用的 Virtex-4 資源是一條 64-tap 絕對(duì)延遲線。該 64-tap 絕對(duì)延遲線可利用 IDELAY 和 IDELAYCTRL primitive 實(shí)現(xiàn)。時(shí)鐘/ 選通脈沖和數(shù)據(jù)位均通過此 64-tap絕對(duì)延遲線來布線。雖然選通脈沖不 用于采集數(shù)據(jù),但它用于確定數(shù)據(jù)與內(nèi)部 FPGA 時(shí)鐘實(shí)現(xiàn)中心對(duì)齊所需的 tap 數(shù)量。以下部分將詳細(xì)解釋直接時(shí)鐘控制技術(shù)方案的設(shè)計(jì)及實(shí)現(xiàn)。

選通脈沖邊沿檢測(cè)

與時(shí)鐘/ 選通脈沖相關(guān)的數(shù)據(jù)位的延遲值就是內(nèi)部 FPGA 時(shí)鐘上升沿與時(shí)鐘/ 選通脈沖中心之間的相位差。假設(shè)時(shí)鐘/ 選通脈沖和數(shù)據(jù)實(shí)現(xiàn)了邊沿對(duì)齊。要確定這個(gè)相位差,時(shí)鐘/ 選通脈沖通過 IOB 內(nèi)的 64-tap 絕對(duì)延遲線輸入,并利用內(nèi)部 FPGA 時(shí)鐘在增量 tap 輸出端對(duì)其進(jìn)行采樣。

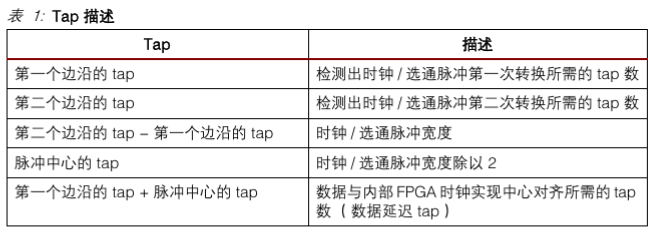

要確定時(shí)鐘/ 選通脈沖的中心,至少需要檢測(cè)到時(shí)鐘/ 選通脈沖的兩個(gè)邊沿或轉(zhuǎn)換。檢測(cè)出第二次轉(zhuǎn)換所需的 tap 數(shù)(即第二個(gè)邊沿的 tap)和檢測(cè)出第一次轉(zhuǎn)換所需的 tap 數(shù)(即第一個(gè)邊沿的 tap)之差,即為時(shí)鐘/ 選通脈沖寬度。這個(gè)差值的二分之一就是脈沖中心(即脈沖中心的 tap)。從內(nèi)部 FPGA 時(shí)鐘上升沿到時(shí)鐘/ 選通脈沖中心之間的 tap 數(shù),即為第一個(gè)邊沿的tap 數(shù)與脈沖中心的 tap 數(shù)之和。

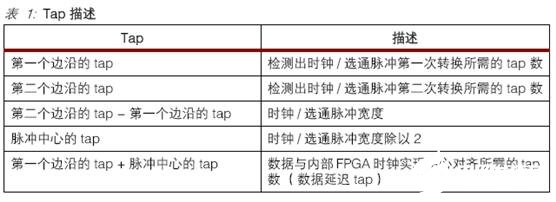

表1 描述了各類 tap 數(shù)量。

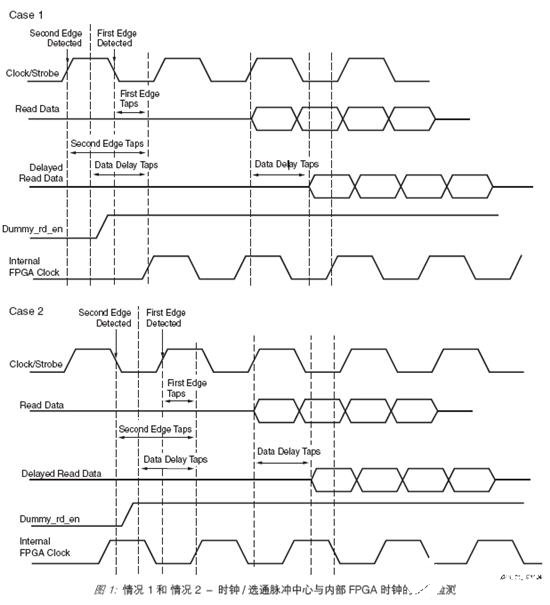

圖1 說明了通過使數(shù)據(jù)延遲相應(yīng)的 tap 數(shù),讓數(shù)據(jù)與內(nèi)部 FPGA 時(shí)鐘實(shí)現(xiàn)中心對(duì)齊的兩種情況。第 1 種情況所示為,由于時(shí)鐘/ 選通脈沖的下降沿是被檢測(cè)到的第一個(gè)邊沿,因此內(nèi)部FPGA 時(shí)鐘的上升沿位于延遲數(shù)據(jù)的中心。第 2 種情況所示為,由于時(shí)鐘/ 選通脈沖的上升沿是檢測(cè)到的第一個(gè)邊沿,因此內(nèi)部 FPGA 時(shí)鐘下降沿位于延遲數(shù)據(jù)的中心。

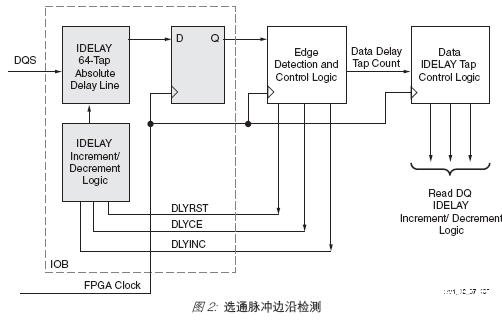

實(shí)現(xiàn)選通脈沖邊沿檢測(cè)

由于具有專用的 IDELAY 和 IDELAY_CTRL 電路,所以可以輕松地在 Virtex-4 器件中實(shí)現(xiàn)確定延遲值的電路。實(shí)現(xiàn)確定延遲值電路的結(jié)構(gòu)圖如圖2 所示。

利用一個(gè)簡(jiǎn)單的算法檢測(cè)存儲(chǔ)器時(shí)鐘/ 選通脈沖的邊沿。將初始值為 0 的時(shí)鐘/ 選通脈沖輸入IDELAY 模塊。時(shí)鐘/ 選通脈沖將不停地增加 1 tap 的延遲,直到檢測(cè)到第一個(gè)邊沿。然后記錄下檢測(cè)出第一個(gè)邊沿所需的 tap 數(shù)。在檢測(cè)到第二個(gè)邊沿之前,時(shí)鐘/ 選通脈沖仍然不停地增加 1 tap 的延遲。然后記錄下檢測(cè)出第二個(gè)邊沿所需的 tap 數(shù)。根據(jù)兩次記錄的值,計(jì)算出脈沖寬度。在用 tap 數(shù)確定時(shí)鐘/ 選通脈沖寬度后,除以 2 即得到中間值。中間值與檢測(cè)出第一個(gè)邊沿所需的 tap 數(shù)之和為延遲數(shù)據(jù)所需的tap 數(shù)。

IDELAY 模塊可用的 tap 總數(shù)為64。因此,當(dāng)頻率為 200 MHz 或以下時(shí),將無法檢測(cè)出兩個(gè)邊沿。如果在 64 tap 結(jié)束后僅檢測(cè)出一個(gè)邊沿,那么延遲數(shù)據(jù)所需的 tap 數(shù)應(yīng)為,檢測(cè)出第一個(gè)邊沿所需的 tap 數(shù)減去 16 tap (約 1.25 ns,每個(gè) tap 的延時(shí)約為 75 ps)。一個(gè) 200 MHz 時(shí)鐘/ 選通脈沖周期的四分之一約為 16 tap。根據(jù)時(shí)序分析,該值也適用于更低的頻率,最低可達(dá) 110 MHz。當(dāng)頻率低于 110 MHz 時(shí),如果在 64 tap 結(jié)束后未檢測(cè)出任何邊沿,那么延遲數(shù)據(jù)所需的 tap 數(shù)應(yīng)為 32 tap(約 2.5 ns,每個(gè) tap 的延時(shí)約為 75 ps)。該值足以使內(nèi)部 FPGA時(shí)鐘邊沿位于數(shù)據(jù)窗口內(nèi)。

檢測(cè)第一個(gè)和第二個(gè)邊沿僅需一個(gè)小型狀態(tài)機(jī)。只有在為確定數(shù)據(jù)延遲 tap 數(shù)而發(fā)出的虛讀操作過程中,才啟用該狀態(tài)機(jī)。在正式工作之前,發(fā)送至外部存儲(chǔ)器器件的虛讀操作命令包含多條背靠背讀命令。狀態(tài)機(jī)將控制輸入 IDELAY 電路的信號(hào),即DLYRST、DLYCE 和 DLYINC。

DLYRST - 延遲線復(fù)位信號(hào),將延遲線中的 tap 數(shù)重設(shè)為按 IOBDELAY_VALUE 屬性設(shè)置的值。本設(shè)計(jì)中被設(shè)為 “0”。

DLYCE - 延遲線使能信號(hào),確定何時(shí)激活延遲線遞增/ 遞減信號(hào)。

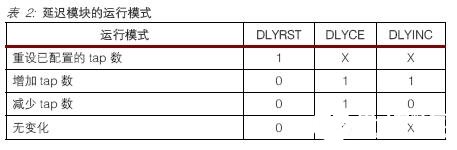

DLYINC - 延遲線遞增/ 遞減信號(hào),可增加或減少延遲模塊中的 tap 數(shù)。表2 描述了延遲線的運(yùn)行模式。

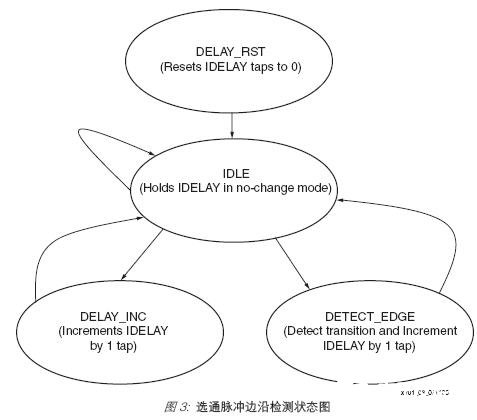

用于控制這些延遲模塊輸入的狀態(tài)圖如圖3 所示。該狀態(tài)機(jī)的四種狀態(tài)分別為:DELAY_RST、IDLE、DELAY_INC 和 DETECT_EDGE。

DELAY_RST

該狀態(tài)是發(fā)起虛讀操作時(shí)啟用的狀態(tài)機(jī)的第一個(gè)狀態(tài)。在這種狀態(tài)下,延遲模塊被重設(shè)為“0”tap。該狀態(tài)之后是多個(gè) IDLE 狀態(tài)。

IDLE

在這種狀態(tài)下,延遲模塊保持“無變化”運(yùn)行模式。除 IDLE 狀態(tài)之外,每種狀態(tài)結(jié)束后都會(huì)出現(xiàn)數(shù)個(gè) IDLE 狀態(tài), 以便處理 tap 輸出值。IDLE 狀態(tài)之后是另一個(gè) IDLE、DELAY_INC 或DETECT_EDGE 狀態(tài)。

DELAY_INC

這個(gè)狀態(tài)使延遲模塊tap 數(shù)加 1。該狀態(tài)之后是數(shù)個(gè)IDLE 狀態(tài)。

DETECT_EDGE

在這種狀態(tài)下,比較延遲模塊的輸出及其上一個(gè)值,用于檢測(cè)信號(hào)邊沿或轉(zhuǎn)換,同時(shí),延遲模塊tap 數(shù)加 1。該狀態(tài)之后是數(shù)個(gè) IDLE 狀態(tài)。

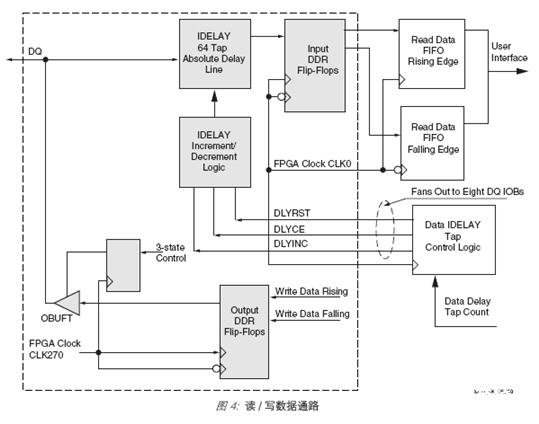

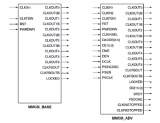

在確定了延遲數(shù)據(jù)所需的 tap 數(shù)后,將啟用數(shù)據(jù) IDELAY 電路,并增加到這一數(shù)值。按照所需的 tap 數(shù),使數(shù)據(jù) IDELAY 電路增加相同的時(shí)鐘周期。數(shù)據(jù) IDELAY 電路的讀/ 寫數(shù)據(jù)通路結(jié)構(gòu)圖如圖4 所示。

數(shù)據(jù)采集與二次采集

如圖4 所示,利用內(nèi)部FPGA時(shí)鐘,在輸入 DDR 觸發(fā)器中采集延遲數(shù)據(jù)。然后,把這些觸發(fā)器的輸出存儲(chǔ)到兩個(gè)FIFO 中;一個(gè)代表上升沿?cái)?shù)據(jù),另一個(gè)代表下降沿?cái)?shù)據(jù)。這些FIFO 是利用LUT RAM 實(shí)現(xiàn)的,其寫使能操作由控制器生成的讀使能信號(hào)提供,并在數(shù)據(jù)格式校準(zhǔn)的基礎(chǔ)上與采集的讀取數(shù)據(jù)對(duì)齊。

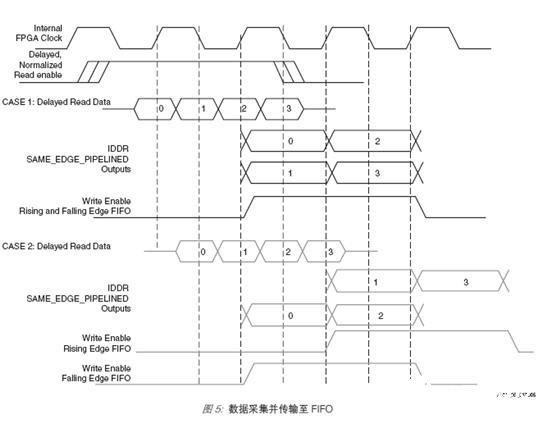

DDR2 SDRAM 器件并未隨讀取數(shù)據(jù)一同提供讀有效或讀使能信號(hào)。因此,控制器將根據(jù) CAS延遲和突發(fā)長(zhǎng)度,生成這個(gè)讀使能信號(hào)。在開始執(zhí)行讀取操作時(shí),必須令該讀使能信號(hào)有效,并在選通脈沖的最后一個(gè)上升沿結(jié)束后使其無效。在IDDR 觸發(fā)器的輸出端,該讀使能信號(hào)必須與采集到的讀取數(shù)據(jù)對(duì)齊。為了實(shí)現(xiàn)讀使能對(duì)齊,在數(shù)據(jù)與FPGA 時(shí)鐘對(duì)齊后,將已知數(shù)據(jù)格式寫入存儲(chǔ)器。然后讀回已知數(shù)據(jù)格式,并在讀使能信號(hào)與采集到的讀取數(shù)據(jù)對(duì)齊之前,利用移位寄存器延遲讀使能信號(hào)。每字節(jié)數(shù)據(jù)都會(huì)生成一個(gè)讀使能信號(hào)。圖5 為讀使能對(duì)齊的時(shí)序圖。

讀時(shí)序分析

這一部分介紹了利用直接時(shí)鐘控制技術(shù)實(shí)現(xiàn)的讀時(shí)序分析。直接在FPGA 時(shí)鐘域內(nèi)采集讀取數(shù)據(jù),因此,用于數(shù)據(jù)有效窗口分析的存儲(chǔ)器參數(shù)就是存取時(shí)間 (TAC)。下面簡(jiǎn)要介紹了此時(shí)序分析中使用的各個(gè)參數(shù)。

此時(shí)序分析中考慮的外部存儲(chǔ)器參數(shù)有:

TAC - 讀取數(shù)據(jù) (DQ) 的存取時(shí)間(以FPGA 傳遞給存儲(chǔ)器的時(shí)鐘為參照)

TDCD - DCM 輸出占空比失真

利用FPGA 時(shí)鐘而非存儲(chǔ)器時(shí)鐘/ 選通脈沖(DQS),來采集讀取數(shù)據(jù)(DQ) ;因此,該分析考慮了TAC (以時(shí)鐘為參照的數(shù)據(jù)存取時(shí)間)。在此分析中,未考慮DQS - DQ 存儲(chǔ)器參數(shù),如TDQSQ 和TQHS,因?yàn)?TAC 比這兩個(gè)參數(shù)更重要。

此時(shí)序分析中考慮的FPGA 參數(shù)有:

TCLOCK_TREE-SKEW - 緊密放置在該組中的 IOB 觸發(fā)器的全局時(shí)鐘樹歪斜

TPACKAGE_SKEW - 特定器件/ 封裝的封裝歪斜

TSAMP - Virtex-4 源同步數(shù)據(jù)手冊(cè)中規(guī)定的采樣窗口

TIDELAYPAT_JIT - Virtex-4 數(shù)據(jù)手冊(cè)中規(guī)定的每個(gè) IDELAY tap 的數(shù)據(jù)格式抖動(dòng)

通過檢測(cè) DQS 邊沿,計(jì)算出與 DQS 相關(guān)的數(shù)據(jù)位延遲。利用全局時(shí)鐘在 I/O 觸發(fā)器中采集DQS 來進(jìn)行檢測(cè)。因此,最終得到的數(shù)據(jù)延遲值已經(jīng)包含了 I/O 觸發(fā)器的建立時(shí)間和保持時(shí)間。在進(jìn)行最差情況分析時(shí),需要考慮 I/O 觸發(fā)器固有的建立時(shí)間和保持時(shí)間。

此外,計(jì)算數(shù)據(jù)位和相關(guān)選通脈沖之間的歪斜也需要考慮 PCB 布局歪斜。

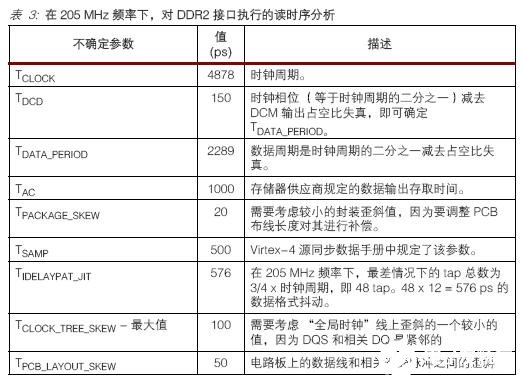

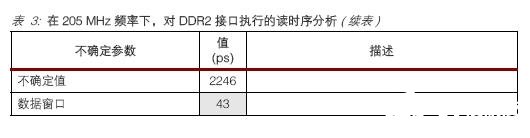

表3 所示為在205 MHz 頻率下,對(duì)DDR2 接口執(zhí)行的讀時(shí)序分析。全部參數(shù)單位均為皮秒。

TDATA_PERIOD 是時(shí)鐘周期的二分之一減去TMEM_DCD。TDATA_PERIOD 與不確定值之和的差,就是有效數(shù)據(jù)窗口 (43 ps)。因此,在 205 MHz 頻率下,-11Virtex-4 器件將產(chǎn)生 43 ps 的余量。

參考設(shè)計(jì)

存儲(chǔ)器接口生成器 (MIG) 工具中集成了直接時(shí)鐘控制數(shù)據(jù)采集技術(shù)的參考設(shè)計(jì)。該工具已被集成到 Xilinx Core Generator 工具中。

結(jié)論

Virtex-4 I/O 架構(gòu)增強(qiáng)了源同步存儲(chǔ)器接口的實(shí)現(xiàn)。本應(yīng)用指南及參考設(shè)計(jì)中使用的架構(gòu)特性包括:

IDELAY 模塊 - 連續(xù)校準(zhǔn)的 tap 延時(shí)很小的延遲元件。

FIFO16 primitive - 用作 FIFO 的 Block RAM,無需使用生成狀態(tài)標(biāo)志所需的其他 CLB 資源。

高速差分全局時(shí)鐘資源提供了更好的占空比。差分時(shí)鐘減少了參考設(shè)計(jì)所需的全局時(shí)鐘資源數(shù)量。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論