跨時(shí)鐘域(Clock Domain Crossing,CDC)信號處理問題,首先要考慮的就是亞穩(wěn)態(tài)。

1.亞穩(wěn)態(tài)

亞穩(wěn)態(tài)是指在設(shè)計(jì)的正常運(yùn)行過程中,信號在一定時(shí)間內(nèi)不能到達(dá)穩(wěn)定的0或者1的現(xiàn)象。

在多時(shí)鐘設(shè)計(jì)中,亞穩(wěn)態(tài)是不可避免的,可以減少亞穩(wěn)態(tài)的發(fā)生和傳播,消除亞穩(wěn)態(tài)的有害影響。

為什么會產(chǎn)生亞穩(wěn)態(tài)?

存儲元件,如交叉耦合反相器、SR鎖存器、D鎖存器和D觸發(fā)器等都有兩個(gè)穩(wěn)定的狀態(tài),即0和1,也就是能存儲0和1這兩個(gè)狀態(tài)。亞穩(wěn)態(tài)就是既不是0又不是1的狀態(tài)。在分析元器件時(shí),把器件抽象為理想器件以簡化分析,但實(shí)際的元器件并不是理想的,一個(gè)理想的CMOS反相器的電平傳輸特性如下所示:

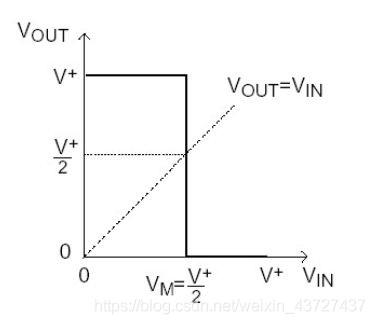

理想的CMOS反相器件的電平傳輸特性:

在0 < VIN < VM時(shí),VOUT= V+

在VM < VIN < V+時(shí),VOUT=0

剛好在VM這個(gè)點(diǎn)就能完成“突變”,界限明確。實(shí)際上變化時(shí)一個(gè)過程的。實(shí)際的CMOS反相器電平傳輸特性如下:

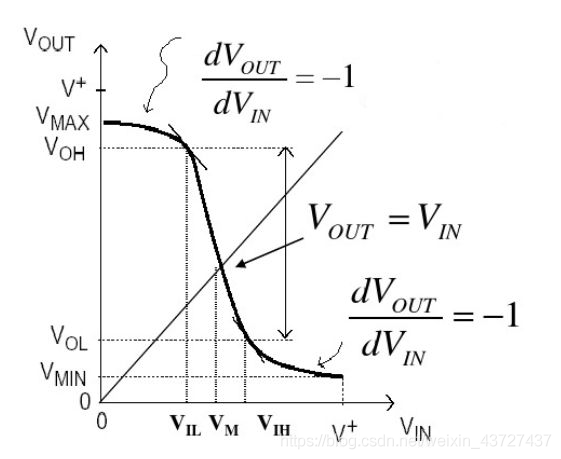

在0 < VIN < VIL時(shí),VOH < VOUT < VMAX

在VIH < VIN < V+時(shí),Vmin < VOUT < VOL

在VIL

如果在后一級的判斷電路把低于VOL電壓判斷為0,把高于VOH的電壓判斷為1,那么在輸入VIL–VLH這個(gè)范圍的電壓產(chǎn)生的VOUT后一級電路就不能判斷當(dāng)前是0還是1,有可能是0,有可能是1,不能準(zhǔn)確預(yù)測它的輸出。

實(shí)際情況下,沒有一個(gè)點(diǎn)來作為分界線,實(shí)際電路做不出來。實(shí)際上是高于VH才算1,低于VL才算0,VH>VL,也就是說高閾值VH和VL之間是由一段距離的。

當(dāng)輸入數(shù)據(jù)不滿足寄存器的建立時(shí)間和保持時(shí)間的時(shí)候,寄存器很可能捕捉到輸入數(shù)據(jù)的電平在未定義的電平區(qū)間,就是亞穩(wěn)態(tài)。

不是每個(gè)違反寄存器建立時(shí)間和保持時(shí)間的信號翻轉(zhuǎn)都會導(dǎo)致亞穩(wěn)態(tài)。一個(gè)寄存器進(jìn)入亞穩(wěn)態(tài)和從亞穩(wěn)態(tài)進(jìn)入穩(wěn)態(tài)的時(shí)間依賴與制造商的制造工藝和使用環(huán)境。大部分情況下,寄存器會很快的進(jìn)入一個(gè)定義的穩(wěn)態(tài)中。

亞穩(wěn)態(tài)的危害

由于亞穩(wěn)態(tài)的輸出在穩(wěn)定下來之前可能是毛刺、振蕩、固定的某一電壓值,因此亞穩(wěn)態(tài)除了導(dǎo)致邏輯誤判之外,輸出在0~1之間的中間電壓值還會使下一級產(chǎn)生亞穩(wěn)態(tài)(導(dǎo)致亞穩(wěn)態(tài)的傳播)。邏輯誤判有可能通過電路的特殊設(shè)計(jì)減輕危害,亞穩(wěn)態(tài)的傳播擴(kuò)大了故障面,難以處理。

電平信號的邏輯誤判一般只會對電路造成幾個(gè)時(shí)鐘的延時(shí),后面還會穩(wěn)定在需要的電平,不會造成邏輯錯(cuò)誤。

亞穩(wěn)態(tài)信號的穩(wěn)定時(shí)間通常比一個(gè)時(shí)鐘周期要短的多。一般情況下不會超過一個(gè)或者兩個(gè)周期,取決于觸發(fā)器的性能。

如果亞穩(wěn)態(tài)超過一個(gè)或者兩個(gè)周期,那么就會被下一個(gè)觸發(fā)器采樣到,這樣就會造成亞穩(wěn)態(tài)的傳播。

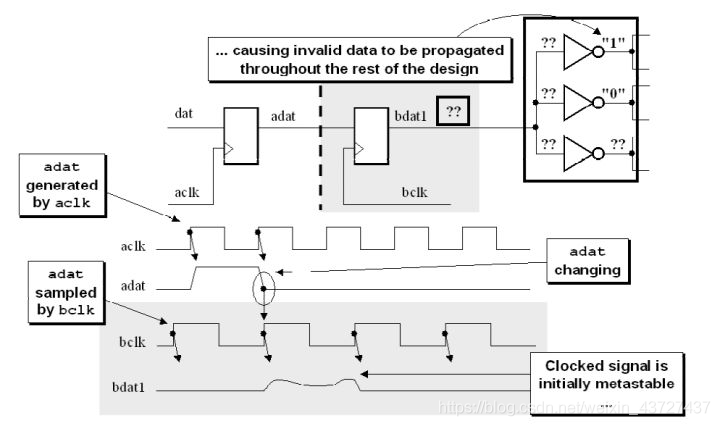

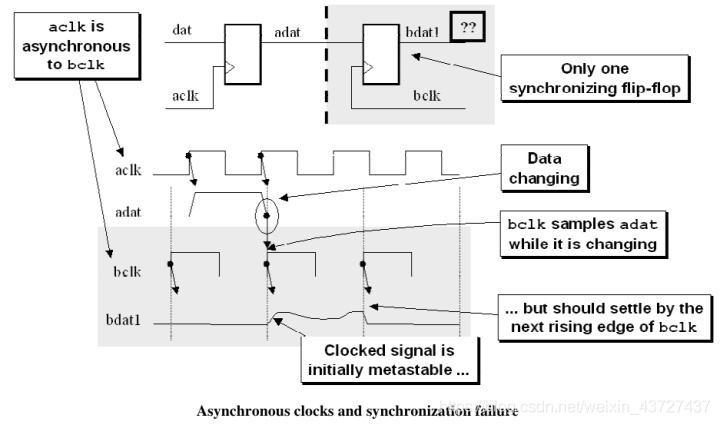

上圖的bdat1的亞穩(wěn)態(tài)在下一個(gè)時(shí)鐘沿還沒穩(wěn)定,就造成了亞穩(wěn)態(tài)的傳播。這里可以選擇更快的觸發(fā)器,減少亞穩(wěn)態(tài)收斂的時(shí)間。

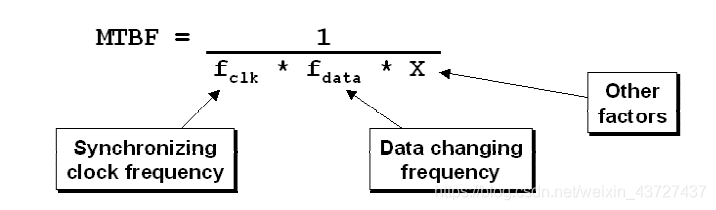

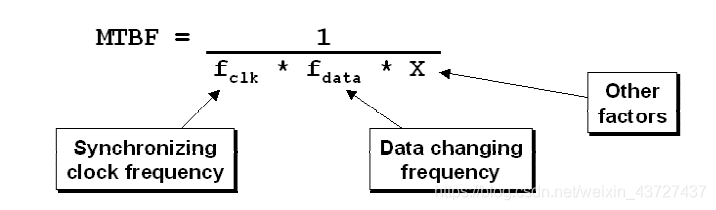

亞穩(wěn)態(tài)的量化公式

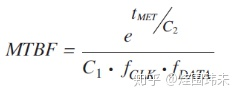

設(shè)計(jì)人員采用平均故障間隔時(shí)間(MTBF:mean-time-between-failure)這個(gè)指標(biāo)來估算從問題出現(xiàn)并導(dǎo)致故障的兩個(gè)事件間的平均時(shí)間。MTBF越高,說明設(shè)計(jì)的穩(wěn)定性越好。如果發(fā)生了故障,只是說明沒有解決亞穩(wěn)態(tài)的問題,并不是系統(tǒng)本身真的出現(xiàn)了問題。

C1和C2代表器件的相關(guān)的常數(shù),器件的建立時(shí)間和保持時(shí)間越小,C2越小,MTBF就越大。所以可以通過更快的觸發(fā)器,來減少亞穩(wěn)態(tài)發(fā)生的概率。

數(shù)據(jù)變化頻率越小,采樣時(shí)鐘越低,MTBF越大。

減少亞穩(wěn)態(tài)的方法

亞穩(wěn)態(tài)是不可避免的,是器件的固有屬性。可以減少亞穩(wěn)態(tài)的發(fā)生和傳播,避免亞穩(wěn)態(tài)帶來的消極影響。

減少亞穩(wěn)態(tài)的方法有以下幾種:

(1)使用同步器:比如常用的2級或者多級FF打拍的方法

(2)降低頻率:如果能滿足功能要求,降低頻率能夠減少亞穩(wěn)態(tài)的發(fā)生。

(3)避免變化過快或者過于頻繁的信號進(jìn)行跨時(shí)鐘采樣。

(4)采用更快的觸發(fā)器:更快的觸發(fā)器,也可以亞穩(wěn)態(tài)的產(chǎn)生

同步器

信號跨時(shí)鐘邊界,一般有兩種場景:

(1)信號跨時(shí)鐘邊界,可以漏掉某些值

(2)信號跨時(shí)鐘邊界,不能漏掉任何值

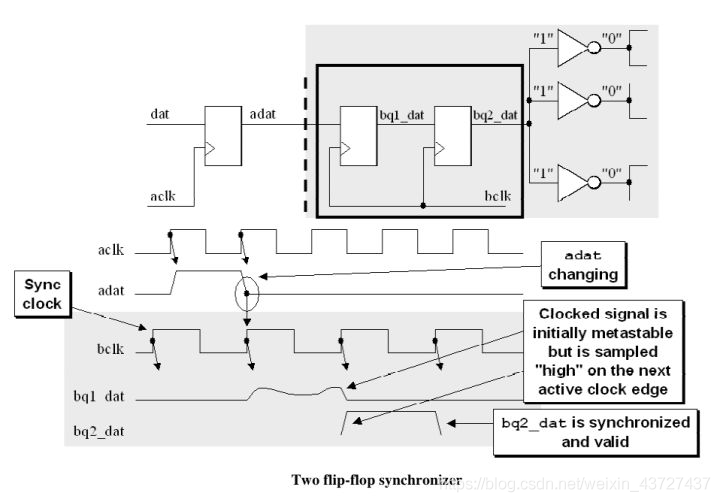

兩級觸發(fā)同步器

(1)如果亞穩(wěn)態(tài)維持的時(shí)間不止一個(gè)周期,在下一個(gè)時(shí)鐘上升沿沒有穩(wěn)定,那么第二級的FF也會進(jìn)入亞穩(wěn)態(tài),這種情況的概率是1/MTBF

(2)第一級亞穩(wěn)態(tài)在下一個(gè)時(shí)鐘上升沿穩(wěn)定,但是被是識別為0,那么第二級的FF輸出bq2_dat就是0,說明信號跨時(shí)鐘采樣失敗。但是這種情況不會造成亞穩(wěn)態(tài)的傳播,也就是不會影響后面的設(shè)計(jì)。針對這種情況,一般會改變設(shè)計(jì),不會讓快時(shí)鐘域的單cycle脈沖,跨時(shí)鐘到慢的時(shí)鐘內(nèi)采樣。

三級或多級同步器

在高速、超高速設(shè)計(jì)中,兩級的MTBF可能還不夠,為了保險(xiǎn)會采樣三級或多級同步器。

3級FF的MTBF是2級FF的MTBF的7倍。

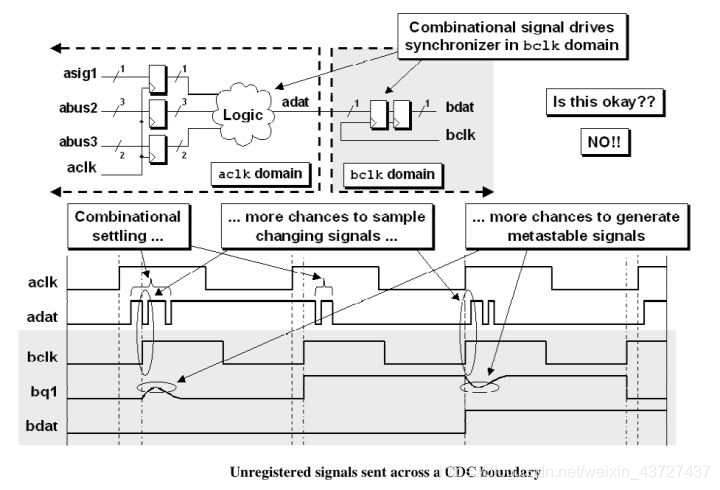

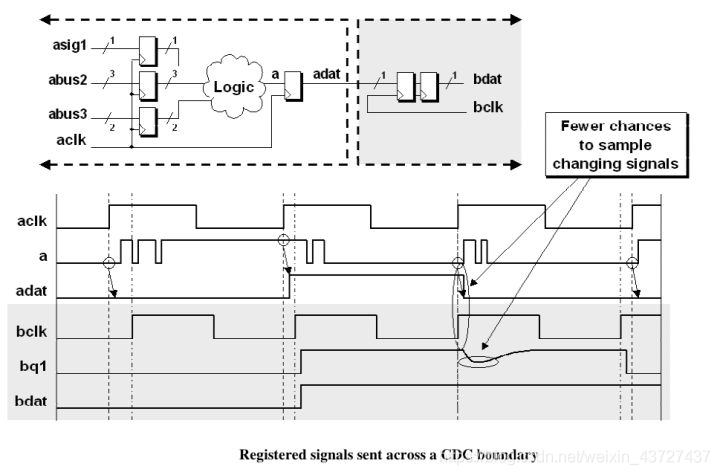

同步器的輸入:源時(shí)鐘寄存

采用同步器的另外一個(gè)要求:通常,需要跨時(shí)鐘的信號,需要在源時(shí)鐘經(jīng)過一級FF進(jìn)行寄存輸出。即,跨時(shí)鐘信號必須是寄存器的輸出,中間不能有組合邏輯。如果輸入不是寄存器的輸出,是組合邏輯的輸出,會是如下情況:

可以看到,adat是組合邏輯的輸出,變化的頻率更快了,根據(jù)MTBF公式:

數(shù)據(jù)變化太快,會減少M(fèi)TBF,增加亞穩(wěn)態(tài)發(fā)生的概率。如果adat是FF的輸出,根據(jù)FF的特性,輸出在一個(gè)時(shí)鐘周期內(nèi)是不會改變的,數(shù)據(jù)的變化頻率不會超過時(shí)鐘頻率,這樣就能降低跨時(shí)鐘信號變化的頻率,減少亞穩(wěn)態(tài)發(fā)生的概率:

在使用同步信號時(shí),要求理解了其中的原理,要求輸入信號必須是源時(shí)鐘域的寄存器輸出。

2. 跨時(shí)鐘信號處理方法

跨時(shí)鐘域的信號可以分為單bit信號和多bit信號。

單bit信號跨時(shí)鐘域的處理

信號跨時(shí)鐘域,根據(jù)兩個(gè)異步時(shí)鐘之間的關(guān)系可以分為:

(1)信號從快時(shí)鐘域到慢時(shí)鐘域

(2)信號從慢時(shí)鐘域到快時(shí)鐘域

單bit信號一般采用同步器來做CDC(clock domain crossing)。由于在CDC時(shí),會在源時(shí)鐘域做寄存器輸出,所以信號的變化頻率不會超過源時(shí)鐘的頻率,所以這里可用兩個(gè)時(shí)鐘間的快慢來分類。

快時(shí)鐘域到慢時(shí)鐘域

信號從快時(shí)鐘域到慢時(shí)鐘域CDC如下圖所示:

當(dāng)在aclk中生成的信號adat被送到了另一個(gè)時(shí)鐘域bclk中采樣,由于采樣時(shí)間太靠近第二個(gè)時(shí)鐘的上升沿,發(fā)生的同步失敗。同步失敗是由于輸出bdat1變?yōu)閬喎€(wěn)態(tài),而在bdat1再次被采樣時(shí)沒有收斂到合法的穩(wěn)定狀態(tài)。

如果是電平信號進(jìn)行CDC,不用考慮時(shí)鐘快慢,直接用同步器就可以,因?yàn)榭偰鼙徊蓸拥健?/p>

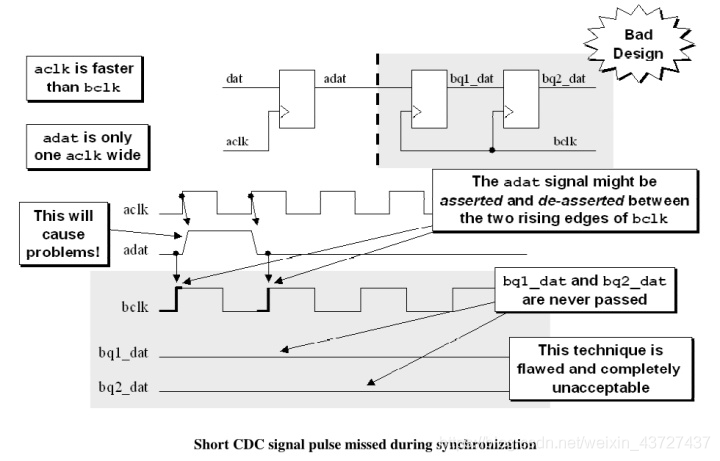

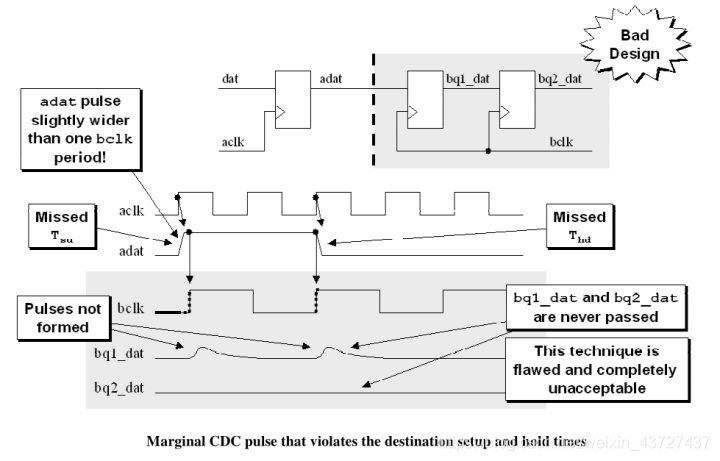

快時(shí)鐘到慢時(shí)鐘的(單bit)信號處理,主要問題是信號在快時(shí)鐘域中,可能會多次改變,這樣慢是可能來不及采樣導(dǎo)致數(shù)據(jù)丟失。這個(gè)問題被稱為信號寬度問題,在CDC檢查工具中,如果快時(shí)鐘的信號寬度不足,就會報(bào)出CDC違例。

快時(shí)鐘到慢時(shí)鐘的(單bit)信號處理分為兩種:

(1)采樣丟失是被允許的。單bit信號一般不會是這種情況,如果是,直接用同步器同步就行。

(2)采樣丟失不被允許。這樣就用其他手段來保證數(shù)據(jù)不丟失。主要原理是保證快時(shí)鐘與的信號寬度滿足一定的條件,使得慢時(shí)鐘域有足夠時(shí)間采樣到。

信號寬度的“三時(shí)鐘沿”要求

比較安全的寬度是,快時(shí)鐘域的信號寬度必須是慢時(shí)鐘域周期的1.5倍以上。也就是要持續(xù)3個(gè)時(shí)鐘沿以上(上升沿和下降沿都算)。這個(gè)被稱為“三時(shí)鐘沿”要求。

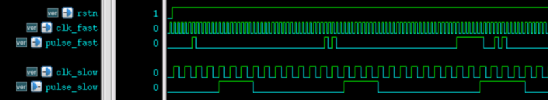

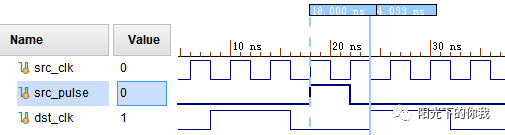

下面是一個(gè)CDC信號只持續(xù)一個(gè)周期的例子:

發(fā)送時(shí)鐘域的頻率高于接收時(shí)鐘域,而CDC脈沖在發(fā)送時(shí)鐘域只有一個(gè)周期寬,這樣CDC信號可以在慢時(shí)鐘上升沿之間變動,不會被捕獲到慢時(shí)鐘域。

如果CDC信號寬度超過慢時(shí)鐘周期,但是不足1.5個(gè)周期,也會發(fā)生問題。

如上圖所示,信號寬度超過了一個(gè)慢時(shí)鐘周期,但是可能會setup和hold time違例,導(dǎo)致信號采樣失敗。

信號寬度問題的解決方法:

通過保證信號寬度滿足超過慢時(shí)鐘周期的1.5倍,來解決這個(gè)問題,這是最直接,也是跨時(shí)鐘最快的方法。可以通過system verilog加“斷言”的方式來檢測是否滿足條件。

但實(shí)際中很少用這種方法,因?yàn)樵O(shè)計(jì)可能會變,設(shè)計(jì)人員在改變設(shè)計(jì)時(shí),可能會忘記這個(gè)限制。

所以,通常還是通過“握手”的方式來保證數(shù)據(jù)被采樣到。

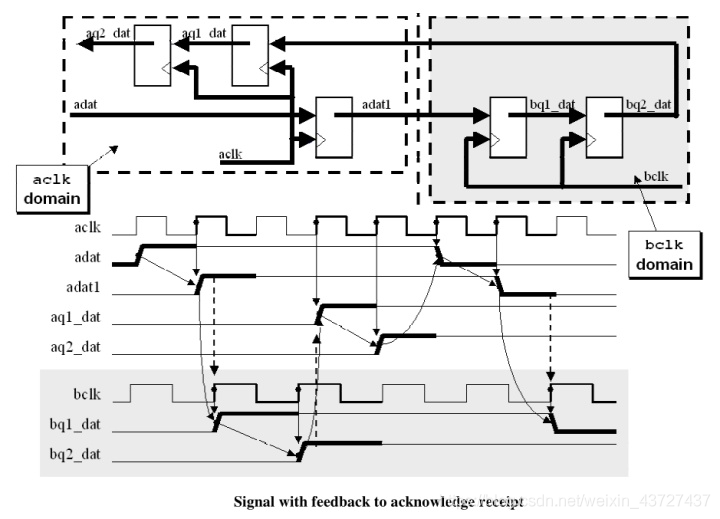

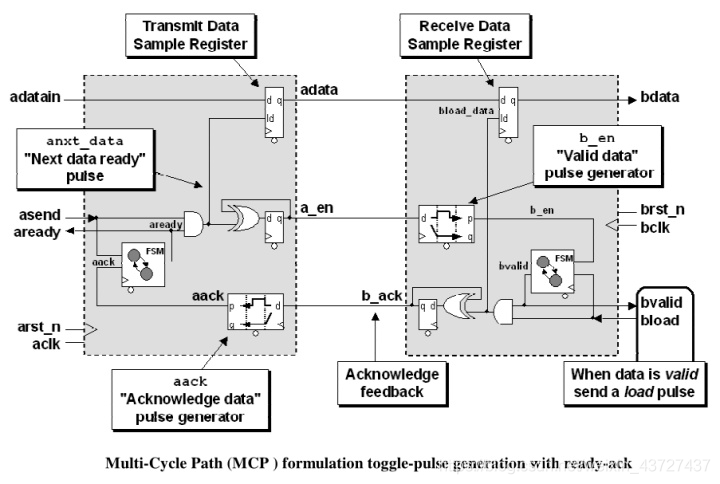

通常的做法是:發(fā)送一個(gè)使能控制限號,將它同步到新的時(shí)鐘域,然后通過另一個(gè)同步器將同步信號作為確認(rèn)信號作為確認(rèn)信號傳回發(fā)送時(shí)鐘域,如下圖所示:

優(yōu)點(diǎn):

同步反饋信號是一種非常安全的技術(shù),可以識別第一個(gè)控制信號并將其采樣到新的時(shí)鐘域中。

缺點(diǎn):

在允許控制信號改變之前,在兩個(gè)方向上同步控制信號有相當(dāng)大的延遲。也就是時(shí)候,在應(yīng)答信號到來之前,是不允許源信號改變的。

在實(shí)際的芯片設(shè)計(jì)中,脈沖(寬度有限)信號的同步都是采用這種握手機(jī)制來處理。

慢時(shí)鐘到快時(shí)鐘域

慢時(shí)鐘域到快時(shí)鐘域的CDC,直接使用信號同步器就可以了。

目標(biāo)時(shí)鐘頻率必須是源時(shí)鐘頻率1.5倍或者以上,才能算慢時(shí)鐘到快時(shí)鐘的CDC。

只有滿足快1.5倍以上,才能滿足“三時(shí)鐘沿要求”。才能保證快時(shí)鐘域能夠采樣到慢時(shí)鐘域的脈沖。

如果目標(biāo)時(shí)鐘域只快一點(diǎn),為保險(xiǎn)起見,還是用握手機(jī)制。

有的設(shè)計(jì)中為了保險(xiǎn)和以后修改的方便,或者不清楚時(shí)鐘之間的關(guān)系,都會按照握手機(jī)制來處理。

多個(gè)信號跨時(shí)鐘的處理

不同同步器的芯片上的走線也可能不同,導(dǎo)致延時(shí)不一樣。會導(dǎo)致后端走線難度增大。

在CDC檢查的時(shí)候,會有專門的規(guī)則來檢查是否采樣了多bit信號用同步器聚合使用的情況。

多個(gè)信號CDC策略可以分為以下幾種:

(1)多個(gè)信號合并,在可能的情況下,將多個(gè)CDC合并為1位的CDC信號

(2)多周期路徑發(fā)。使用同步負(fù)載信號安全地傳遞多個(gè)CDC位。

(3)使用格雷碼傳遞多個(gè)CDC位。

(4)使用異步FIFO來傳遞多位信號

(5)使用DMUX電路結(jié)構(gòu)進(jìn)行多位信號傳遞

多個(gè)信號合并

有時(shí)候并不需要將多個(gè)信號做CDC。下面是將兩個(gè)信號合并為1位信號做CDC。

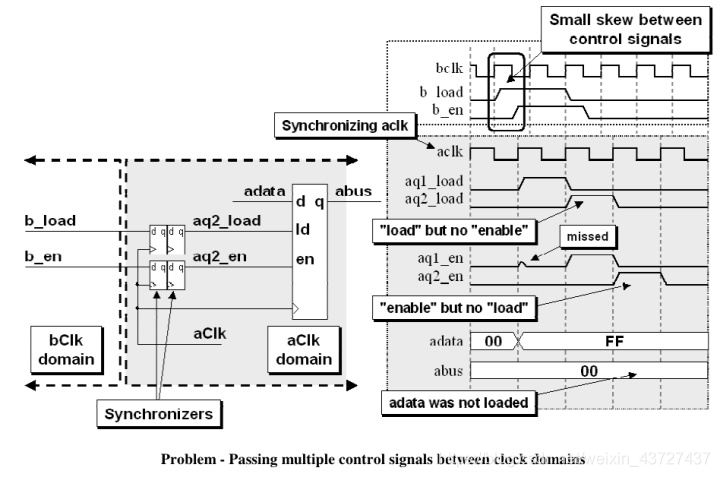

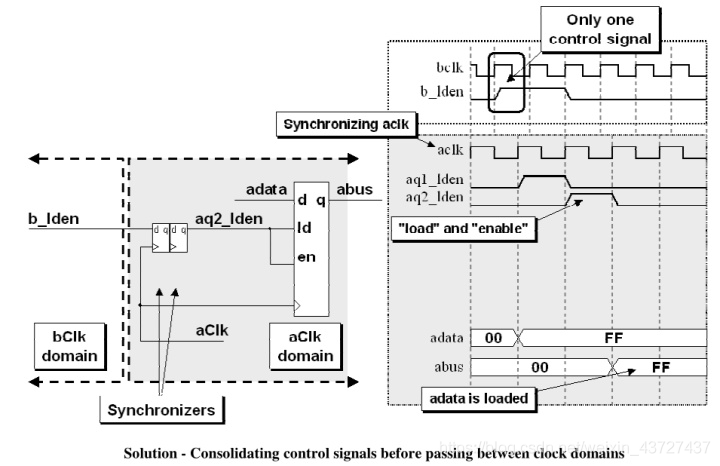

下圖中,接收時(shí)鐘域中的寄存器需要加載信號和使能信號崔你那個(gè)將數(shù)據(jù)值加載到急促器中。如果負(fù)載和使能信號都是在同一個(gè)發(fā)送時(shí)鐘邊緣上驅(qū)動的。那么控制信號之間的小偏差就有可能導(dǎo)致兩個(gè)信號在接收時(shí)鐘域中同步到不同的時(shí)鐘周期。在這種情下,數(shù)據(jù)不會被加載到寄存器中,就會出問題。

解決方法是,將控制吸納后b_load和b_en合起來;b_lden = b_load & b_en同步到aclk時(shí)鐘域中。

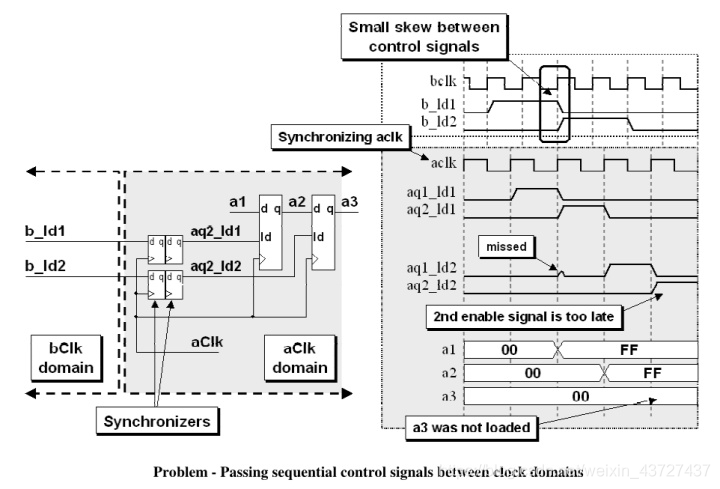

下面這個(gè)例子中,顯示了兩個(gè)使能信號,aen1和aen2,它們從發(fā)送時(shí)鐘域依次驅(qū)動到接收時(shí)鐘域,以控制流水線數(shù)據(jù)寄存器的使能輸入。問題是同步器并不能保證兩個(gè)cycle一定能同步過來,下面的同步器花了3個(gè)cycle才tongue完成數(shù)據(jù),導(dǎo)致流水線寄存器不能“流水”起來。

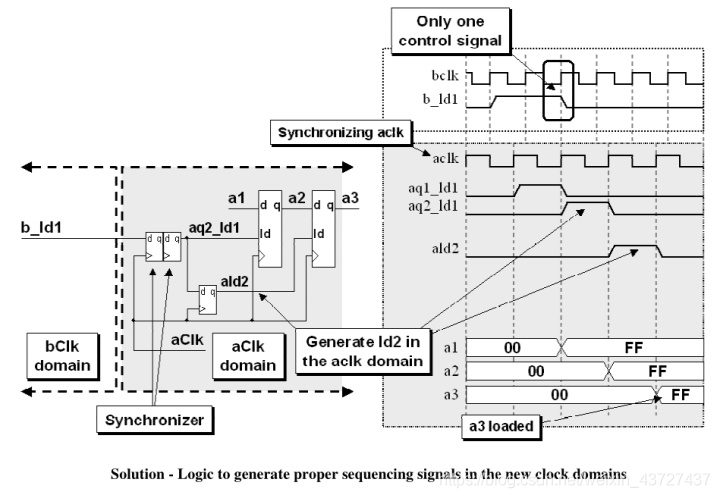

該問題的解決方案是只向接收時(shí)鐘域發(fā)送一個(gè)控制信號,并在接收時(shí)鐘域內(nèi)生成第二個(gè)相移流水線使能信號。

多周期路徑(Multi-Cycle Path,MCP)

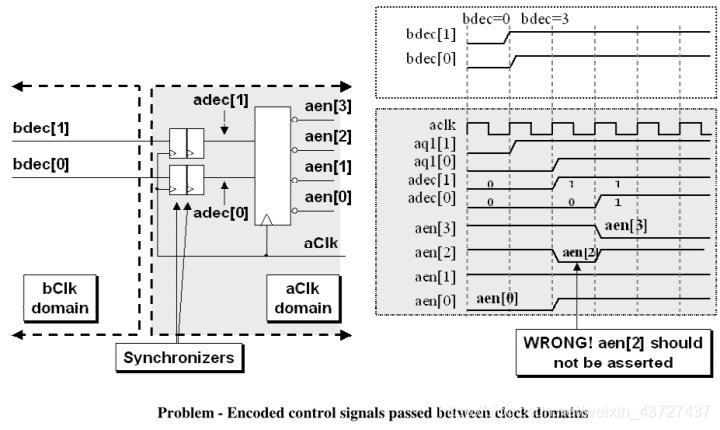

下圖顯示在時(shí)鐘域之間傳遞兩個(gè)編碼控制信號。如果這兩個(gè)編碼信號在采樣時(shí)略有偏差,則在接收時(shí)鐘域中的一個(gè)時(shí)鐘周期內(nèi)可能會產(chǎn)生錯(cuò)誤的解碼輸出。

多位數(shù)據(jù)問題可以用“多周期路徑法(MCP)”來解決。

MCP方法是指直接不同步將數(shù)據(jù)發(fā)生到目標(biāo)時(shí)鐘域,但是同時(shí)送一個(gè)同步過的控制信號到目標(biāo)時(shí)鐘域。數(shù)據(jù)和控制信同時(shí)發(fā)送,允許數(shù)據(jù)在目標(biāo)寄存器的輸入端進(jìn)行設(shè)置,同時(shí)控制信號在到達(dá)目標(biāo)寄存器的負(fù)載輸入端之前做同步。

MCP優(yōu)點(diǎn):

(1)不需要在發(fā)送時(shí)鐘域計(jì)算適當(dāng)?shù)拿}沖寬度

(2)發(fā)送時(shí)鐘域只需要將enable toggle到接收時(shí)鐘域,表示數(shù)據(jù)已經(jīng)被傳遞完成,已經(jīng)準(zhǔn)備好被加載,使能吸納后不需要返回到初始邏輯電平。

MCP方法的實(shí)質(zhì)是,不同步多位的數(shù)據(jù),只同步一位的控制信號,通過握手保證控制信號能夠正確傳輸,然后在目標(biāo)時(shí)鐘域通過控制信號來采樣數(shù)據(jù)。

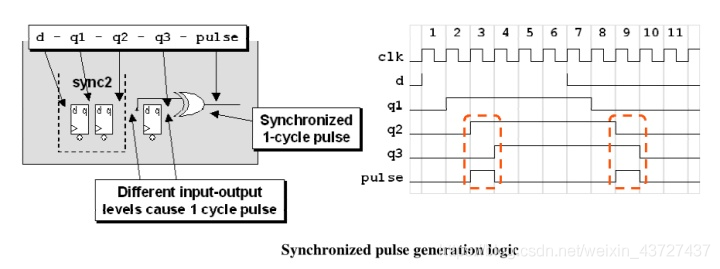

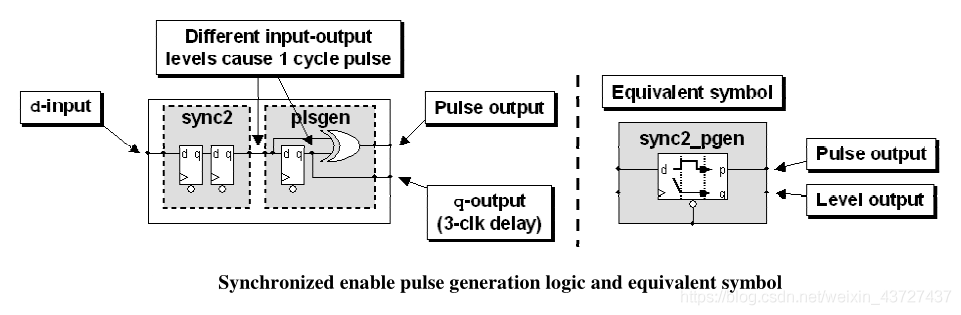

MCP需要用到“同步脈沖器”:

同步脈沖器的符號表示如下:

多周期路徑法有兩種方法來傳遞多位信號:

多周期路徑法的思想十分有用,但是實(shí)際中用來傳遞多位信號比較少見,因?yàn)檫壿嬤^于復(fù)雜。但是MCP方法用來傳遞單bit的信號卻十分有用。

格雷碼

對于計(jì)數(shù)器的CDC,大部分是不需要的,如果需要,那就使用格雷碼。

格雷碼每次只允許更改一個(gè)位,從而消除了跨時(shí)鐘域同步更改多個(gè)CDC位所帶來的問題。

需要注意的是:格雷碼必須是計(jì)數(shù)到2^n才是每次改變一個(gè)bit。

如果計(jì)數(shù)器是從0-5計(jì)數(shù),那么從5–0的計(jì)數(shù)就不止一個(gè)bit改變,就失去了只改變一個(gè)bit的初衷。

格雷碼最常見的應(yīng)用是在異步fifo中,通常異步fifo的深度都是2^N。原因如上,就算浪費(fèi)面積,也需要把FIFO深度設(shè)置為2 ^ N.

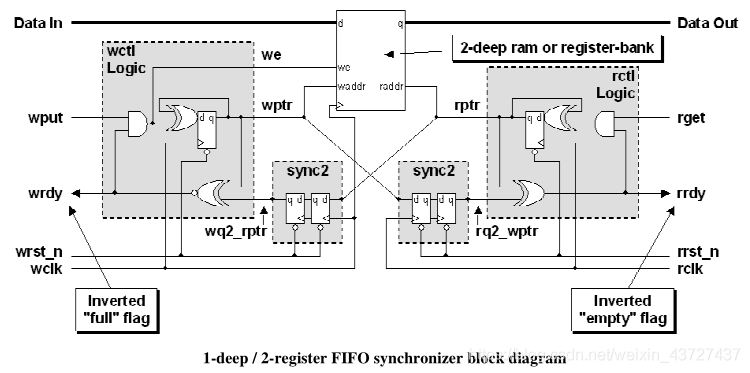

異步FIFO(AFIFO)

就是深度為2的AFIFO,來進(jìn)行多bit數(shù)據(jù)的CDC. 如下圖所示:

2個(gè)寄存器搭建的AFIFO,地址只需要一位。相比MCP方法,邏輯簡單,可以復(fù)用AFIFO代碼(一般公司都有芯片驗(yàn)證過的AFIFO代碼),而且延時(shí)也比MCP方法小。

DMUX(數(shù)據(jù)分配器)

有一個(gè)輸入端和多個(gè)輸出端1,其邏輯功能是一個(gè)輸入端的信號發(fā)送到多個(gè)輸出端中某一個(gè),簡稱DMUX,作用與MUX正好相反。

3.SpyGlass CDC流程

數(shù)字電路的集成度越來越高,設(shè)計(jì)也就越復(fù)雜。系統(tǒng)很少都只工作在一個(gè)時(shí)鐘頻率之下。一個(gè)系統(tǒng)中往往會存在多個(gè)時(shí)鐘,這些時(shí)鐘之間有可能是同步的,也有可能是異步的。一個(gè)系統(tǒng)中,異步時(shí)鐘之間存在信號通道,則就會存在CDC(clock domain crossign)。

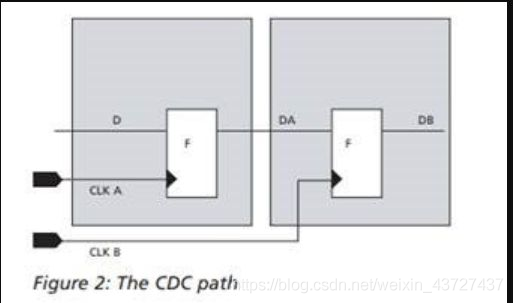

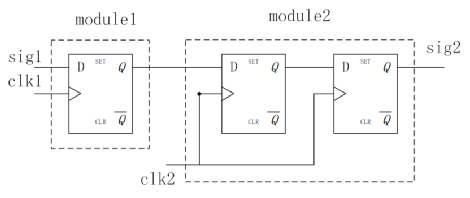

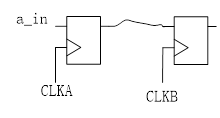

下圖中,CLKA和CLKB之間沒有固定的相位關(guān)系,是異步時(shí)鐘。前半部分設(shè)計(jì)屬于時(shí)鐘域CLKA,后半部分設(shè)計(jì)屬于時(shí)鐘域CLKB。DA信號從時(shí)鐘域CLKA進(jìn)入到時(shí)鐘域CLKB,是一個(gè)跨時(shí)鐘域的信號,這條路徑被稱為CDC path。

CDC(Clock Domain Crossing)是前端設(shè)計(jì)中最常見的問題。在RTL中要恰當(dāng)?shù)奶幚砻總€(gè)異步的控制信號和數(shù)據(jù)信號,否則就會出現(xiàn)亞穩(wěn)態(tài),造成嚴(yán)重的function false。

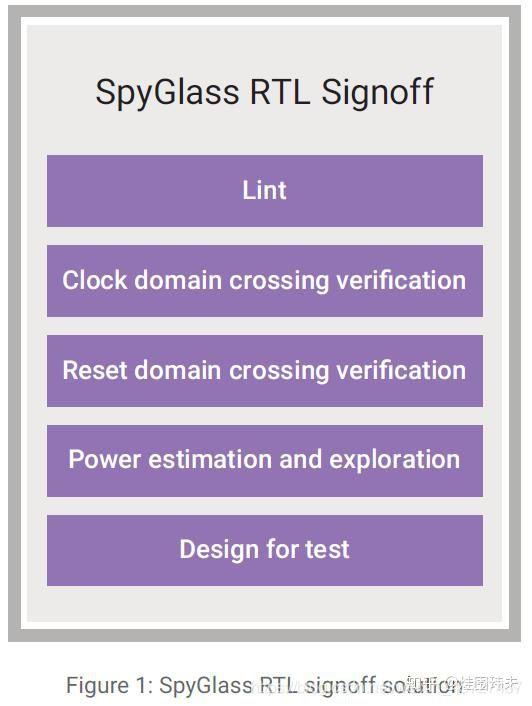

SpyGalss是目前業(yè)界唯一可靠的RTL Sign off解決方案,可以幫助客戶在設(shè)計(jì)早起發(fā)現(xiàn)潛在問題,保住產(chǎn)品質(zhì)量,極大的減少設(shè)計(jì)風(fēng)險(xiǎn),降低設(shè)計(jì)成本。

包括五大模塊:lint,CDC(跨時(shí)鐘域檢查),LP(低功耗),Constraint(約束),DFT(可測試性)。

SpyGlass CDC分析使你能夠識別設(shè)計(jì)中的CDC問題。SpyGlass CDC tool是中Formal Check Methodology工具,相比寫case跑仿真來找CDC問題,靠SpyGlass能更早,更全,更快的發(fā)現(xiàn)CDC問題。它能夠:

(1)管理是多時(shí)鐘域設(shè)計(jì)

(2)系統(tǒng)地處理CDC問題

(3)檢查和報(bào)告任何不同步的信號:時(shí)鐘和復(fù)位

SpyGlass CDC與靜態(tài)時(shí)序分析相比:

(1)STA對async interface不太好使,只適合sync模塊分析

(2)CDC paths總是需要設(shè)置成false paths

(3)一般在design的后期能在netlist level做才有意義

SpyGlass CDC與功能仿真相比:

(1)黑盒測試很難窮舉

(2)白盒測試需要assertions

(3)需要覆蓋CDC的所有test branches

(4)很難幸運(yùn)的覆蓋所有,一般只能發(fā)現(xiàn)部分問題

(5)一般在design后期才發(fā)現(xiàn)問題

當(dāng)soc design設(shè)計(jì)的clock domain太多,用到很多第三方IP,及設(shè)計(jì)人員水平參差不齊時(shí),用SpyGlass CDC來檢查保證RTL質(zhì)量是十分必要的。

在工程的block-level和SOC集成的兩個(gè)不同階段,所用的CDC Goal也是有所不同的。Block-level關(guān)心的是模塊內(nèi)部,只有模塊內(nèi)部檢查沒問題后才能做deliver,而SOC集成主要關(guān)心的是模塊間interface 的CDC問題。

?

編輯:黃飛

電子發(fā)燒友App

電子發(fā)燒友App

評論