1、clk中為什么用posedge而不用negedge?

(1)、一般情況下,系統中統一用posedge避免用negedge,降低設計的復雜度,可減少出錯。

(2)、在modelsim仿真中,時鐘是很嚴格的,但是在真實的晶振所產生的clock卻是不嚴格的,比如高電平和低電平的時間跨度就不一樣,甚至非周期性的微小波動。如果只是用posedge,則整個系統的節拍都按照clock上升沿對齊,如果用到了negedge,則系統的節拍就沒有統一到一個點上。上升沿到上升沿肯定是一個時鐘周期,但是上升沿到下降沿卻很可能不是半個周期。

(3)、FPGA特有的東西:GLOBAL clk。FPGA內部有專門的時鐘線,和一般的邏輯門走法不一樣,目的是為了保證整個FPGA內部時鐘盡可能的偏差小。

?

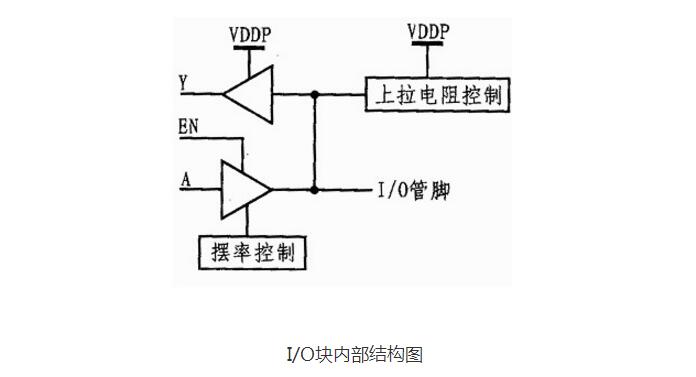

2、BANK劃分與供電策略

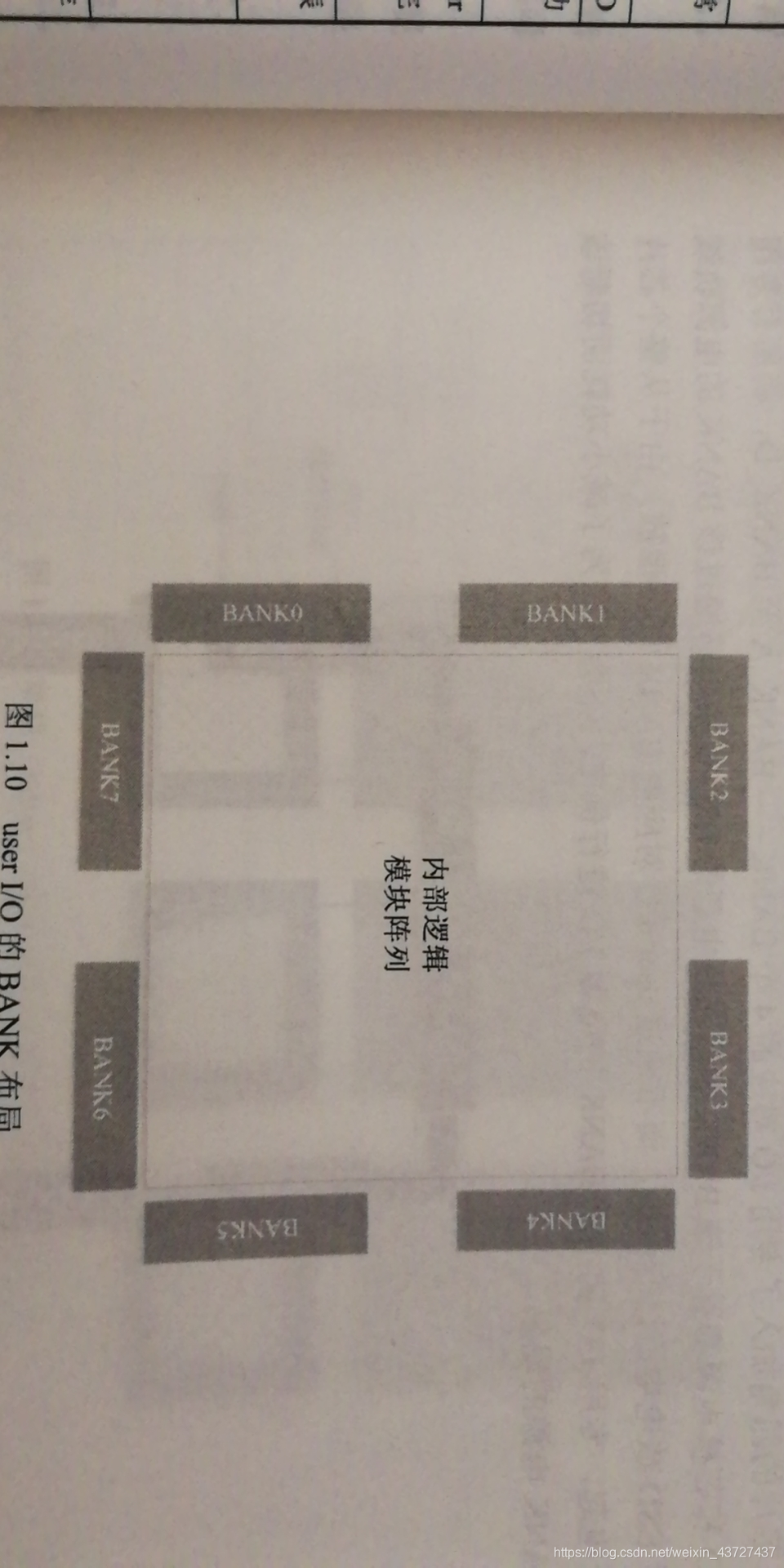

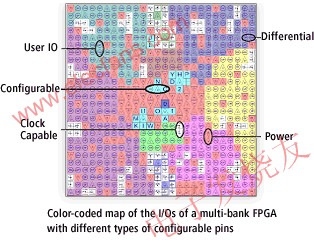

FPGA內I/O的排布是通過BANK劃分來實現的,若干user I/O與電源I/O被劃分為一個BANK。如下圖,整個芯片的user I/O被分成8個BANK。BANK與BANK之間是相互獨立的。每個BANK的user I/O可由不同電平的電源供電而不會相互影響。不同BANK的user I/O可以配置為不同的I/O標準和電平標準,提高了user I/O使用的靈活性。

?

由同一個電源供電的多個user I/O同時跳變時,會帶來相當大的瞬時動態電流。由于PAD和封裝引起的電感,這個電流可能會在電源軌線上帶來壓降,嚴重時會因邏輯電平降低而引起翻轉,使電路工作失效。

?

采用劃分BANK的方法對user I/O進行排布,可以有效改善這個問題。將FPGA中所有的user I/O劃分為多個BANK分別進行獨立的供電,用戶在編程時將使用到的user I/O配置于不同的I/O BANK,可以控制每個BANK內同時翻轉的user I/O的數量,降低瞬時的動態電流,也可以避免觸地反彈現象的出現。對于沒有使用到的BANK,還可以關閉該BANK的電源,能夠有效降低功耗。

?

FPGA中的user I/O一般通過劃分BANK的方式獨立進行供電,為保證器件在輸出電流驅動片外負載的情況下能夠正常工作,并保證ESD放電現象發生時,電源軌線不會因瞬間的高熱而熔斷燒毀,I/O的電源軌線必須滿足一定的寬度,且留有足夠金屬通孔(VLA)數量。在設計前期,由BANK內user I/O的數量、I/O最大驅動電流以及BANK內電源PAD數量對BANK內電源軌線上通過最大電流進行預估,根據Foundry提供的金屬電流密度參數,設計合理的電源軌線寬度。

?

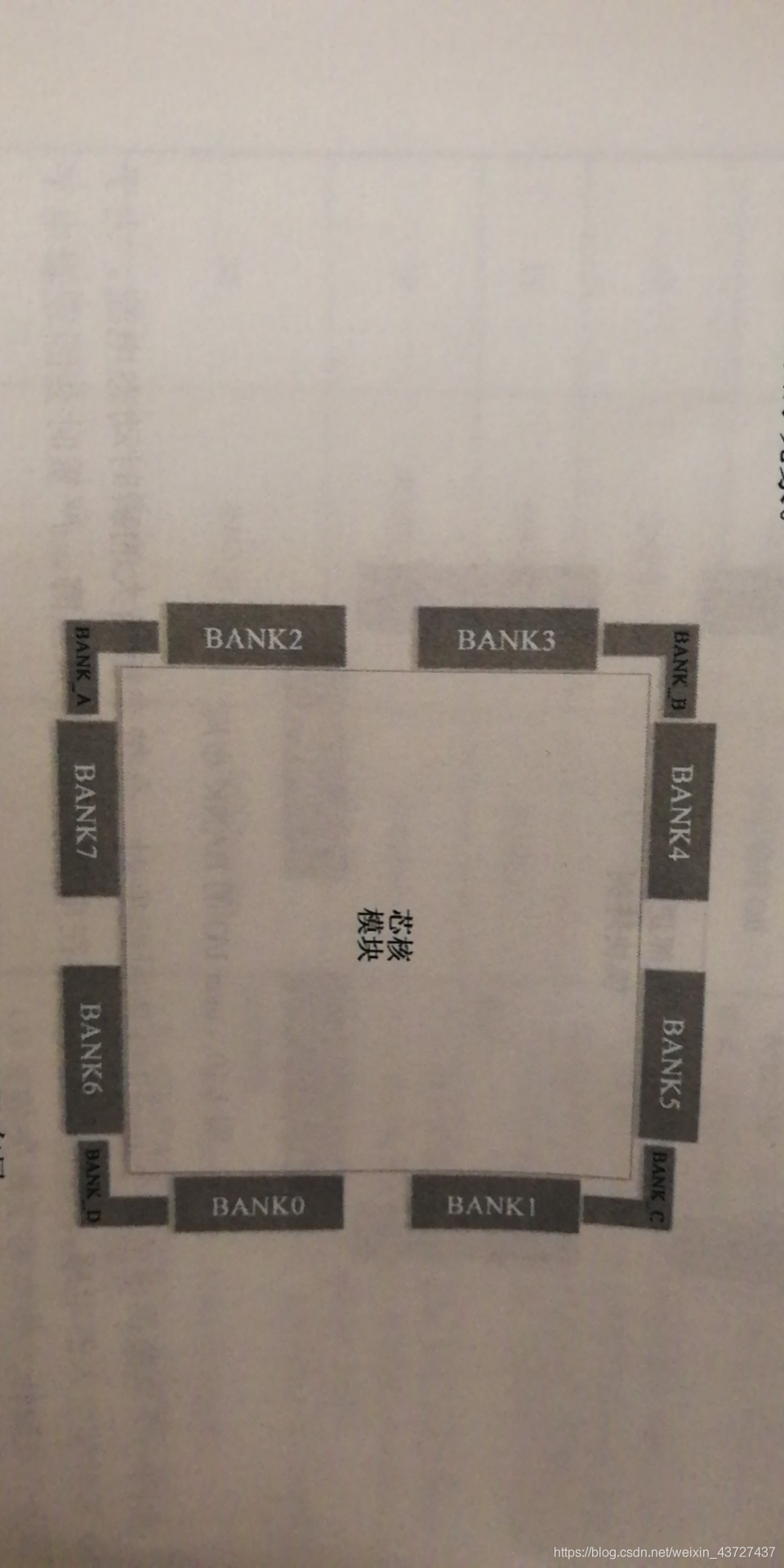

在FPGA中,一般有多個專用I/O的供電和特點,對整個FPGA芯片的BANK布局進行改造,保持user I/O的8個獨立BANK不變,在芯片的四角加入了專用I/O對應的4個BANK----BANKA-BANKD,將所有專用IO和芯核,電源都置于該BANK中,芯核電源的ESD保護電路通過該BANK的電源軌線對ESD放電電流進行泄放,而不通過user I/O對應的BANK進行泄放。由于從整個芯片上電起,專用I/O就由該BANK的電源I/O進行供電,不會存在為了減小功耗而切斷該BANK電源的現象。

3、為什么verilog HDL設計中一定要用同步而不能用異步時序邏輯?

同步時序邏輯是指狀態的寄存器組的值只可能在唯一確定的觸發條件時刻改變。只能由時鐘的正條邊沿或負跳變沿觸發的狀態機就是一例。always@(posedge clock)就是一個同步時序邏輯的觸發條件,表示由該always控制begin end塊中寄存器變量重新賦值的情形只可能是在clock正條邊沿發生。

?

而異步時序邏輯是指觸發條件由多個控制因素組成,任何一個因素的跳變都可以引起觸發。記錄狀態的寄存器組其是在輸入端不是都連接在同一個時鐘信號上。例如用一個觸發器的輸出連接到另一個觸發器的時鐘端去觸發就是異步時序邏輯。

?

用Verilog HDL設計的可綜合模塊,必須是避免使用異步時序邏輯,這不但是因為許多綜合器不支持異步時序邏輯的綜合,而且也因為用異步時序邏輯確實難以控制由組合邏輯和延遲所產生的冒險和競爭。當電路復雜度增加時,異步時序邏輯無法調試。工藝的細微變化也會造成異步時序邏輯電路的失效。因為異步時序邏輯中觸發條件很隨意,任何時刻都有可能發生,所以記錄狀態的寄存器組的輸出在任何時刻都有可能發生變化。而同步時序邏輯中的觸發輸入至少可以維持一個時鐘后才會發生第二次觸發。這是一個非常重要的差別,因為我們利用這一個時鐘的時間在下一次觸發信號到來前,為電路狀態的改變創造一個穩定可靠的條件。

?

因為我們可以得出結論:同步時序邏輯比異步時序邏輯具有更可靠更簡單的邏輯關系。如果我們強行做出規定,用Verilog來設計可綜合的狀態機必須使用同步時序邏輯,有了這個前提條件,實現自動生成電路結構的綜合器有了可能。一碗這樣大大減少了綜合工具的復雜度。

?

同步、異步時序邏輯的差異:

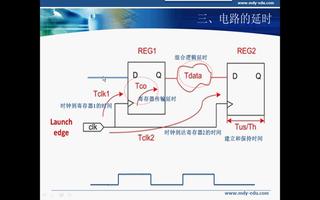

在同步邏輯電路中,觸發信號是時鐘的正跳變沿(或負跳變沿);觸發器的輸入與輸出是經由兩個時鐘來完成的。第一個時鐘的正跳沿(或負跳沿)為輸入做準備,在第一個時鐘正跳沿(或負跳沿)到來后到第二個時鐘正跳沿(負跳沿)到來之前這段時間內,有足夠的時間使輸入穩定。當第二個時鐘正跳沿(負跳沿)到來時刻,由前一個時鐘沿創造的條件已經穩定,所以能夠使下一個狀態正確地輸出。

?

若在同一時鐘的正跳沿(負跳沿)下對寄存器組既進行輸入又進行輸出,很有可能由于門的延遲使輸入條件還未確定時,就輸出了下一個狀態,這種情況會導致邏輯紊亂。

而利用上一個時鐘為下一個時鐘創造的觸發條件是安全可靠的。前提是:確定下一個狀態所使用的組合電路的延遲與時鐘到各觸發器餓的差值必須小于一個時鐘周期的寬度。只有滿足這一前提才可以避免邏輯紊亂。實際電路中有以下幾點可以保證這一條件成立:

(1)、全局時鐘時鐘網絡布線時盡量各分支的時鐘一致;

(2)、應平衡樹結構,在每一級加入緩沖器,使到達每個觸發器時鐘端的時鐘同步。

?

通過這些措施基本可以保證時鐘的同步,在后仿真時,若邏輯與預期設計的不一樣,可降低時鐘頻率,就有可能消除由時鐘過快引起的觸發器輸入端由延遲和冒險競爭造成的不穩定從而使邏輯正確。

?

在組合邏輯電路中,多路信號的輸入使各信號在同時變化時很容易產生競爭冒險,從而結果難以預料。

?

4、function and task

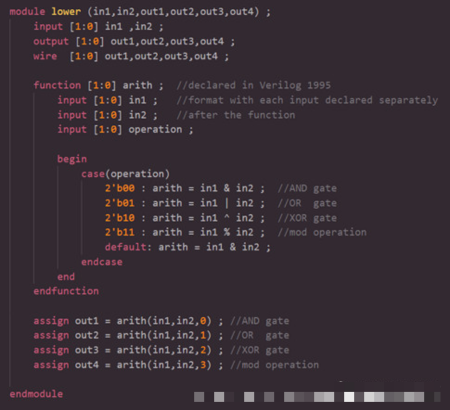

function的邏輯被綜合成了什么?

?

由于function中沒有任何時序結構,function只能綜合出組合邏輯。

?

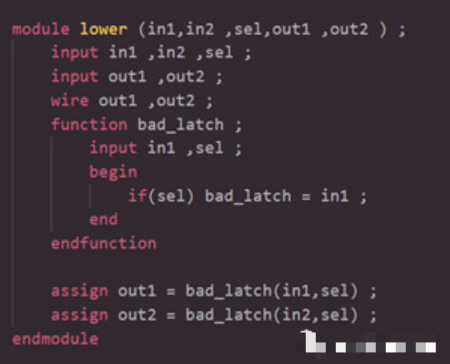

每次調用function時,局部變量和返回值都被賦值,否則將導致形成鎖存器。例如,以下示例中,if條件語句沒有else語句。也就是說,如果sel是false,該function將返回其先前調用的值,就好像結果被鎖存住了。

fucntion只用于綜合成組合邏輯。但是,fucntion的最終結果可以用作D觸發器的輸入。

fucntion不應包括延遲(#)或事件控制(@,wait)語句。

fucntion可以調用其他fucntion,但不能調用task。

fucntion在調用時會返回一個值。

?

雖然在task中可以有@等時序控制結構中,它僅適用于仿真。綜合工具會忽略所有task中的時序結構。因此,如果task中存在時序控制結構,可能會存在仿真和綜合不匹配的現象。

因此,在可綜合verilog中一般只會使用task綜合基本的組合邏輯,在testbench中調用帶有時序控制結構的task具有較好的通用性。

?

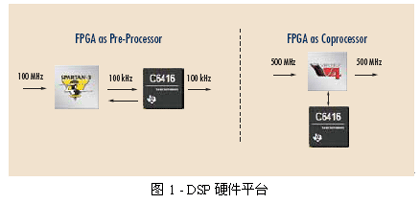

5、FPGA設計技巧

DSP:實際上就是乘加器,FPGA內部可以集成多個乘加器,而一般的DSP芯片往往每個core只有一個。換言之,FPGA可以更容易實現多個DSP core功能。在某些需要大量乘加計算的場合,往往多個乘加器并行工作的速度可以遠遠超過一個高速乘加器。

SERDES:高速串行接口。將來PCI-E、XAUI、HT、S-ATA等高速串行接口會越來越多。有了SERDES模塊,FPGA可以很容易將這些高速串行接口集成進來,無需再購買專門的接口芯片。

CPU core:分為2種,軟core和硬core。軟core是用邏輯代碼寫的CPU模塊,可以在任何資源足夠的FPGA中實現,使用非常靈活。而且在大容量的FPGA中還可以集成多個軟core,實現多核并行處理。硬core是在特定的FPGA內部做好的CPU core,優點是速度快、性能好,缺點是不夠靈活。

?

FPGA設計技巧(1):時鐘樹

對于FPGA設計來說,要盡可能的避免異步設計,盡可能的采用同步設計。同步設計的第一個關鍵是時鐘樹。時鐘樹的設計原則如下:

(1)盡可能采用單一時鐘

(2)如果有多個時鐘域,注意時鐘域的劃分

(3)跨時鐘域的信號一定要做同步處理。對于控制信號,可以采用雙采樣;對于數據信號,可以采用異步fifo。需要注意的是,異步fifo不是萬能的,一個異步fifo也只能解決一定范圍內的頻差問題。

(4)盡可能使用FPGA內部的PLL、DLL和MMCM,不要自己產生時鐘。

(5)對于特殊的IO接口,需要仔細計算Tsu、Tco、Th,并利用PLL、DLL、DDIO、管腳可設置的delay等多種工具來實現。簡單對管腳進行Tsu、Tco、Th的約束往往是不行的。

?

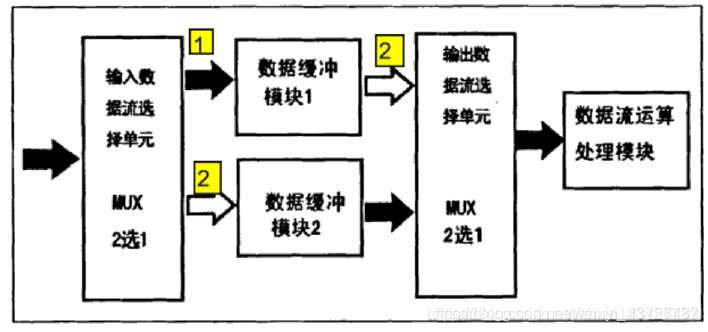

FPGA設計技巧(2):乒乓操作

乒乓操作是FPGA設計中經常用到的設計思想,常用于需要提高數據效率的地方。其主要特點有:

1、 實現數據的無縫緩沖和處理;

2、 可節約緩沖區空間;

3、 可實現低速模塊處理高速模塊如圖所示:

T1時刻,DATA_T1存入buffer 1;

T2時刻,buffer 1已被寫滿,DATA_T2存入buffer 2, 同時buffer 1將DATA_T1送至運算模塊處理;

T3時刻,DATA_T3存入buffer A1,同時buffer 2將DATA_T2送至運算模塊處理;

然后重復2、3階段的操作。

?

FPGA設計技巧(3):串并轉換

串并轉化的思想,旨在與提升運算和芯片運行的速度,串行轉并行已經成為設計中不可缺少的一種思維。

串轉并的設計思想具體是這樣的,首先準備好一組寄存器,當來了一位數據的時候,寄存器組左移(右移)一位,然后把發送過來的數據寄存到寄存器組的最低位(最高位),當一組數據完整接收完畢的時候,標志位會變高,表示當前數據可以采樣。

?

module study(clk, rst_n, data, data_out); //端口列表input clk, rst_n; //時鐘,復位輸入input data; //輸入數據output reg [7:0] data_out;reg [3:0] count; reg [7:0] temp;always @ (posedge clk or negedge rst_n) //時序邏輯,異步復位if(!rst_n)

? begin

? ?data_out <= 0;

? ?temp <= 0;

? ?count <= 0;

? end

?else if(count < 8) //計數表示只接8個數據? begin

? ?temp <= {temp[6:0],data}; //移位寄存器? ?count <= count +1'b1;

? end

?else

? begin

? ?data_out <= temp; //接到后輸出? endendmodule

?

?

采用計數方法,將并行的數據的總數先表示出來,然后發送一位數據減一,后面的接收的這樣表示: data_out <=data[cnt];

?

module study(clk, rst_n, data, data_out,load,turn); //端口列表input clk, rst_n; //時鐘,復位輸入input data; //輸入數據input load; //并行數據使能信號input turn; //串行數據使能信號output reg [7:0] data_out;reg [7:0] temp;always @ (posedge clk or negedge rst_n) //時序邏輯,異步復位if(!rst_n)

? begin

? ?data_out <= 0;

? ?temp <= 0;

? end

?else if(load)

? temp<=data;

?else if(turn) //計數表示只接8個數據? ?temp <= {temp[6:0],temp[7]}; //移位寄存器 else

? begin

? ?temp <= temp[7]; //接到后輸出? endassign data=temp;endmodule

?

FPGA設計技巧(4):流水線(面積換取速度)

流水線設計就是將組合邏輯系統地分割,并在各個部分(分級)之間插入寄存器,并暫存中間數據的方法。目的是將一個大操作分解成若干的小操作,每一步小操作的時間較小,所以能提高頻率,各小操作能并行執行,所以能提高數據吞吐率(提高處理速度)。使用流水線一般是時序比較緊張,對電路工作頻率較高的時候。典型情況如下:

1)功能模塊之間的流水線,用乒乓 buffer 來交互數據。代價是增加了 memory 的數量,但是和獲得的巨大性能提升相比,可以忽略不計。

2) I/O 瓶頸,比如某個運算需要輸入 8 個數據,而 memroy 只能同時提供 2 個數據,如果通過適當劃分運算步驟,使用流水線反而會減少面積。

3)片內SRAM的讀操作,因為SRAM的讀操作本身就是兩極流水線,除非下一步操作依賴讀結果,否則使用流水線是自然而然的事情。

4)組合邏輯太長,比如(a+b)*c,那么在加法和乘法之間插入寄存器是比較穩妥的做法。

?

流水線優缺點

1)優點:流水線縮短了在一個時鐘周期內給定信號必須通過的通路長度,增加了數據吞吐量,從而可以提高時鐘頻率,但也導致了數據的延時。

2) 缺點:功耗增加,面積增加,硬件復雜度增加,流水線就是插入寄存器,以面積換取速度。

?

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論