引言:從本文開始,我們陸續介紹Xilinx 7系列FPGA的時鐘資源架構,熟練掌握時鐘資源對于FPGA硬件設計工程師及軟件設計工程師都非常重要。本章概述7系列FPGA時鐘,比較了7系列FPGA時鐘和前幾代FPGA差異,總結7系列FPGA中的時鐘連接。有關7系列FPGA時鐘資源使用的詳細信息,請關注后續文章。

時鐘資源架構概述

7系列FPGA與前一代FPGA時鐘資源差異

時鐘資源連接概述

1.時鐘資源架構概述

1.1 時鐘資源概述

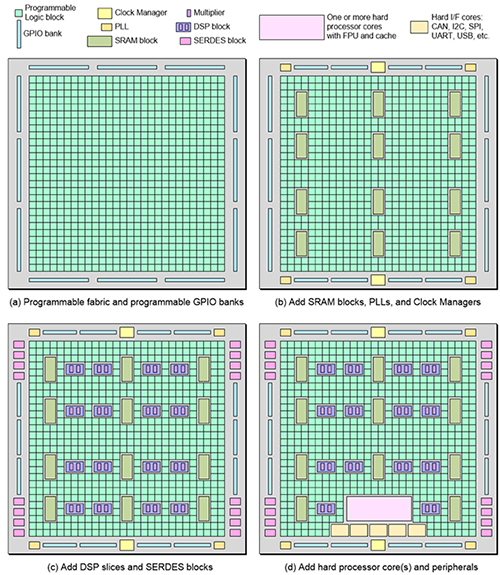

7系列FPGA時鐘資源通過專用的全局和區域I/O和時鐘資源管理符合復雜和簡單的時鐘要求。時鐘管理塊(CMT)提供時鐘頻率合成、減少偏移和抖動過濾等功能。非時鐘資源,如本地布線,不推薦用于時鐘功能。

全局時鐘樹允許同步模塊時鐘跨越整個FPGA器件。

I/O時鐘和區域時鐘樹允許最多為三個垂直相鄰的時鐘區域提供時鐘。

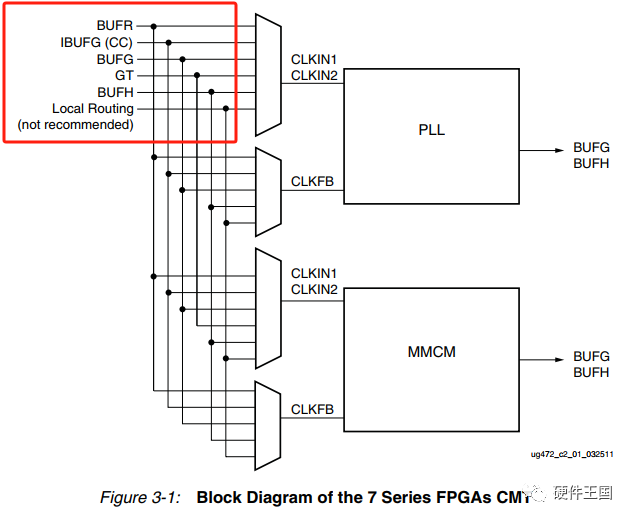

每個CMT包含一個混合模式時鐘管理器(MMCM)和一個鎖相環(PLL),位于I/O列旁邊的CMT列中。

為了提供時鐘,每個7系列器件被劃分為時鐘區域。

時鐘區域的數量隨器件大小而變化,從最小器件的一個時鐘區域到最大器件中的24個時鐘區域。

時鐘區域包括50個CLB和一個I/O bank(50個I/O)的區域中的所有同步模塊(例如:CLB、I/O、串行收發器、DSP、塊RAM、CMT),其中心有一個水平時鐘行(HROW)。

每個時鐘區域從HROW向上和向下跨越25個CLB,并水平跨越器件的每一側。

1.2 時鐘布線資源概述

每個I/O bank包含支持時鐘的輸入引腳,將用戶時鐘帶到7系列FPGA時鐘路由資源上。與專用時鐘緩沖器一起,時鐘輸入管腳將用戶時鐘引入到:

器件相同上/下半部分的全局時鐘線

相同I/O Bank和垂直相鄰的I/O Bank的時鐘線

相同時鐘區域和垂直相鄰的時鐘區域的區域時鐘線

同一時鐘區域內的CMT和有限制的情況下的垂直相鄰的時鐘區域

每個7系列器件有32條全局時鐘線,可以對整個器件中的所有時序資源進行時鐘控制和提供控制信號。全局時鐘緩沖器(BUFGCTRL,在本用戶指南中被簡化為BUFG)驅動全局時鐘線,用于訪問全局時鐘線。每個時鐘區域可以使用時鐘區域中的12條水平時鐘線來支持多達12條全局時鐘線。

全局時鐘緩沖器:

可用作時鐘使能電路,以使能或禁用跨越多個時鐘區域的時鐘

可用作glitch-free multiplexer:

在兩個時鐘源之間選擇

從故障時鐘源切換

通常由CMT驅動,用于:

消除時鐘分布延遲

調整相對于另一個時鐘的時鐘延遲

水平時鐘緩沖器(BUFH/BUFHCE)允許通過水平時鐘行訪問單個時鐘區域中的全局時鐘線。它也可以作為時鐘使能電路(BUFHCE)獨立地使能或禁用跨越單個時鐘區域的時鐘。使用每個時鐘區域中的12條水平時鐘線可以支持多達12個時鐘。每個7系列FPGA都有區域時鐘樹和I/O時鐘樹,可以為一個時鐘區域內對所有時序資源提供時鐘。每個器件還具有多時鐘區域緩沖器(BUFMR),允許區域和I/O時鐘跨越最多三個垂直相鄰的時鐘區域。

I/O時鐘緩沖器(BUFIO)驅動I/O時鐘樹,提供對同一I/O bank中所有時序I/O資源的訪問。

區域時鐘緩沖器(BUFR)驅動區域時鐘樹,該樹驅動同一時鐘區域中的所有時鐘目的地,并可編程輸入時鐘頻率。

緊鄰IOB中的可編程串行器/解串器器(請參閱UG471 7系列FPGA SelectIO Resources用戶指南中的高級選擇邏輯資源一章),BUFIO和BUFR時鐘緩沖區允許源同步系統跨時鐘域,而無需使用額外的邏輯資源。

當與相關的BUFR或BUFIO一起使用時,可以使用多時鐘區域緩沖器(BUFMR)驅動相鄰時鐘區域和I/O時鐘樹。

在一個時鐘區域或I/O bank中最多可支持四個唯一的I/O時鐘和四個唯一的區域時鐘。

高性能時鐘路由將CMT的某些輸出以非常低的抖動、最小的占空比失真的連接到I/O上。

1.3 CMT 概述

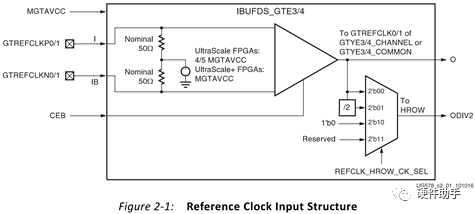

每個7系列FPGA最多有24個CMTs,每個CMT由一個MMCM和一個PLL組成。MMCMs和PLL用作頻率合成器,用于非常寬的頻率范圍,用作外部或內部時鐘的抖動濾波器,以及低偏移時鐘。PLL包含MMCM功能的一個子集。7系列FPGA時鐘輸入連接允許多個資源向MMCM和PLL提供參考時鐘。

7系列FPGA MMCMs具有任意方向的無限精細相移能力,可用于動態相移模式。MMCMs在反饋路徑或一個輸出路徑中也有一個小數計數器,使得頻率合成能力能夠進一步細化。

LogiCORE IP時鐘向導可用于幫助利用MMCMs和PLL在7系列FPGA設計中創建時鐘網絡。圖形用戶界面用于采集時鐘網絡參數。計時向導選擇適當的CMT資源,并以最佳方式配置CMT資源和關聯的時鐘路由資源。

1.1.3 時鐘緩沖、管理和布線

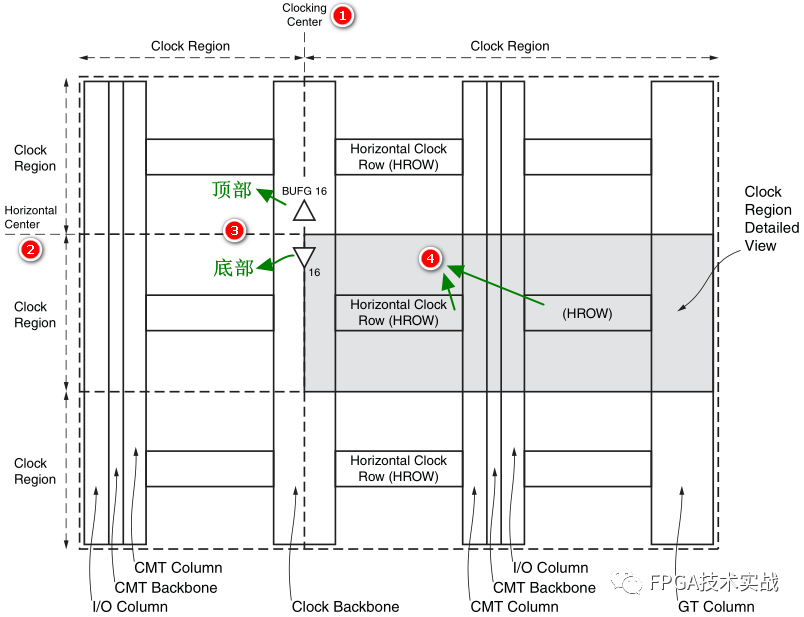

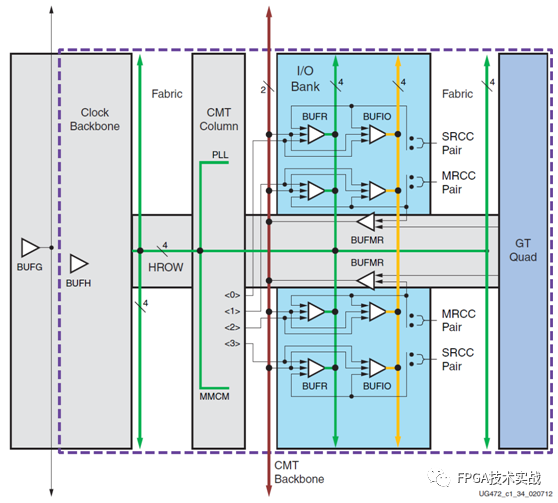

圖1是7系列FPGA時鐘結構的高級視圖。垂直時鐘中心線(①時鐘主干線)將器件劃分為相鄰的左右區域,而水平中心線(②)將器件劃分為頂部和底部側面。時鐘主干中的資源被鏡像到水平相鄰區域的兩側,從而將某些時鐘資源擴展到水平相鄰區域。頂部和底部(③)分隔兩組全局時鐘緩沖器(BUFGs),并對它們的連接方式施加了一些限制。但是,BUFGs不屬于時鐘區域,可以到達器件上的任何時鐘點。所有水平時鐘資源包含在時鐘區域水平時鐘行(HROW)(④)的中心,而垂直的、非區域的時鐘資源包含在時鐘主干或CMT主干中。

圖1、7系列FPGA高級時鐘結構視圖圖2是一個時鐘區域內可用時鐘資源及其基本連接的高層次概述。

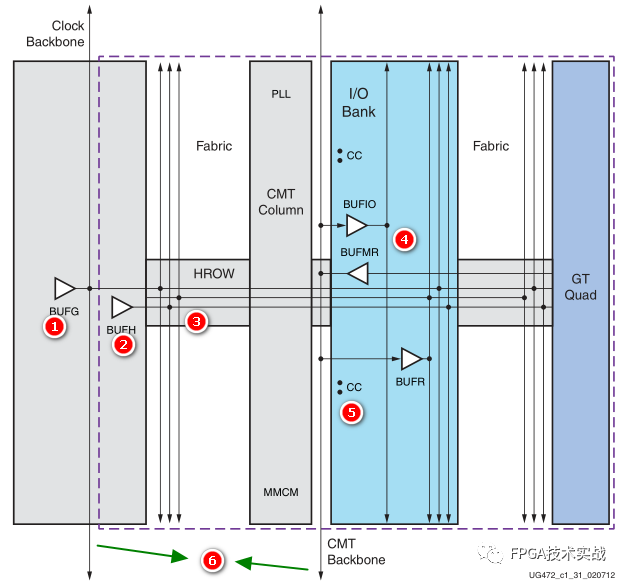

圖2、時鐘區域的基本視圖在圖中,我們可以看到:

全局時鐘緩沖器(①)可以通過HROW進入每個區域,即使物理空間上不在該區域。

水平時鐘緩沖器(②BUFH)通過HROW驅動該區域的每個時鐘點。

BUFGs和BUFHs在HROW中共享路由路徑(③)。

I/O緩沖器(BUFIO)和區域時鐘緩沖器(BUFR)位于I/O bank內部(④)。BUFIO只驅動I/O時鐘資源,而BUFR驅動I/O資源和邏輯資源。

BUFMR支持BUFIOs和BUFRs的多區域鏈接。時鐘輸入(芯片*CC管腳⑤)將外部時鐘連接到器件上的時鐘資源。某些資源可以通過CMT主干時鐘網絡(⑥)連接到頂部和底部的區域。

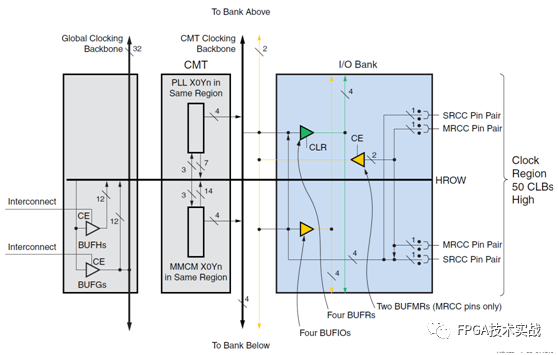

圖3顯示了器件右邊緣單個時鐘區域中時鐘的更詳細視圖。在該圖中,我們可以看到外部時鐘輸入管腳SRCC和MRCC進入I/O Bank后可以驅動的時鐘資源以及CMT資源與外部互聯情況。

圖3、單時鐘區域(器件右側)

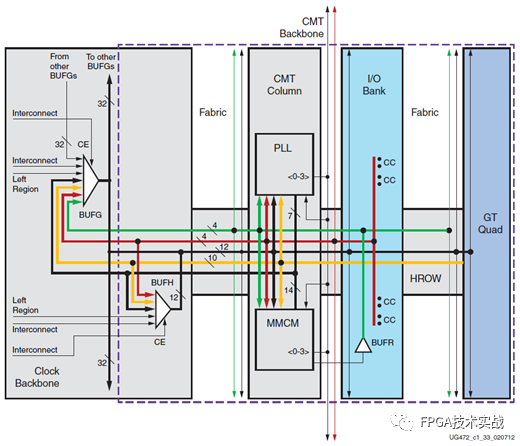

圖4顯示了更詳細的全局BUFG和區域BUFH/CMT/CC引腳連接以及一個區域內可用資源的數量(此處顯示右側區域)。

圖4、BUFG/BUFH/CMT時鐘區域細節在圖4中,我們可以看到:

SRCC和MRCC時鐘的輸入引腳中的任何一個都可以驅動CMT和BUFH中的PLL/MMCM。

BUFG顯示位于該區域中,但可以實際位于時鐘主干的其他位置。

BUFG和BUFH在HROW中共享12條路由,可以驅動該區域內的所有時鐘點。BUFGs也可以驅動BUFHs(圖4中未顯示),允許在其他全局時鐘分布上單獨啟用時鐘(CE)。

一個GT Quad有十個專用的通道來驅動CMT和時鐘緩沖器。

位于I/O bank中的BUFRs有四個走線驅動邏輯、CMT和BUFG中的時鐘點。CMT可以使用CMT主干網驅動相鄰區域中的其他CMT,但有局限性。類似地,時鐘輸入管腳可以在相同的限制下驅動相鄰區域的CMT。

時鐘輸入管腳在器件的同一頂部/底部的任何地方可以驅動BUFG。CMT主干網中有四條走線支持垂直區域之間的連接。

邏輯互連驅動BUFG和BUFH的CE引腳。邏輯互連也可以將時鐘驅動到相同的緩沖區,但必須小心,因為時間是不可預測的。圖5顯示了BUFR/BUFMR/BUFIO時鐘區域詳細信息。

圖5、BUFR/BUFMR/BUFIO時鐘區域詳細信息在圖5中,我們可以了解到:

每個I/O bank包含四個BUFIO和四個BUFRs。這些時鐘緩沖器中的每一個可以由專用的輸入時鐘管腳對(_CC管腳)驅動,或者可以直接由MMCM的特定輸出時鐘驅動。

兩個支持時鐘的輸入管腳對,稱為MRCCs,支持多區域時鐘方案。一個MRCC管腳對可以驅動一個特定的BUFMR,而該BUFMR又可以驅動相同和相鄰區域中的BUFIOs和BUFRs,從而促進多區域/bank接口。

GT Quad也可以驅動BUFMRs。

MMCM《3:0》輸出有一個專用的高性能差分路徑到BUFRs和BUFIO。此功能也稱為高性能時鐘(HPC)。

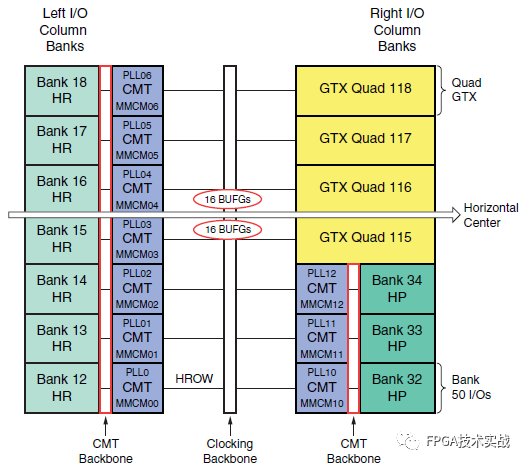

圖6、7K325T架構布局

盡管所有7系列器件都具有相同的基本架構,但系列和系列內器件之間存在一些架構差異。每7系列FPGA在器件的左邊緣至少有一個完整的I/O列。GT可以是7系列FPGA支持的任何一個串行收發器(GTP、GTX,或GTH)。帶有GTs的器件要么在器件的右邊緣有一個GTs和I/O的混合列(一些Kintex-7器件和一些Artix-7器件),要么在器件的右邊緣有一個完整的GT列(一些Kintex-7器件和一些Virtex-7器件)和一個完整的I/O列在器件的右側。其他Virtex-7器件的左右邊緣都有完整的GT列,左右兩側都有完整的I/O列側面。Artix-7200t器件在時鐘列的頂部和底部有GTP收發器。

2. 7系列FPGA時鐘與6系列FPGA的區別

7系列FPGA時鐘具有與Virtex-6 FPGA類似的結構,并支持許多相同的功能。但是,不同的時鐘組件及其功能存在一些架構差異和修改。與Spartan-6 FPGA相比,它在結構和功能上都有一些顯著的變化。一些Spartan-6 FPGA時鐘原語不再可用,取而代之的是更強大、更簡單的結構。

2.1 與Virtex-6 FPGA的不同

7系列FPGA基本BUFIO時鐘功能沒有改變,唯一的例外是BUFIO現在只跨越一個Bank。相鄰Bank的直接時鐘被一個新的時鐘緩沖器所取代。現在每個Bank有四個BUFIO,另外,BUFR的基本目的沒有改變。然而,現在BUFR只直接跨越一個時鐘區域。現在每個區域有四個BUFRs和四個區域時鐘(軌道)。

7系列FPGA引入了一種新的緩沖類型:BUFMR/BUFMRCE。BUFMR/BUFMRCEs驅動BUFIOs和/或BUFRs在同一垂直相鄰位置區域。他們還提供相同的多時鐘區域/多組時鐘路由,可用于支持相同三個時鐘區域/組的Virtex-6 FPGA能力.BUFMRCE具有可選擇的同步或異步切換功能。

7系列FPGA不再支持Virtex-6系列中的全局時鐘(GC)輸入引腳。每列4個時鐘輸入引腳/對替換GCs,支持時鐘的輸入引腳的連接性得到了增強,以支持以前的GC功能。

全局時鐘多路復用器BUFGMUX添加了一個屬性CLK_SEL_TYP,用于允許兩個輸入時鐘的同步或異步時鐘切換(以前僅通過忽略端口可用)。

BUFHCE有一個增強的時鐘使能,允許輸入時鐘的同步或異步使能。

CMT現在包含一個MMCM和一個PLL(MMCM的一個子集),而不是兩個MMCM,以及保留的專用內存接口邏輯。CMT列位于SelectIO旁邊 CMT中的列/列組,并具有對I/O的專用訪問權限以獲得高性能。全局時鐘緩沖區仍然位于由驅動的I/O列之間的設備的垂直中心CMTs.直接不再支持CMT內的級聯。直接級聯到相鄰的cmt是可能的,但是由于資源有限而受到限制。級聯到相鄰CMT之外的其他CMT會導致源和目標MMCMs/pll之間的相位偏移,并且需要特殊的屬性設置。

分數除法器不再共享輸出計數器。這將釋放這些計數器用于其他用途。分數計數器增加了靜態相移功能。

時鐘保持功能不再可用

MMCMs支持擴頻

2.2 與Spartan-6 FPGA的不同

Spartan-6體系結構獨有的一些Spartan-6 FPGA時鐘電路拓撲、功能和塊不受支持,已被7系列FPGA時鐘功能所取代。7系列設備不直接支持DCM_SP,DCM_CLKGEN, BUFIO2, BUFIO2_2CLK, BUFIO2FB, BUFPLL, and BUFPLL_MCB等特性和功能。

PLL是MMCM的一個子集,具有相同的性能(最小CLKIN/PFD和最小/最大VCO頻率除外)、一些連接限制和一些降低的功能。與以前的SpartanFPGA PLL相比,7系列FPGA PLL增加了掉電、輸入時鐘切換和級聯到相鄰CMT。PLL與BUFIO或BUFR沒有直接連接。

在7系列FPGA中,沒有直接替代BUFIO2和BUFIO2 clk原句的方法。使用BUFIO和BUFR代替推薦的連接來驅動ILOGIC和Logic。

Spartan-6 FPGA BUFIO2專用輸入路由從GCLK到CMT和全局時鐘緩沖器不再受支持。要遷移到7系列FPGA,請使用來自CCIO引腳的專用輸入路由。

在7系列FPGA中沒有直接等效于Spartan-6 FPGA BUFPLL。要進行遷移,請使用BUFIO和BUFR以及ILOGIC和logic的推薦連接。MMCME2 CLKOUT[0:3]的高性能時鐘路由取代了BUFPLL的專用路由。ISERDES和OSERDES電路基于Virtex-6體系結構。

在7系列FPGA中,不再需要BUFIO2FB基元。對于MMCM和PLL反饋連接,CLKFBIN可以直接連接到全局時鐘緩沖器、輸入引腳或CLKFBOUT,具體取決于所使用的反饋。

Spartan-6 FPGA僅支持BUFH。7系列FPGA BUFHCE原語添加了禁用時鐘的功能,以在由該資源驅動的時鐘區域中實現潛在的節能。

7系列FPGA新的緩沖區BUFMR/BUFMRCE驅動相同和垂直相鄰時鐘區域中的BUFIO和/或BUFRs。當與BUFIO或BUFR一起使用時,BUFMR/BUFMRCE允許MRCC輸入訪問相鄰時鐘中的BUFIO和BUFR區域。BUFMRCE具有可選擇的同步或異步切換功能。

Spartan-6 FPGA設計遷移的一個新原語是BUFR。當與BUFIO一起使用時,BUFRs功能將取代BUFIO2、BUFIO2 clk和BUFPLL功能。在每個時鐘區域中有四個BUFR。

Spartan-6 FPGA設計遷移的另一個新原語是BUFIO。當與BUFR一起使用時,BUFIO功能將取代BUFIO2、BUFIO2 clk和BUFPLL功能。

與Spartan-6體系結構中的兩個DCM和一個PLL不同,7系列FPGA使用的CMT包含一個MMCM、一個PLL和專用內存接口邏輯,這些邏輯在此時保留給Xilinx使用。這些功能現在支持DCM及其相關功能。CMT位于與SelectIO列相鄰的單獨列中,具有對I/O的專用訪問權限。DCM_SP和DCM_CLKGEN不再可用,它們的功能現在在MMCMs和PLL中受支持。

7系列FPGA不再支持全局時鐘(GCLK)輸入。現在,每一個支持Spartan-6 FPGA GCLK引腳功能的銀行都有四個支持時鐘的輸入引腳。

對于Spartan-6 FPGA設計人員來說,MMCM是一個新的功能塊。MMCM增加了分頻、精細相移、動態相移、反向時鐘輸出、CLKOUT6到CLKOUT4級聯以及其他一些功能。使用CLKOUT[0:3],MMCMs到BUFIO/BUFR的HPC連接取代了到BUFPLL的直接路由連接。還提供了更廣泛的DRP。

對于通用高速I/O時鐘,使用PLL不再是推薦的CMT功能。PLL與BUFIO或BUFR沒有直接連接。不再支持CLKOUT0反饋。將MMCM用于高速I/O接口。級聯連接使用有限的CMT主干資源。還有一種新的斷電模式。完全支持輸入時鐘切換。Spartan-6 FPGA和7系列FPGA的工作范圍不同。DRP功能仍然可用。DRP功能位置和地址已更改。

Spartan-6 FPGA DCM_SP不再受支持。要遷移到7系列FPGA,請使用MMCM和PLL.

Spartan-6 FPGA DCM_CLKGEN在7系列FPGA中不受直接支持。使用MMCM或PLL低帶寬輸入抖動濾波。還可以使用MMCM或PLL的DRP參考設計來完成M/D值的動態重新編程。

3.時鐘連接概述

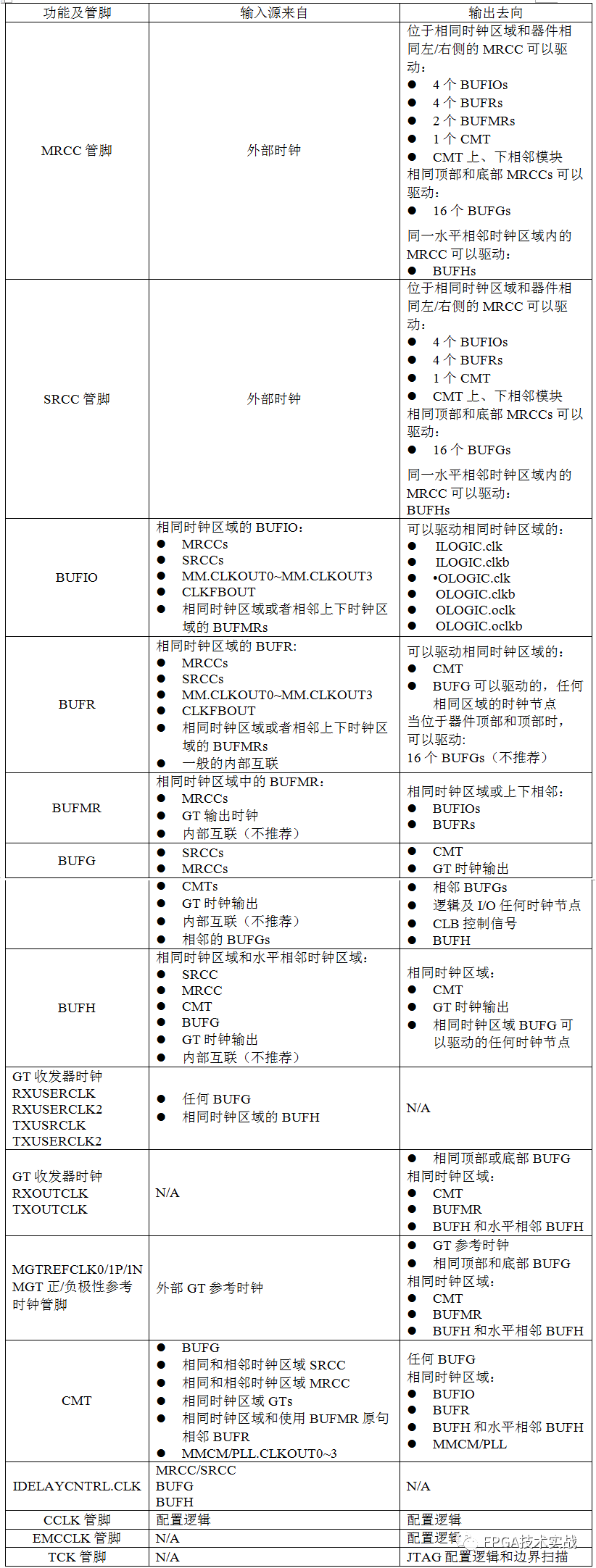

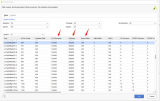

表1對7系列FPGA時鐘連接進行了總結。

表1、7系列FPGA時鐘連接總結

電子發燒友App

電子發燒友App

評論