我們在ASIC或FPGA系統設計中,常常會遇到需要在多個時鐘域下交互傳輸的問題,時序問題也隨著系統越復雜而變得更為嚴重。

跨時鐘域處理技術是IC設計中非常重要的一個部分,我們需要學習并應用一些常用的處理方法,從而提高電路運行的穩定性,使得整個系統更魯棒。

下面考慮ASIC設計場景,為了滿足系統功能需求,整個系統由不同的功能塊構成,例如:

存儲器

浮點引擎

存儲控制器

總線接口

高速接口

假如考慮處理器和存儲器的工作頻率為500MHz,帶有存儲器控制器的浮點引擎的工作頻率為666.66MHz,總線接口和高速接口工作頻率為250MHz,則該設計具有多個時鐘,被視為多個時鐘域的設計。

1、多時鐘域設計常用方法

如前所述,多個時鐘域的處理問題是在傳輸數據和控制信號時,它對數據完整性有影響。下面的策略在ASIC設計階段是有用的。

嘗試為數據和控制路徑優化制定策略。

嘗試創建多個時鐘域組來定義策略。

在多個時鐘域之間傳遞控制信號時,嘗試使用同步器的策略。

嘗試使用FIFO和緩存的數據路徑同步器來提高數據完整性。

現在討論重要的跨時鐘處理問題與策略及其在多時鐘域設計中的使用。

2、多時鐘域設計有哪些問題

如果我們考慮適度的門數設計或使用單時鐘工作的處理器核心和設計,它可能在布局階段由于額外的互連延遲而產生時序違例。但是這種設計可能會通過架構、RTL、綜合和基于工具的優化調整來滿足時序和性能。

現在考慮圖中所示的需要多個時鐘的設計,讓我們試著理解設計中的問題。

1.由于多個時鐘域,數據完整性是主要問題,設計需要通過數據完整性檢查。

2.沒有使用同步器的時鐘域邊界上的觸發器將由于建立和保持違例而存在亞穩態問題。

3.該設計將存在時序違例,并且很難強制時序電路輸出進入有效的合法狀態。

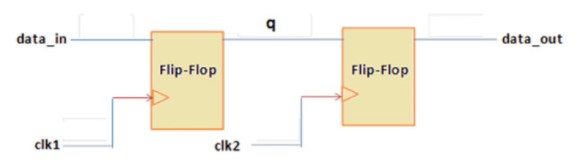

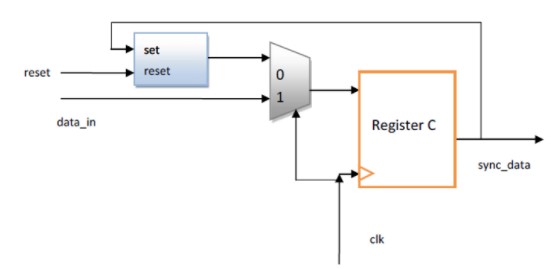

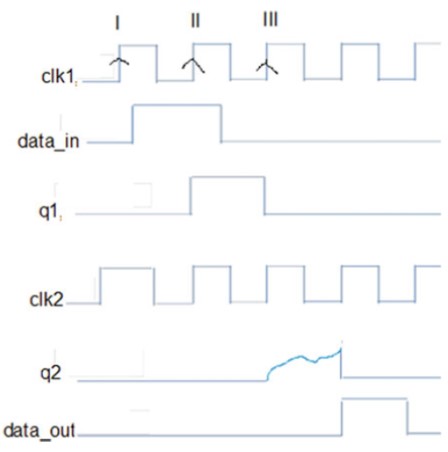

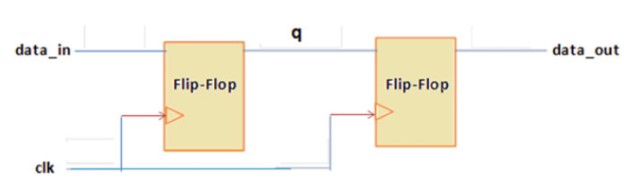

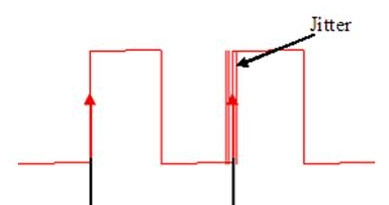

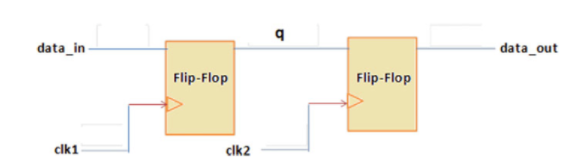

讓我們用具有多個時鐘域的時序電路來理解上面的內容。由于到達clk1和clk2之間的相差,第二個時鐘域的觸發器將有建立和保持違例,即觸發器輸出data_out將是亞穩態的。原因是時鐘域1的q輸出在clk2活動邊的建立和保持窗口期間可能會改變,因此data_out將被迫進入非法狀態,即亞穩態。如圖1所示。

圖1 多時鐘域概念

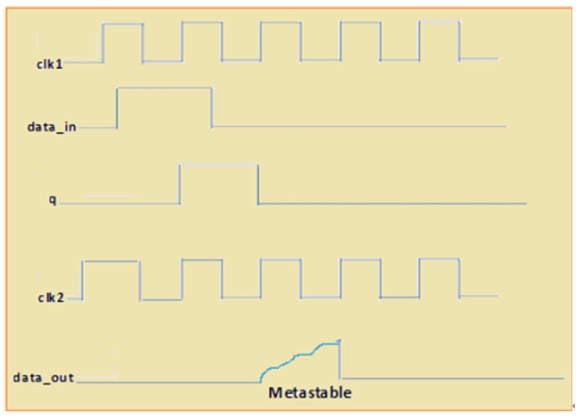

時序如圖2所示。

圖2 亞穩態輸出

3、架構設計策略

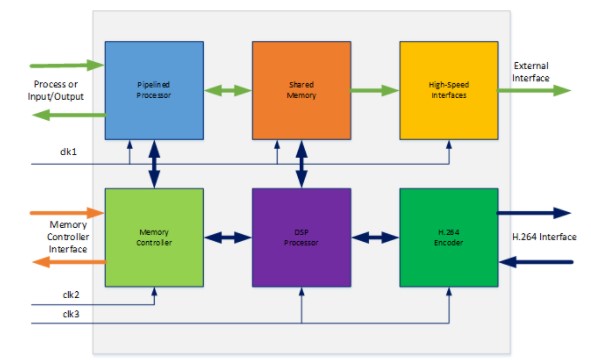

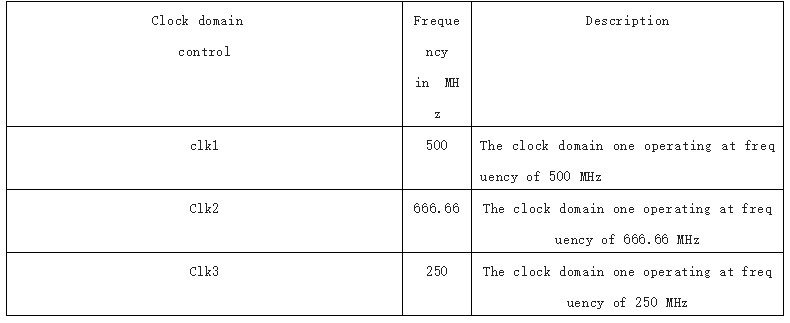

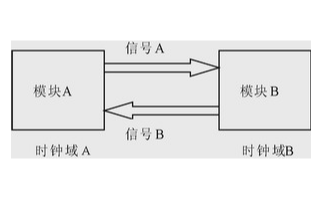

考慮圖3中有三個時鐘域的設計,表1描述了不同時鐘頻率下的時鐘域信息。

圖3 多時鐘域架構

表1 多時鐘域時鐘組

作為一名IC設計人員或架構師,我們需要考慮多個時鐘域設計的整體數據完整性檢查,并需要為數據路徑和控制路徑提供干凈的時序。

考慮到這一點,我們需要設計同步器來在多個時鐘域設計之間傳輸數據。當在多個時鐘域設計之間傳遞控制信號時,電平、多路復用器和脈沖等同步器是有用的。異步FIFO可以用作同步器,在時鐘域和數據路徑之間傳輸數據。

以下是我們在進行多時鐘域設計時應該使用的一些準則,以消除CDC錯誤。

避免亞穩態:在傳遞控制信號信息時,使用寄存器輸出,因為這有助于避免毛刺和冒險。通過在傳遞控制信號時使用寄存的輸出邏輯,可以避免單時鐘周期內的多次轉換。亞穩態阻塞邏輯如圖4所示。

圖4 亞穩態阻塞邏輯

使用MCP:強烈推薦多周期路徑策略,以避免在多個時鐘域之間傳遞數據和控制信號信息時的亞穩態問題。在MCP中,采用的策略是建立控制和數據對,將具有單比特控制信號的多比特數據從發送時鐘域傳遞到接收時鐘域。利用脈沖同步器可以在接收時鐘域對控制信息進行采樣,并在有或沒有同步器的情況下將數據傳遞到接收時鐘域。該技術可以在多個周期內保持數據的穩定值,并且可以利用脈沖同步器產生的同步信號在接收時鐘域中采樣。跨越時鐘域的邊界,以下是需要考慮的關鍵點。

(a)控制信號必須使用多級同步器進行同步。

(b)控制信號應無冒險和毛刺。

(c)應該有跨越時鐘邊界的過渡。

(d)控制信號應至少穩定一個時鐘周期。

MCP策略如圖5所示。

圖5 MCP策略

采用FIFO:異步FIFO是傳遞多位控制信號或數據信息的有效技術。在這種技術中,發送時鐘域在FIFO未滿時將數據寫入FIFO內存緩沖區,接收時鐘域在FIFO未空時從FIFO緩沖區讀取數據。

使用格雷碼計數器:在大多數具有跨時鐘域(CDC)的ASIC設計中,跨時鐘域傳遞計數器值是至關重要的。如果二進制計數器用于在時鐘域邊界交換數據,那么由于一個或多個比特的轉換,數據轉換很容易出錯。在這種情況下,建議使用格雷碼計數器在跨時鐘邊界傳遞數據。在接收端時鐘域,采用格雷碼到二進制碼的轉換,將原始數據恢復。

設計分區:在為多個時鐘域設計邏輯時,通過使用時鐘組對設計進行分區。

時鐘命名約定:為了更好地識別時鐘源,建議使用時鐘命名約定。時鐘的命名約定應該由有意義的前綴/后綴支持。例如,發送時鐘域使用clk_s,接收時鐘域使用clk_r。

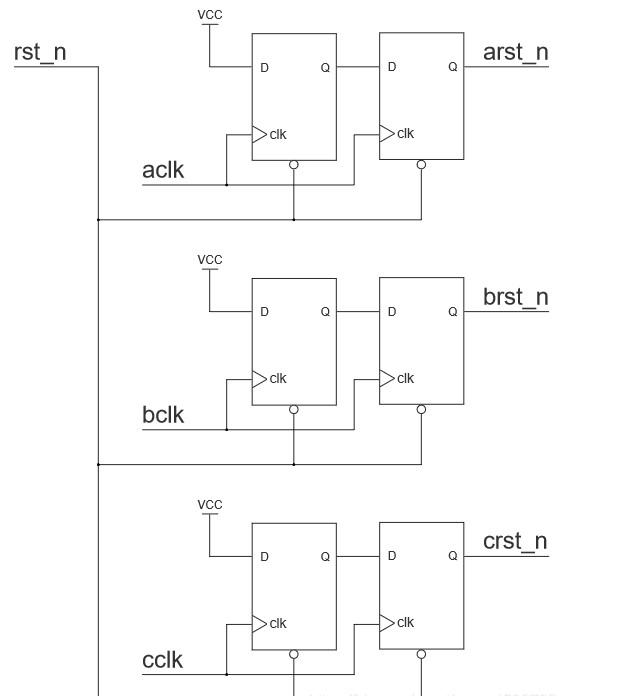

同步復位:對于ASIC設計,強烈建議使用同步復位器。

避免保持時間違例:為了避免保持時間違例,建議仔細查看體系結構,并制定在多個時鐘周期之間傳遞穩定數據的策略。

避免丟失相關性:在時鐘域邊界上,有幾種可能導致丟失相關性的方式。比如有:

(a)總線上的多個比特

(b)多個握手信號

(c)不相關的信號

為了避免這種情況,使用時鐘意圖驗證技術,因為這些技術將確保在時鐘邊界上傳遞多位信號。

4、控制路徑與同步

本節討論ASIC設計中使用的各種同步器和策略。

電平或多觸發同步器

在多個時鐘域之間傳遞的控制信號主要由快時鐘域向慢時鐘域傳遞,會出現時序錯誤,設計中會出現時序違例。因此,在體系結構設計期間,更好的策略是確定多個時鐘域設計的接口邊界,然后在RTL設計中使用同步器的策略。

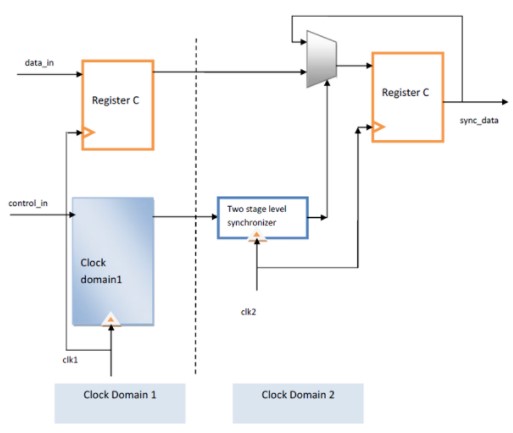

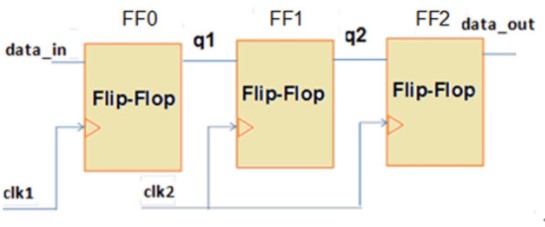

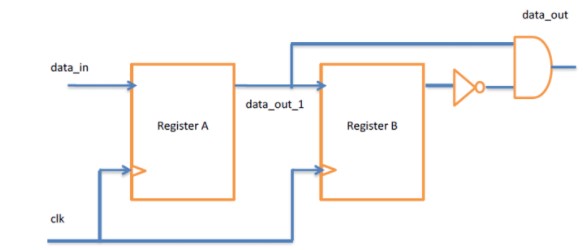

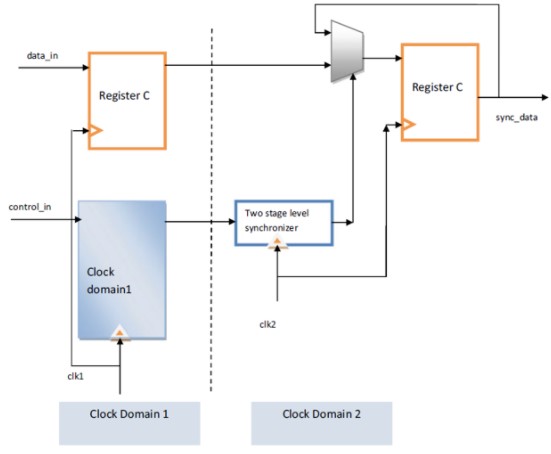

當在多個時鐘域之間傳遞控制信號時,可以通過設計電平同步器(可能使用兩個或三個觸發器)來解決亞穩態問題。圖6使用了兩級電平同步器邏輯。

圖6 控制路徑中有二級電平同步器

如圖6所示,利用電平同步器將控制信號q1從時鐘域1傳遞到時鐘域2。主要的設計策略是將有效的輸出q1傳遞到第二個時鐘域。電平同步器在第二個時鐘域,對輸出q1進行采樣。由于違反了設置或保持時間,第二個時鐘域的輸入觸發器將是亞穩態的,這應該通過設置EDA工具屬性來忽略。輸出的data_out是有效的數據,由于使用了同步器,本設計有兩個時鐘的延遲。

圖6所示的設計時序描述如下(圖7所示)。

圖7 使用兩級同步器的時序

如圖7所示,q1由第一個時鐘域輸出。在clk2的上升沿上,觸發器FF1的輸出q2將由于建立或保持時間違例而進入亞穩態。但是觸發器FF2輸出在接下來的時鐘邊是data_out是有效的輸出。使用該命令設置false path:

?

set_false_path –from FF0/q –to FF1/q

?

使用這兩個觸發器的電平同步器如圖8所示,可以在設計中采用。更好的策略是在RTL設計期間將電平同步器的RTL描述作為單獨的模塊。引入的延遲取決于將輸出驅動到有效合法狀態所需的觸發器數。

圖8 電平同步器

下面將對RTL描述部分進行描述:

?

always?@?(posedge?clk)

在ASIC設計中,當控制信息需要從快時鐘域傳遞到慢時鐘域時,就會出現數據完整性問題。該問題是由于在將控制信號從時鐘域1傳遞到時鐘域2時觸發器輸出的合法狀態不收斂造成的。

利用脈沖展寬器可以解決從快時鐘域到慢時鐘域的采樣問題。工作在正時鐘邊緣的電平脈沖發生器如圖9所示。

圖9 電平到脈沖轉換

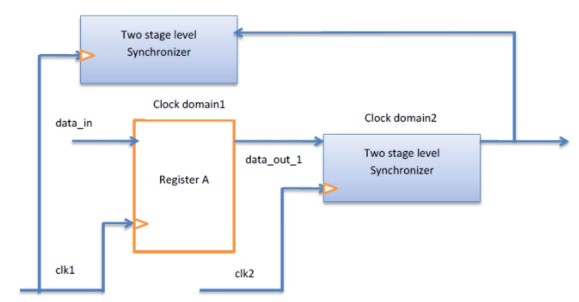

另一種機制是信號的握手,可以用來實現數據的收斂。

如圖10所示,將時鐘域2的采樣信號作為握手信號反饋到時鐘域1。這種握手機制類似于對較快時鐘域1的確認或通知,較快時鐘域傳遞的控制信號被較慢時鐘域成功采樣。在實際的大多數場景中,都采用了這種機制,即使較快的時鐘域在收到較慢時鐘域的有效通知或確認信號后,也可以發送另一個控制信號。

圖10 控制信號的握手機制

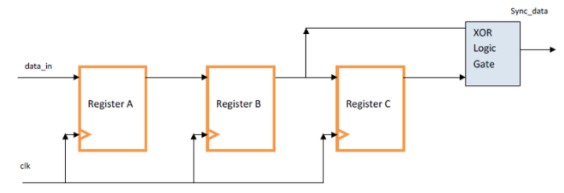

脈沖同步器

這種類型的同步器使用多級電平同步器,其中兩級電平同步器的輸出由輸出觸發器采樣。這種同步器也稱為切換同步器,用于將發送時鐘域產生的脈沖同步到目標時鐘域。當將數據從較快的時鐘域傳遞到較慢的時鐘域時,如果使用兩級電平同步器,脈沖可能跳過。在這種情況下,脈沖同步器是有效和有用的。脈沖同步器圖如圖11所示。

圖11 脈沖同步器

Mux同步器

將時鐘域1的信息發送到時鐘域2時,使用這對數據和控制信號。使用多bit數據和使用單bit控制信號。在接收端,根據發送時鐘和接收時鐘的比值,使用電平或脈沖同步器為多路復用器產生控制信號。這種技術類似于MCP,并且如果數據在跨越時鐘邊界的多個時鐘周期中是穩定的,則這種技術是有效的。如圖12所示。

圖12 Mux同步器

5、多bit數據傳輸的挑戰

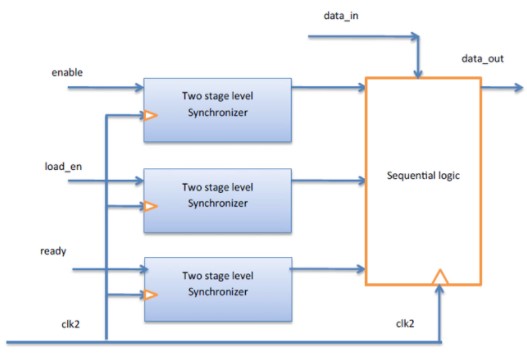

在多個時鐘域之間傳遞多個控制信號是一個重要的挑戰。問題是這些控制信號到達的時間不同。如果這些控制信號的到達沒有得到正確的管理,那么真正的問題是由于傾斜。考慮圖13所示的場景,其中“enable ” “load_en ”和“ready ”需要從一個時鐘域傳遞到另一個時鐘域。在這種情況下,如果使用獨立的電平同步器,則接收端可能會因為信號的歪斜(信號到達時間不同)而出現同步失敗。

圖13 對接收端時鐘域內的多個信號進行采樣

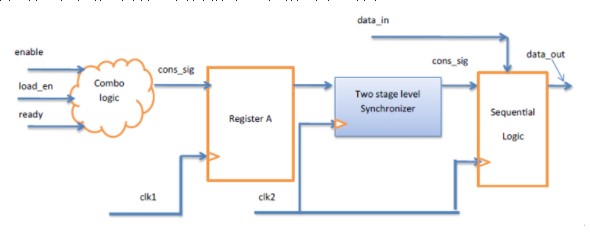

考慮其中一個控制信號,例如enable到達較晚,則控制路徑中可能存在同步失敗,為了避免這組3個控制信號,嘗試在時鐘域之間傳遞共同信號。策略如圖14所示。

圖14 固定在多時鐘域內傳遞的控制信號

6、數據路徑同步

用于在時鐘域之間傳遞多個數據bit的技術是:

握手機制

異步FIFO緩存

格雷編碼

握手機制

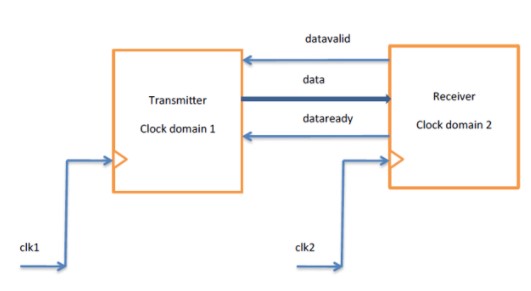

在時鐘域之間傳遞多比特信號時,握手機制的使用是一種有用的技術。如圖15所示,發射機工作在clk1,接收機工作在clk2。數據可以從發射機傳送到接收機。這里要注意,該握手與AXI總線的握手略有不同。

接收端時鐘域可以產生數據有效(data valid)和設備就緒(ready)等握手信號。因此,目的是通知發送器總線上還存在有效數據可用,設備還沒有準備好接收新數據。

圖15 握手機制框圖

握手信號datavalid它是來自時鐘域2的主動高電平握手信號,表示傳輸的數據是有效數據,接收端只需要很少的時鐘就可以對該數據進行采樣。傳輸數據時的時鐘延遲取決于同步器中使用的觸發器的數量,而延遲是握手機制的最大缺點之一。

握手信號deviceready它表明當數據有效的時候,接收端已經準備好接收新數據,并且設備ready好了可以拉高通知發送端將新數據放到數據總線上。

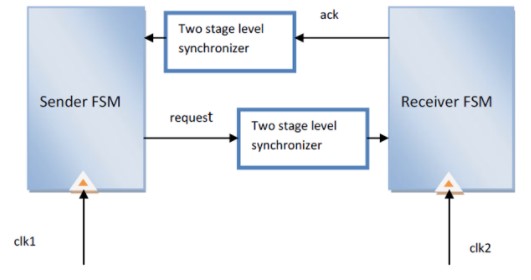

如果我們有多個時鐘域的FSM控制器,那么設計架構來通過使用請求(request)和確認(ack)信號建立同步。FSM控制的握手機制如圖16所示。

圖16 FSM握手機制

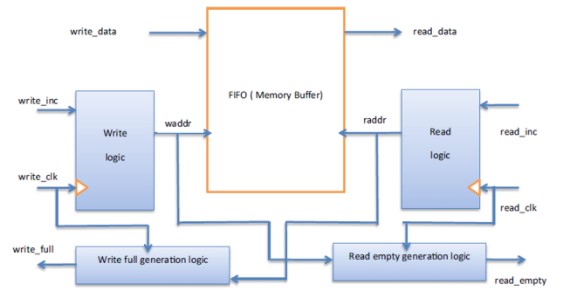

異步FIFO同步器

異步FIFO是有用的,因為數據路徑同步器是用來交換多個時鐘域之間的數據。如果FIFO內存緩沖區沒有滿,發送端時鐘域或發送端時鐘域可以使用write_clk將數據寫入FIFO內存緩沖區,如果FIFO內存緩沖區沒有空,接收端時鐘域可以使用read_clk讀取數據(圖17)。

FIFO由以下幾個塊組成:

Memory:內存緩沖區

Write Clock Domain:在write_clk上工作的寫時鐘域邏輯。

Read clock Domain:讀時鐘域邏輯,它正在read_clk上工作。

Flag Logic:生成標志邏輯empty和full。

FIFO和相關的邏輯塊如圖17所示。

圖17 FIFO框圖

如何得到FIFO的深度?

考慮寫時鐘域的工作頻率為250 MHz,讀時鐘域的工作頻率為100 MHz,沒有延遲,然后傳輸50字節的突發長度,可以使用以下計算:

?

Write?clock?time:?T1?=?1/250?MHz?=?4?ns.

?

如果指定了讀和寫延遲,那么嘗試修改上面的步驟來獲得FIFO的深度。

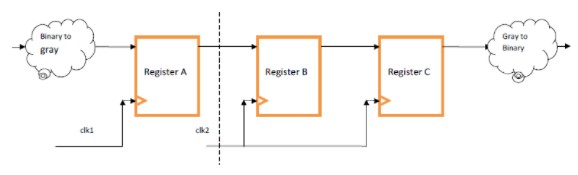

格雷編碼

在傳遞多個位的數據或控制信號時,必須使用格雷編碼技術,因為這種技術保證了兩個連續的數字只有一bit的變化。例如,如果4bit二進制數據需要在多個時鐘域之間傳遞,那么一個或多個bit轉換,因此需要更多的功率和出錯的機會。因此,為了避免這種情況,提高性能,在發送端或發送端時鐘域采用二進制到格雷碼轉換邏輯。這保證了在時鐘邊界上只有一bit變化。為了得到接收端時鐘域的原始二進制數據,采用格雷碼到二進制碼的轉換。該技術如圖18所示。

圖18 格雷編碼技術

7、總結

總結幾個要點:

在多個時鐘域之間傳遞數據時,設計數據路徑同步器。

在多個時鐘域之間傳遞控制信號時,需要設計控制路徑同步器。

在通過時鐘域傳遞數據和控制信號信息時,強烈建議使用多周期路徑來避免亞穩態問題。

傳遞多bit控制或數據信息的常用而有效的技術是使用異步FIFO。

對于在多個時鐘域之間傳遞的多位控制信號,采用分組技術來避免由于到達時間不同而產生的歪斜。

審核編輯:劉清

電子發燒友App

電子發燒友App

評論