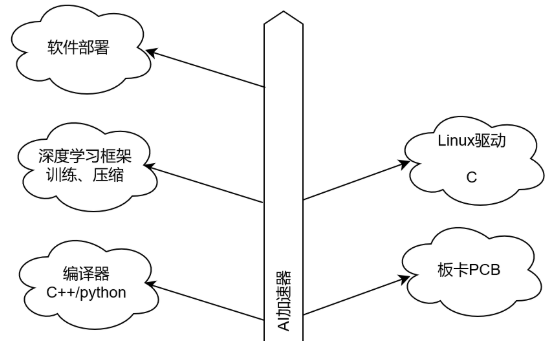

相比GPU和GPP,FPGA在滿足深度學習的硬件需求上提供了具有吸引力的替代方案。憑借流水線并行計算的能力和高效的能耗,FPGA將在一般的深度學習應用中展現GPU和GPP所沒有的獨特優勢。同時,算法

2016-07-28 12:16:38 7349

7349 大家好,又到了每日學習的時間了,今天我們來聊一聊基于FPGA的異步FIFO的實現。 一、FIFO簡介 FIFO是英文First In First Out 的縮寫,是一種先進先出的數據緩存器,它與普通

2018-06-21 11:15:25 6164

6164

的主要有三種不同架構的器件種類:CPU,GPU,AI芯片/FPGA。CPU是一個通用架構芯片,其計算能力和數據帶寬相對受到限制,面對大計算量的深度學習就顯露出其缺點了。GPU含有大量的計算陣列,可以適用于大規模運算,而且其生態較為成熟和完整,所以現在包

2020-10-10 16:25:43 3349

3349

,它是7系列FPGA新設計的IO專用FIFO,主要用于IOLOGIC(例如ISERDES、IDDR、OSERDES或ODDR)邏輯功能的擴展。 FPGA的每個BANK有4個IN_FIFO

2020-11-29 10:08:00 2340

2340

最近加的群里面有些萌新在進行討論**FIFO的深度**的時候,覺得 **FIFO的深度計算比較難以理解** 。所

2023-11-28 16:19:46 347

347

FIFO先進深度?我也想知道我的輸入是否改變為3個數據單元(每個16位)的突發,應該是什么深度?謝謝,阿倫以上來自于谷歌翻譯以下為原文Hi All, I have a design issue, I

2019-01-10 10:45:27

本帖最后由 eehome 于 2013-1-5 10:08 編輯

FPGA學習總結[經典推薦]

2012-05-14 16:59:49

現場可編程門陣列 (FPGA) 解決了 GPU 在運行深度學習模型時面臨的許多問題

在過去的十年里,人工智能的再一次興起使顯卡行業受益匪淺。英偉達 (Nvidia) 和 AMD 等公司的股價也大幅

2024-03-21 15:19:45

被用作系統中的緩沖元件或隊列。因此FIFO的大小基本上暗示了所需緩存數據的容量,該容量取決于讀寫數據的速率。FIFO深度計算=B-B*F2/(F1*I), B為突發數據塊大小

2013-05-28 14:17:37

為1024,但是在此處顯示的卻是1023。原因是因為FIFO結構的特殊性,并不是我們設置的有問題。所以,在我們這個異步FIFO中,深度為1023。

點擊OK直接生成。在點擊

2023-06-16 17:50:31

CORE 之 FIFO設計 本篇實現基于叁芯智能科技的SANXIN -B01 FPGA開發板,以下為配套的教程,如有入手開發板,可以登錄官方淘寶店購買,還有配套的學習視頻。 SANXIN-B01

2023-03-15 16:19:35

深度學習中的IoU概念理解

2020-05-29 09:24:28

深度學習中的圖片增強

2020-05-28 07:03:11

汽車安全系統的發展進步中發揮重要的作用。而這些系統遠不止僅供典型消費者群體掌握和使用。深度學習這一概念在幾十年前就已提出,但如今它與特定的應用程序、技術以及通用計算平臺上的可用性能更密切相關。深度學習

2022-11-11 07:55:50

簡單的回顧的話,2006年Geoffrey Hinton的論文點燃了“這把火”,現在已經有不少人開始潑“冷水”了,主要是AI泡沫太大,而且深度學習不是包治百病的藥方。計算機視覺不是深度學習最早看到

2021-07-28 08:22:12

神經系統,因此支持人工智能的概念。圖 2:簡易反向傳播示例盡管深度學習具有效力,但其在實際應用中也遇到了一些挑戰。對于容易受到系統限制因素(如總體成本、功耗和擴展計算能力)影響的嵌入式應用程序而言,在

2019-03-13 06:45:03

深度學習在預測和健康管理中的應用綜述摘要深度學習對預測和健康管理(PHM)引起了濃厚的興趣,因為它具有強大的表示能力,自動化的功能學習能力以及解決復雜問題的一流性能。本文調查了使用深度學習在PHM

2021-07-12 06:46:47

深度學習常用模型有哪些?深度學習常用軟件工具及平臺有哪些?深度學習存在哪些問題?

2021-10-14 08:20:47

摘要與深度學習算法的進步超越硬件的進步,你如何確保算法明天是一個很好的適合現有的人工智能芯片下發展?,這些人工智能芯片大多是為今天的人工智能算法算法進化,這些人工智能芯片的許多設計都可能成為甚至在

2020-11-01 09:28:57

創客們的最酷“玩具” 智能無人機、自主機器人、智能攝像機、自動駕駛……今年最令硬件創客們著迷的詞匯,想必就是這些一線“網紅”了。而這些網紅的背后,幾乎都和計算機視覺與深度學習密切相關。 深度學習

2021-07-19 06:17:28

怎樣從傳統機器學習方法過渡到深度學習?

2021-10-14 06:51:23

不多說,上貨。IP CORE 之 FIFO 設計- ISE 操作工具本篇實現基于叁芯智能科技的SANXIN -B02 FPGA開發板,如有入手開發板,可以登錄官方淘寶店購買,還有配套的學習視頻。FIFO

2023-04-11 20:50:21

SPI2_CONFIG寄存器中FIFO深度是根據什么改變的?是根據TRANSCTRL寄存器的WRTRANCNT和RDTRANCNT設置改變嗎?為什么我設置了WRTRANCNT和RDTRANCNT,SPI2_CONFIG寄存器中FIFO深度還是默認值0x00004311?

2023-05-26 07:46:57

大家好,在zynq 7000系列中,UART FIFO的深度為128字節,這是不是意味著直到所有128字節的數據都在FIFO中傳輸它才會傳輸?如果有人知道,請告訴我...謝謝

2020-03-31 09:29:05

Xilinx FPGA入門連載52:FPGA片內FIFO實例之FIFO配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm1新建源文件打開

2016-02-29 13:35:55

Xilinx FPGA入門連載52:FPGA片內FIFO實例之FIFO配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm1新建源文件打開

2016-02-29 13:35:55

`Xilinx FPGA入門連載56:FPGA片內異步FIFO實例之FIFO配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1新建

2016-03-09 10:49:56

FIFO內緩存數據最多。計算此時寫入數據-該階段讀出數據即為FIFO的最小深度。 Nwr = 120x = Nwr - Nrd = 120 - 96 = 24.二.為保證數據連續輸出,求讀取前

2020-02-22 20:37:49

`FZ3深度學習計算卡總結篇幾個月的試用即將結束,也通過這個板子完成了自己的項目,具體的不方便公開,有網友私聊我相關資料,因此這里做一個統一的說明,能公開的帖子里面都發布了,其他的項目結束之后,會考

2021-01-10 14:39:17

學習的硬件需求上提供了具有吸引力的替代方案。憑借流水線并行計算的能力和高效的能耗,FPGA將在一般的深度學習應用中展現GPU和GPP所沒有的獨特優勢。同時,算法設計工具日漸成熟,如今將FPGA集成到

2018-08-13 09:33:30

都出現了重大突破。深度學習是這些領域中所最常使用的技術,也被業界大為關注。然而,深度學習模型需要極為大量的數據和計算能力,只有更好的硬件加速條件,才能滿足現有數據和模型規模繼續擴大的需求。 FPGA

2019-10-10 06:45:41

- 恒定8 MB /秒(一旦開始讀取,您將需要保持數據速率,不允許上溢/下溢)什么應該是fifo深度?謝謝,以上來自于谷歌翻譯以下為原文Hi, I have a design problem where

2019-04-26 10:56:25

深度學習是什么意思

2020-11-11 06:58:03

上述分類之外,還被用于多項任務(下面顯示了四個示例)。在 FPGA 上進行深度學習的好處我們已經提到,許多服務和技術都使用深度學習,而 GPU 大量用于這些計算。這是因為矩陣乘法作為深度學習中的主要

2023-02-17 16:56:59

《深度學習工程師-吳恩達》03卷積神經網絡—深度卷積網絡:實例探究 學習總結

2020-05-22 17:15:57

關于吳恩達深度學習總結(一)

2019-07-29 10:35:29

點開“memory compiler",然后選擇FIFO,同時在右邊填入自命名的器件名字。點下一步,在這一步中要設置FIFO的數據寬度,FIFO的深度,FIFO的類型(同步FIFO還是異步FIFO,他們

2012-03-27 12:28:32

嗨,我想計算異步fifo的深度,但我很困惑如何計算它。 fifo參數如下:寫Clk Freq = 60 MHz。讀取Clk Freq = 100 MHz。最大WriteBurst大小= 1024

2019-04-17 08:25:47

fifo不為空時,用rd clk = 50 MHz連續讀出數據。從模擬開始,在5次寫入后,fifo空置為空。如何正確計算深度?最初,我的深度為16,所有人都在董事會工作。然后進行實驗,我改變了wr和rd

2019-04-09 06:25:58

數據進入FPGA的速率高于傳出的速率,持續的傳輸會造成數據的溢出,斷續的傳輸可能會造成數據不連續。使用基于LabVIEW FPGA的DMA FIFO作為主控計算機和FPGA之間的緩存,若DMAFIFO深度設置的合適,FIFO不會溢出和讀空,那么就能實現數據輸出FPGA是連續的。

2019-10-12 09:05:54

本文由回映電子整理分享,歡迎工程老獅們參與學習與評論內容? 射頻系統中的深度學習? Deepwave Digital技術? 信號檢測和分類示例? GPU的實時DSP基準測試? 總結回映電子是一家

2022-01-05 10:00:58

圖像壓縮之后的數據存入fifo,然后經過nrf2401發送。。但是由于圖片尺寸比較大,導致fifo深度不夠,受限于FPGA芯片尺寸的限制,fifo深度不能再選大了。。。求指導

2015-05-22 14:34:48

請問2812型DSP的SCI模塊中,接收和發送數據都是16級的FIFO深度是什么意思?對這個16級深度的FIFO不太理解

2023-03-17 11:19:05

嗨,以下條件的FIFO深度是多少?8位并行數據連續出現(即沒有突發長度)寫入和讀取沒有理想的循環。寫頻率= 100MHz讀頻率= 70MHz謝謝娜文G K.

2020-05-21 07:45:14

計算機視覺與深度學習,看這本書就夠了

2020-05-21 12:43:42

`立即學習—60天FPGA工程師入門就業項目實戰特訓營(3月16日開班) 談談FIFO閾值的閾值設置及深度計算1.什么是FIFO2.什么情況下使用FIFO3.什么FIFO的閾值4.FIFO的閾值

2020-02-19 21:09:35

首先介紹異步FIFO 的概念、應用及其結構,然后分析實現異步FIFO的難點問題及其解決辦法; 在傳統設計的基礎上提出一種新穎的電路結構并對其進行綜合仿真和FPGA 實現。

2009-04-16 09:25:29 46

46 容易地嵌入到實際應用系統中;2. 完成從簡單的邏輯控制、數據采集、信號處理、數學計算等功能;3. 核心板FPGA芯片的所有管腳全部引出,可以直接

2023-02-03 15:14:29

基于FPGA的FIFO設計和應用

引 言

在利用DSP實現視頻實時跟蹤時,需要進行大量高速的圖像采集。而DSP本身自帶的FIFO并不足以支持系統中大量數據的暫時存儲

2009-11-20 11:25:45 2127

2127

FPGA設計的高速FIFO電路技術

本文主要介紹高速FIFO電路在數據采集系統中的應用,相關電路主要有高速A/D轉換器、FPGA、SDRAM存儲器等。圖1為本方案的結構框圖。在大容量

2010-05-27 09:58:59 2226

2226

為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設定不當帶來的數據不連續問題,結合LabVIEWFPGA的編程特點和DMA FIFO的工作原理,提出了一種設定 FIFO 深度的方法。對FIFO不同深度的實驗表明,采

2011-09-26 13:45:17 6923

6923

文中給出了異步FIFO的實現代碼和FPGA與DSP的硬件連接電路。經驗證,利用異步FIFO的方法,在FPGA與DSP通信中的應用,具有傳輸速度快、穩定可靠、實現方便的優點。

2011-12-12 14:28:22 51

51 為實現目標識別與跟蹤的應用目的 ,在基于 TMS320DM642 的 FIFO 基礎上擴展存儲空間 ,提出一種基于

FPGA實現 SDRAM 控制器的方法。分析所用 SDRAM 的特點和工作原理

2015-10-29 14:05:57 2

2 FIFO_學習心得。 FIFO_學習心得

2015-11-09 14:07:47 6

6 異步FIFO結構及FPGA設計,解決亞穩態的問題

2015-11-10 15:21:37 4

4 異步FIFO在FPGA與DSP通信中的運用

2016-05-19 11:17:11 0

0 FPGA是深度學習的未來,學習資料,感興趣的可以看看。

2016-10-26 15:29:04 0

0 單片機(Microcontrollers)學習,FPGA學習總結[經典推薦],感興趣的小伙伴可以瞧一瞧。

2016-11-03 15:15:39 153

153 由NSF資助的一個研究項目,目前正在研究如何使用RDMA高性能連接器將深度學習算法在FPGA和跨系統之間運行;另一個由Andrew Ng和兩個超算專家牽頭的項目,則希望把模型放在超級計算機上,給它們一個Python接口。

2017-02-10 16:32:30 744

744 本文我們就來分析目前主流的深度學習芯片的優缺點。 CPU 不適合深度學習 深度學習與傳統計算模式最大的區別就是不需要編程,它是從輸入的大量數據中自發地總結出規律,而傳統計算模式更多都需要人為提取所需

2017-09-27 15:24:59 2

2 基于異步FIFO在FPGA與DSP通信中的運用

2017-10-19 10:30:56 10

10 摘要 利用異步FIFO實現FPGA與DSP進行數據通信的方案。FPGA在寫時鐘的控制下將數據寫入FIFO,再與DSP進行握手后,DSP通過EMIFA接口將數據讀入。文中給出了異步FIFO的實現

2017-10-30 11:48:44 1

1 由騰訊云基礎產品中心、騰訊架構平臺部組成的騰訊云FPGA聯合團隊,在這里介紹國內首款FPGA云服務器的工程實現深度學習算法(AlexNet),討論深度學習算法FPGA硬件加速平臺的架構

2017-11-15 20:20:08 2468

2468 本文總結了Python、Matlab、CPP、Java、JavaScript、Lua、Julia、Lisp、Haskell、.NET、R等語言的深度學習庫,趕緊收藏吧!Theano是一個Python

2017-11-16 14:20:45 2873

2873 在現代電路設計中,一個系統往往包含了多個時鐘,如何在異步時鐘間傳遞數據成為一個很重要的問題,而使用異步FIFO可以有效地解決這個問題。異步FIFO是一種在電子系統中得到廣泛應用的器件,文中介紹了一種基于FPGA的異步FIFO設計方法。使用這種方法可以設計出高速、高可靠的異步FIFO。

2018-07-17 08:33:00 7873

7873

幾乎所有深度學習的研究者都在使用GPU,但是對比深度學習硬鑒方案,ASIC、FPGA、GPU三種究竟哪款更被看好?主要是認清對深度學習硬件平臺的要求。

2018-02-02 15:21:40 10203

10203

為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設定不當帶來的數據不連續問題,結合LabVIEWFPGA的編程特點和DMA FIFO的工作原理,提出了一種設定FIFO深度的方法。對FIFO

2019-01-04 14:25:07 4225

4225

本文從硬件加速的視角考察深度學習與FPGA,指出有哪些趨勢和創新使得這些技術相互匹配,并激發對FPGA如何幫助深度學習領域發展的探討。

2019-06-28 17:31:46 6529

6529 微軟發布了 Project Brainwave,一個基于 FPGA 的低延遲深度學習云平臺。微軟官方測評顯示,當使用英特爾的 Stratix 10 FPGA,Brainwave 不需要任何

2019-07-03 14:58:52 883

883 相比GPU和GPP,FPGA在滿足深度學習的硬件需求上提供了具有吸引力的替代方案。憑借流水線并行計算的能力和高效的能耗,FPGA將在一般的深度學習應用中展現GPU和GPP所沒有的獨特優勢。

2019-10-18 15:48:14 1326

1326 近十年來,人工智能又到了一個快速發展的階段。深度學習在其發展中起到了中流砥柱的作用,盡管擁有強大的模擬預測能力,深度學習還面臨著超大計算量的問題。在硬件層面上,GPU,ASIC,FPGA都是解決龐大計算量的方案。

2019-10-22 15:26:21 977

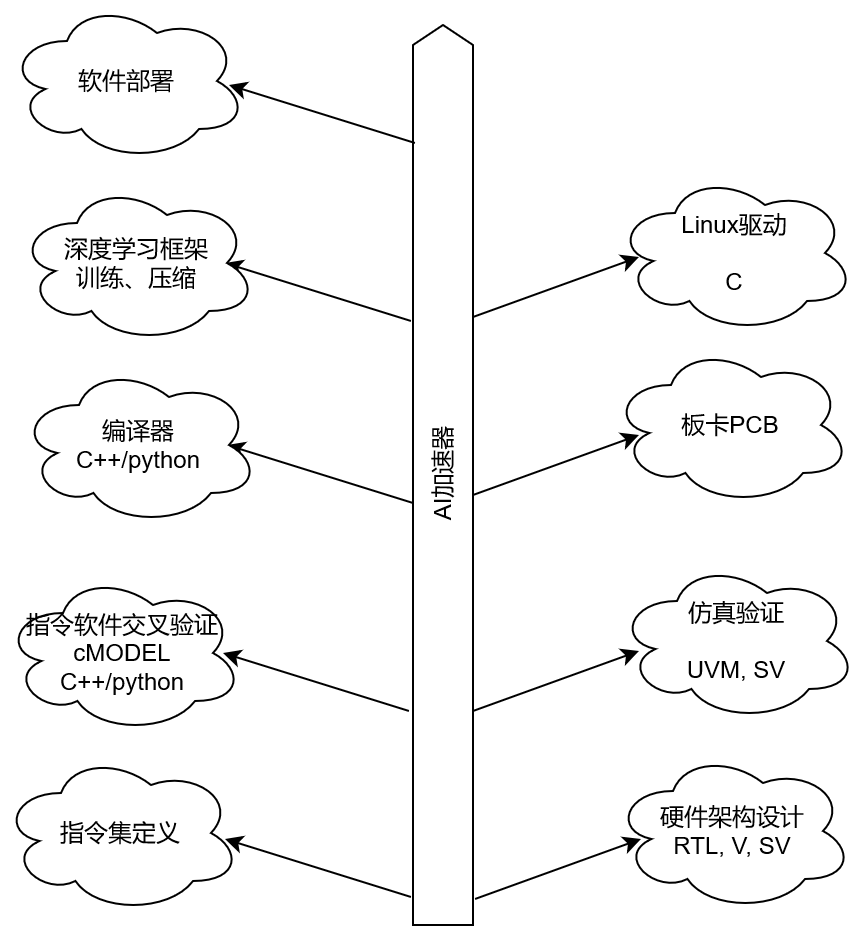

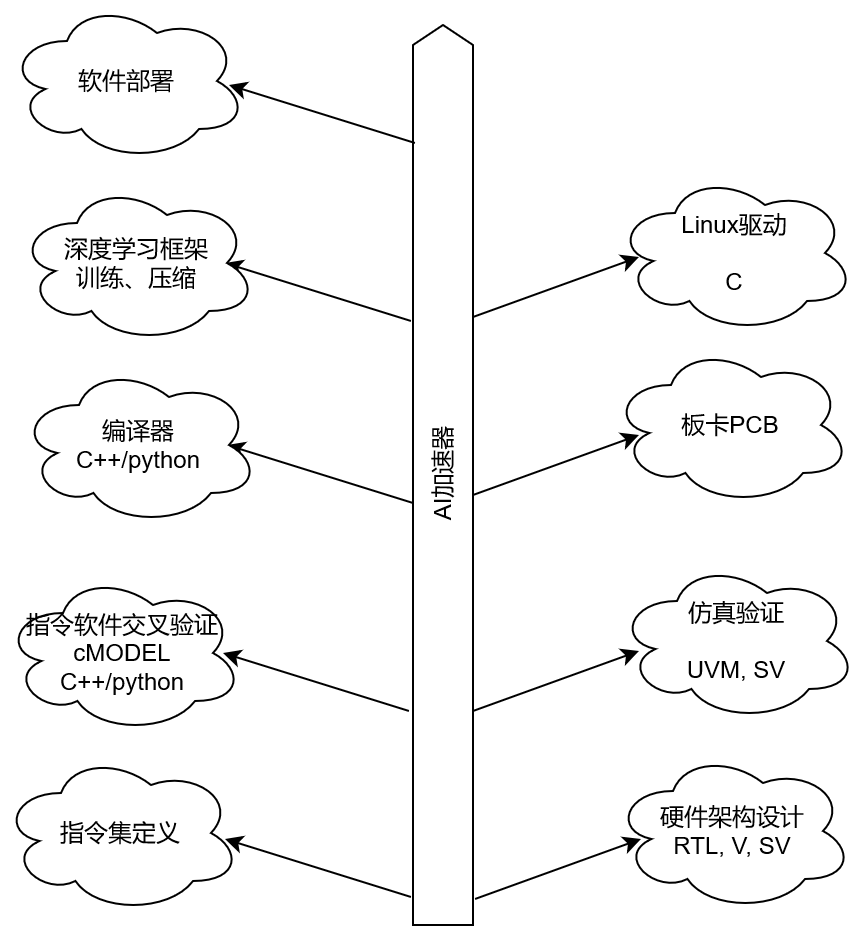

977 做深度學習加速器已經兩年了,從RTL設計到仿真驗證,以及相應的去了解了Linux驅動,深度學習壓縮方法等等。

2020-03-08 16:29:00 8342

8342

FPGA電路FIFO設計的源代碼

2020-07-08 17:34:37 15

15 近日,MIT卻發出警告:深度學習正在接近計算極限,必須轉變現有技術「大幅」提高計算效率。

2020-07-21 09:31:28 721

721 本篇文章用于總結之前學習的time quest,并且我已經能夠利用公式,計算出slack了,并能夠根據setup slack來更改優化代碼了。時光由隔了1個月,時序分析的路沒有終點,本篇文章是對之前

2021-01-13 16:02:00 10

10 FIFO是FPGA處理跨時鐘和數據緩存的必要IP,可以這么說,只要是任意一個成熟的FPGA涉及,一定會涉及到FIFO。但是我在使用異步FIFO的時候,碰見幾個大坑,這里總結如下,避免后來者入坑。

2021-03-12 06:01:34 12

12 由于平時我們工作中,FIFO都是直接調用IP核,對于FIFO深度選擇并沒有很在意,而在筆試面試過程中,經常被問及的問題之一就是如何計算FIFO深度。 當讀數據的速率小于寫數據的速率時,我們需要先將

2021-05-11 14:37:08 1950

1950

FIFO是在FPGA設計中使用的非常頻繁,也是影響FPGA設計代碼穩定性以及效率等得關鍵因素。在數據連續讀取時,為了能不間斷的讀出數據而又不導致FIFO為空后還錯誤的讀出數據。可以將FIFO

2021-09-09 11:15:00 6293

6293 FIFO 最小深度計算 例子 - 1:f_wr 》 f_rd,連續讀寫 寫時鐘80MHz。 讀時鐘50MHz。 Burst_Len = 120,也就是要求至少安全寫入120個數據。 連續寫入和連續

2021-09-10 09:23:28 1507

1507

FIFO最常被用來解決寫、讀不匹配的問題(時鐘、位寬),總結下來,其實FIFO最大的作用就是緩沖。既然是緩沖,那么就要知道這個緩存的空間到底需要多大。接下來的討論,都建立在滿足一次FIFO突發傳輸

2022-02-26 17:41:52 3045

3045

FIFO是FPGA項目中使用最多的IP核,一個項目使用幾個,甚至是幾十個FIFO都是很正常的。通常情況下,每個FIFO的參數,特別是位寬和深度,是不同的。

2022-03-08 11:06:12 4520

4520

在FPGA中對圖像的一行數據進行緩存時,可以采用FIFO這一結構,如上圖所示,新一行圖像數據流入到FIFO1中,FIFO1中會對圖像數據進行緩存,當FIFO1中緩存有一行圖像數據時,在下一行圖像數據來臨的時候,將FIFO1中緩存的圖像數據讀出,并傳遞給下一個FIFO

2022-05-10 09:59:29 3056

3056 由于平時我們工作中,FIFO都是直接調用IP核,對于FIFO深度選擇并沒有很在意,而在筆試面試過程中,經常被問及的問題之一就是如何計算FIFO深度。

2022-07-03 17:25:28 2222

2222 作者:凱魯嘎吉 來源:博客園 這篇文章對現有的深度聚類算法進行全面綜述與總結。現有的深度聚類算法大都由聚類損失與網絡損失兩部分構成,博客從兩個視角總結現有的深度聚類算法,即聚類模型與神經網絡模型

2022-12-30 11:15:08 648

648 這是新的系列教程,在本教程中,我們將介紹使用 FPGA 實現深度學習的技術,深度學習是近年來人工智能領域的熱門話題。

2023-03-03 09:52:13 1088

1088 當今的深度學習應用如此廣泛,它們能夠為醫療保健、金融、交通、軍事等各行各業提供支持,但是大規模的深度學習計算對于傳統的中央處理器(CPU)和圖形處理器(GPU)來說是非常耗時和資源密集的。

2023-03-09 09:35:24 1941

1941 FPGA(Field-Programmable Gate Array)是一種靈活的可編程硬件設備,它在深度學習應用領域中具有許多優勢。

2023-03-09 09:41:15 1350

1350 這是新的系列教程,在本教程中,我們將介紹使用 FPGA 實現深度學習的技術,深度學習是近年來人工智能領域的熱門話題。

2023-04-12 10:19:34 533

533 這是新的系列教程,在本教程中,我們將介紹使用 FPGA 實現深度學習的技術,深度學習是近年來人工智能領域的熱門話題。

2023-05-04 11:22:36 651

651

FIFO(First In First Out)是一種先進先出的存儲結構,經常被用來在FPGA設計中進行數據緩存或者匹配傳輸速率。

2023-08-07 15:39:50 446

446 什么是深度學習算法?深度學習算法的應用 深度學習算法被認為是人工智能的核心,它是一種模仿人類大腦神經元的計算模型。深度學習是機器學習的一種變體,主要通過變換各種架構來對大量數據進行學習以及分類處理

2023-08-17 16:03:04 1300

1300 ? 點擊上方 藍字 關注我們 ? 第一節:fifo基礎 ? ? 內容: 1. 掌握FPGA設計中關于數據緩存的使用 2. 掌握FIFO工作原理

2023-11-17 14:00:02 179

179

電子發燒友App

電子發燒友App

評論