4.4 流水燈的設計輸入

4.4.1 建立FPGA工程

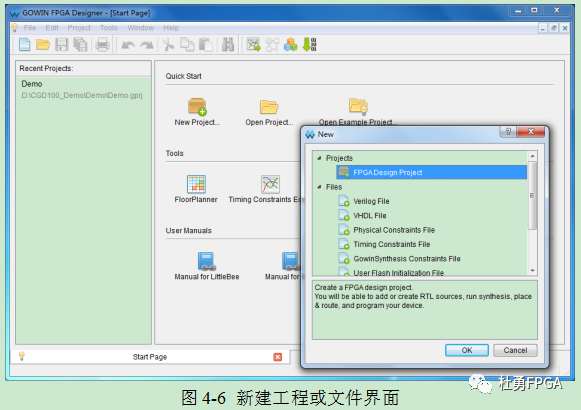

完成項目需求分析、電路圖分析以及方案設計后,接下來可以進行FPGA設計了。如果用戶的計算機已安裝云源軟件GOWIN FPGA Designer,雙擊桌面上的程序圖標,即可打開GOWIN FPGA Designer。在工作界面中依次單擊菜單“File→New”,可打開新建工程(Projects)或文件(Files)類型選擇對話框,如圖4-6所示。

?

圖4-6 新建工程或文件界面

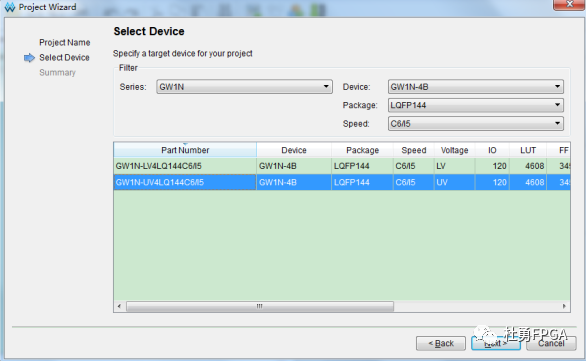

選中“Projects→FPGA Design Project”條目,或直接單擊主界面中的“Quick Start→New Project”圖標,即可打開新建工程對話框,在對話框中設置工程的名稱(waterlight)和存放路徑,單擊“Next”打開器件選擇(Select Device)對話框,如圖4-7所示。

?

圖4-7 FPGA 器件選擇界面

根據CGD100開發板上的FPGA器件型號,在器件系列(Series)列表框中選擇GW1N,器件(Device)列表中選擇GW1N-4B,封裝(Package)列表中選擇LQFP144,速度等級(Speed)中選擇C6/I5,圖中的列表框中自動篩選出CGD100開發板對應的FPGA型號GW1N-UV4LQ144C6/I5,選中該器件型號,依次單擊“Next→Finish”完成工程的創建,且軟件自動返回到主界面。

此時打開工程路徑所指向的文件夾,可以發現目錄中出現了兩個子文件夾“impl”、“src”以及CPRJ類型的工程文件waterlight。其中,impl文件夾存放工程編譯后的一些過程文件,src文件夾存放工程中新建的資源文件。可以雙擊waterlight.gprj直接啟動云源軟件并打開該FPGA工程。

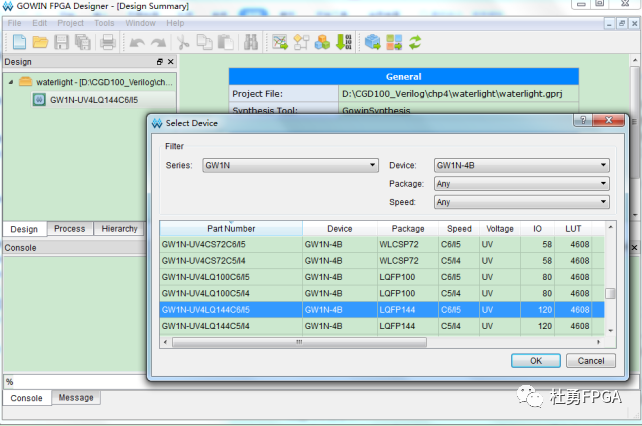

完成工程創建后,如需重新指定FPGA設計的目標器件,可以單擊云源軟件主界面中的目標器件名稱,打開器件設置界面重新指定目標器件,如圖4-8所示。

?

圖4-8 創建工程后重新設置目標FPGA器件界面

4.4.2 Verilog HDL程序輸入

完成FPGA工程建立后,開始編寫Verilog HDL程序代碼進行FPGA設計。AMD、Intel公司的FPGA開發環境均提供了原理圖方式及HDL代碼兩種輸入方式,云源軟件僅提供了HDL代碼輸入方式。原理圖的設計輸入方式類似于繪制電路圖的設計方式,雖然直觀,但十分不便于程序移植和后期代碼的維護修改,因此應用很少。本書均采用HDL代碼輸入的方式進行FPGA程序設計。

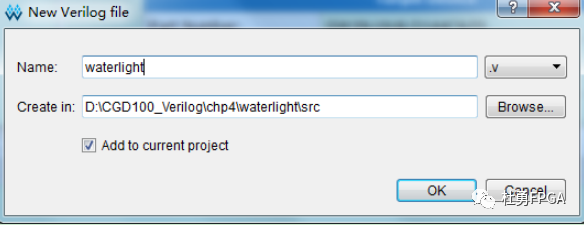

在GWIN FPGA Designer主工作界面中依次單擊菜單“File→New”,打開新建資源界面,在資源界面中選中“Files→Verilog File”,單擊“OK”,在文件名編輯框(Name)中輸入Verilog HDL文件名waterlight,文件存放目錄編輯框(Create In)自動設置為當前工程目錄下的src文件夾下,如圖4-9所示。

?

圖4-9 新建Verilog文件界面

單擊“OK”按鍵,完成Verilog HDL文件的創建,軟件主界面的工作區中自動生成名為“waterlight.v”的文件,且該文件處于打開狀態,可以在文件中輸入設計代碼。

在文件中輸入下列代碼。

//waterlight.v文件

module waterlight(

input clk50m, ?????????????//系統時鐘:50MHz

input rst_n, ???????????????//復位信號:低電平有效

output reg [7:0] led ?????????//8個LED燈

);

reg [29:0] cn=0;

always @(posedge clk50m or negedge rst_n)

if (!rst_n) begin

?????cn <= 0;

?led <= 8'hff;

?end

else begin

?if (cn>30'd8000_0000) cn <=0;

?else cn <= cn + 1;

?if (cn<30'd1000_0000) led <=8'b0000_0001;

?else if (cn<30'd2000_0000) led <=8'b0000_0010;

?else if (cn<30'd3000_0000) led <=8'b0000_0100;

??else if (cn<30'd4000_0000) led <=8'b0000_1000;

??else if (cn<30'd5000_0000) led <=8'b0001_0000;

??else if (cn<30'd6000_0000) led <=8'b0010_0000;

?else if (cn<30'd7000_0000) led <=8'b0100_0000;

?else led <=8'b1000_0000;

?end

endmodule

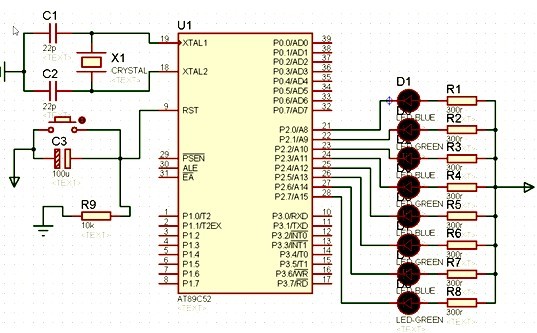

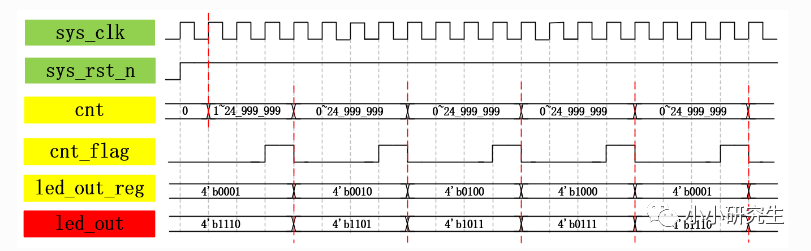

上述文件代碼實現的是一個8位流水燈功能電路,每個燈點亮0.2s的時間,依次循環點亮,實現流水燈效果。本章僅關注FPGA的基本開發流程,關于流水燈的設計思路及Verilog HDL語法細節將在后續章節逐步展開討論。

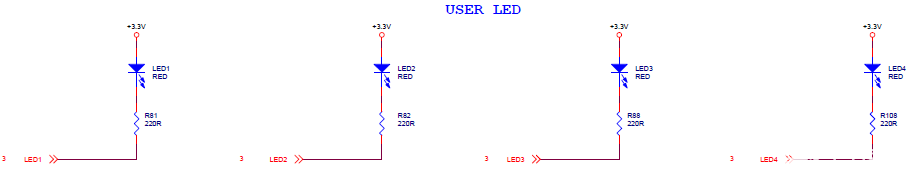

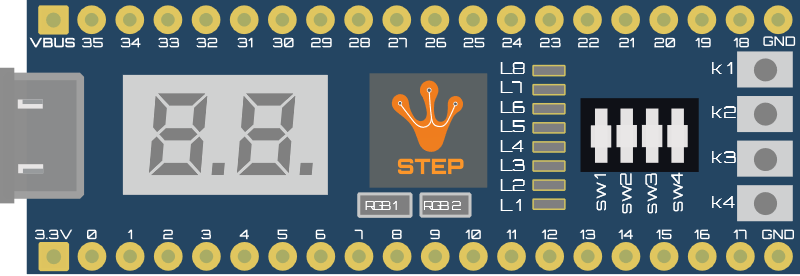

完成代碼輸入后保存文件。流水燈程序共有10個信號接口:時鐘信號clk50m、復位信號rst_n,以及8根LED燈信號。要使設計的程序能夠在FPGA開發板上正確運行,需要將程序的端口信號與CGD100電路板上的FPGA管腳關聯起來。完成信號與管腳關聯過程稱為物理管腳約束。

新建類型為“Physical Constraints File”,在文件中輸入下列代碼。

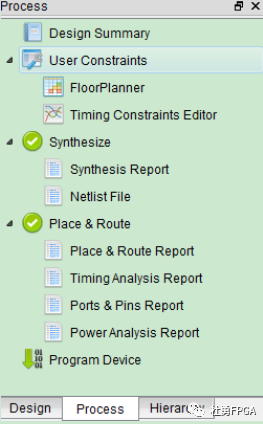

//CGD100.cst文件IO_LOC "clk50m" 7;IO_PORT "clk50m" IO_TYPE=LVCMOS33;IO_LOC "rst_n" 65; //k8IO_PORT "rst_n" IO_TYPE=LVCMOS33;IO_LOC "led[0]" 23;IO_LOC "led[1]" 24;IO_LOC "led[2]" 25;IO_LOC "led[3]" 26;IO_LOC "led[4]" 27;IO_LOC "led[5]" 28;IO_LOC "led[6]" 29;IO_LOC "led[7]" 30;IO_PORT "led[0]" IO_TYPE=LVCMOS33;IO_PORT "led[1]" IO_TYPE=LVCMOS33;IO_PORT "led[2]" IO_TYPE=LVCMOS33;IO_PORT "led[3]" IO_TYPE=LVCMOS33;IO_PORT "led[4]" IO_TYPE=LVCMOS33;IO_PORT "led[5]" IO_TYPE=LVCMOS33;IO_PORT "led[6]" IO_TYPE=LVCMOS33;IO_PORT "led[7]" IO_TYPE=LVCMOS33;至此,我們完成了流水燈例程的所有代碼輸入工作。雙擊GOWIN FPGA Designer主界面中的“Run All”工具按鍵,軟件自動完成工程的綜合及布局布線工作。如果代碼輸入正確,則軟件界面左側“Process”窗口中的“Synthesize”和“Place & Route”條目均會出現綠色的勾,表示程序綜合及布局布線正確,如圖4-10所示。

?

圖4-10 程序綜合及布局布線成功后的界面

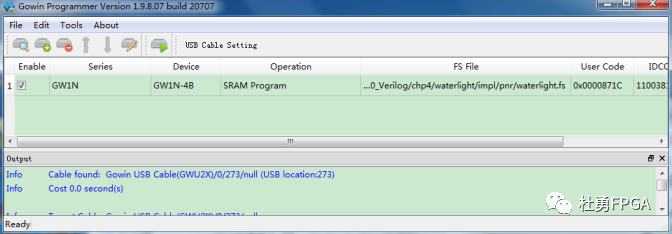

4.5程序文件下載

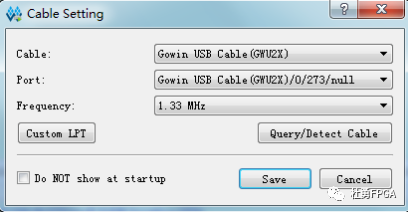

程序布局布線成功后,在工程目錄的“implpnr”路徑下會生成擴展名為fs的程序文件。對于流水燈工程實例來講,生成的程序文件為waterlight.fs。采用USB線連接CGD100開發板和電腦,雙擊“ Program Device”條目,啟動程序下載工具Gowin Programmer,同時彈出下載線設置對話框,如圖4-11所示。

?

圖4-11 程序下載線設置對話框

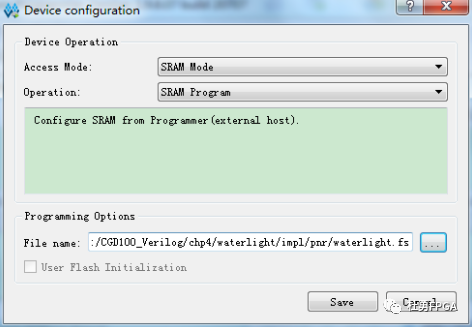

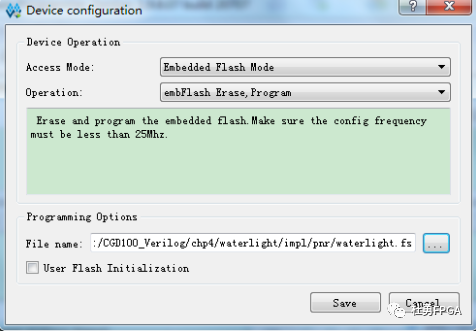

按圖4-11設置下載線狀態,單擊“Save”,返回到Gowin Programmer界面。設置“Series”為GW1N,“Device”為GW1N-4B。單擊“Operation”,打開下載模式設置界面。FPGA最主要的程序下載模式有兩種:SRAM模式及Embedded Flash模式,前者模式在掉電后程序即丟失,后者模式在掉電后程序不丟失。對于SRAM模式來講,在下載模式設置界面中,“Access Mode”選擇SRAM Mode,“Operation”選擇“SRAM Program”;對于Embedded Flash模式,在下載模式設置界面中,“Access Mode”選擇Embedded Flash Mode,“Operation”選擇“embFlash Erase,Program”。在“File name”編輯框中設置下載文件為工程布局布線后生成的waterlight.fs。兩種程序下載模式的設置界面如圖4-12、4-13所示。

?

圖4-12 SRAM模式下載模式設置界面

?

圖4-13 Embedded Flash下載模式設置界面

?

圖4-14 Gowin Programmer配置界面

完成設置后的Gowin Programmer界面如圖4-14所示。單擊“Program/Configure”工具按鈕即可完成程序的下載。程序下載完成后,可以觀察到CGD100的8個LED燈呈現流水燈效果。

4.6 小結

本章以流水燈實例為例詳細介紹了FPGA的設計流程。相對于AMD、Intel等FPGA廠商的FPGA開發環境來講,高云云源軟件的開發界面及流程都要簡單得多,因此更適合FPGA初學者快速掌握FPGA的設計流程。本章的學習要點可歸納為:

(1)了解FPGA的設計流程,并將設計流程與PCB設計流程進行對比分析。

(2)掌握云源軟件的基本使用方法及步驟。

(3)理解SRAM及Embedded Flash兩種下載模式的特點。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論