? FPGA是在PAL、PLA和CPLD等可編程器件的基礎上進一步發展起來的一種更復雜的可編程邏輯器件。它是ASIC領域中的一種半定制電路,既解決了定制電路的不足,又克服了原有可編程器件門電路有限的缺點。

由于FPGA需要被反復燒寫,它實現組合邏輯的基本結構不可能像ASIC那樣通過固定的與非門來完成,而只能釆用一種易于反復配置的結構,查找表-Look Up Table,LUT,可以很好地滿足這一要求。目前,主流FPGA都采用了基于SRAM工藝的查找表結構,也有一些軍品和宇航級FPGA采用Flash/熔絲/反熔絲工藝的查找表結構。

1 查找表結構及功能

由布爾代數理論可知,對于一個n輸入的邏輯運算,最多產生2^n個不同的組合。所以,如果預先將相應的結果保存在一個存儲單元中,就相當于實現了與非門電路的功能。

FPGA的原理的實質,就是通過配置文件對查找表進行配置,從而在相同的電路情況下實現了不同的邏輯功能。

1.1 輸入查找表結構

LUT本質就是一個RAM。自FPGA誕生以來,多使用4輸入的LUT,可以看成一個包含四位地址線的RAM。當設計者通過原理圖或HDL描述了一個邏輯電路后,FPGA廠商提供的集成開發工具就會自動計算邏輯電路的所有可能結果,并把真值表事先寫人到RAM中。這樣,每輸入一個信號進行邏輯運算就等于輸人一個地址進行查表,找出地址對應的內容,然后輸出內容即可。

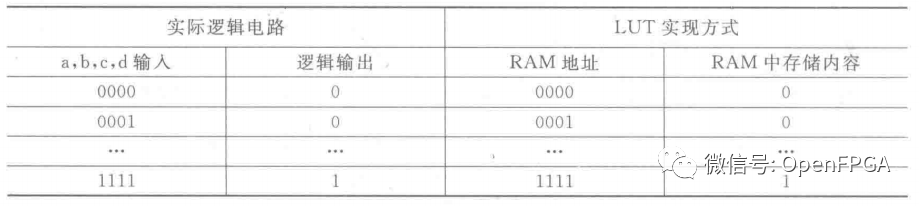

下面用一個4輸人邏輯與門電路的例子來說明LUT實現組合邏輯的原理。LUT描述四輸入邏輯與關系如表2.1所示。

表2.1 輸入與門的真值表

從表2.1可以看到,LUT具有和邏輯電路相同的功能,但是LUT具有更快的執行速度和更大的規模。與傳統化簡真值表構造組合邏輯的方法相比,LUT具有明顯的優勢,主要表現在:

(1)LUT實現組合邏輯的功能由輸入決定,而不是由復雜度決定。

(2)LUT實現組合邏輯有固定的傳輸延遲。

1.2 輸入查找表新結構

在65nm工藝條件下,與其他電路(特別是互連電路)相比,LUT的常規結構大大縮小。一個具有4倍比特位的6輸入LUT結構僅僅將所占用的CLB面積增加了15%,但是平均而言,每個LUT上可集成的邏輯數量卻提高了40%。當采用更高的邏輯密度時,通常可以降低級聯LUT的數目,并且改進關鍵路徑延遲性能。

新一代的FPGA提供了真正的6輸入LUT可以將它用作邏輯或者分布式存儲器,這時,LUT是一個64位的分布式RAM(甚至雙端口或者四端口)或者一個32位可編程移位寄存器。每個LUT具有兩個輸出,從而實現了五個變量的兩個邏輯函數,存儲32X2 RAM比特,或者作為6輸入16X2比特的移位寄存器進行工作。公眾號:OpenFPGA

LUT邏輯結構在每個LUT中融合了更多的邏輯塊,使用了較少的局部互連節點或更少的高電容節點(邏輯功能之間),降低了邏輯層次,從而縮短了路徑延遲。這種新的對稱布線還使相鄰邏輯之間的連接更加直接,進一步降低了布線電容。

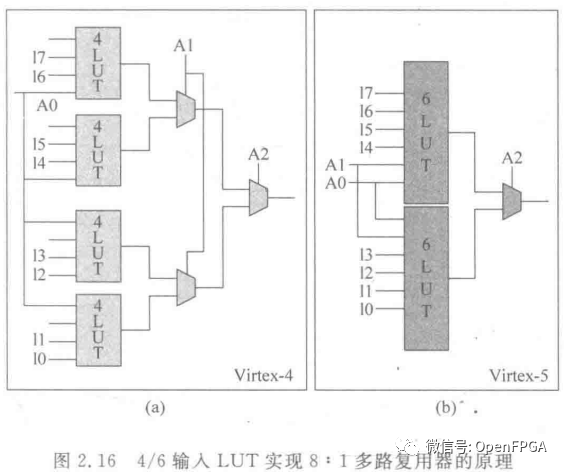

下面通過采用4和6輸入LUT實現多路選擇器(MUX)的例子來說明6輸入查找表的優勢。如圖2.16(a)所示,在4輸入LUT的結構中實現一個8:1的MUX需要四個4輸入LUT和三個MUXF模塊;如圖2.16(b)所示,在6輸入LUT的架構中實現同樣的8:1的MUX只需要兩個LUT和一個MUX模塊。因此,采用6輸入LUT結構時,所構造的邏輯 結構性能更高且利用率更好。

1.3可配置的邏輯塊

可配置的邏輯塊(Configurable Logic Block,CLB)是FPGA內主要的邏輯資源,用于實現時序和組合邏輯電路。7系列的CLB提供了高性能的FPGA邏輯:

真正的6輸人查找表:

雙LUT5(5輸人LUT))選項;

可作為分布式存儲器和移位寄存器;

用于算術功能的快速進位邏輯;

寬的多路復用器。

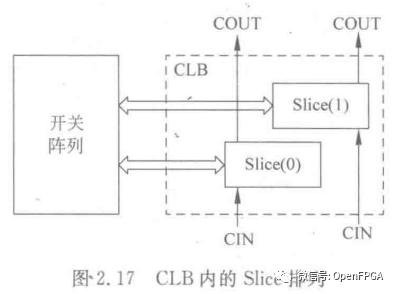

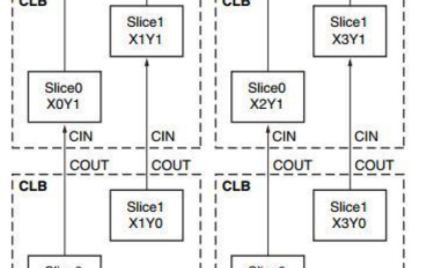

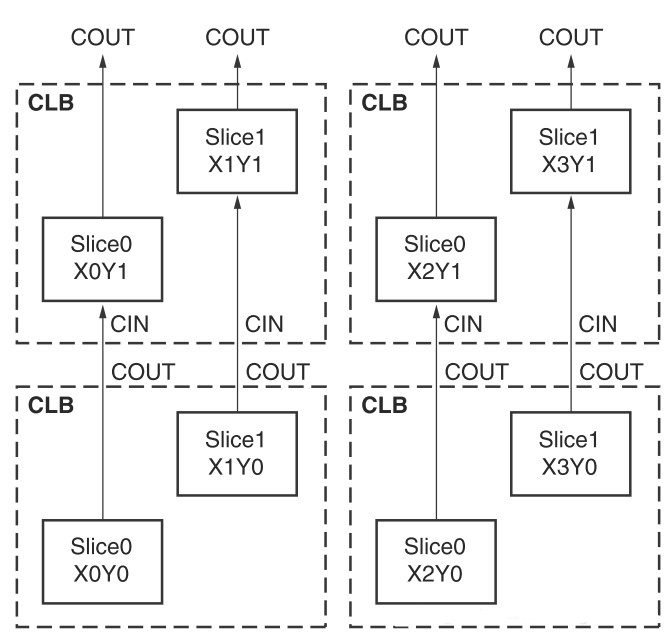

每個CLB連接到一個開關矩陣用于訪問通用的布線資源,如圖2.17所示。一個CLB包含兩個切片(Slice)每個切片中,包含4個6輸入的查找表、8個觸發器、多路復用器和算術進位邏輯。

注:這兩個切片沒有直接的相互連接,每個切片以列的形式排列在一起。

在7系列的FPGA中,大約2/3的Slice是SLICEL邏輯(L表示Logic),剩下的是SLICEM邏輯(M表示Memory)對于SLICEM來說,除了實現SLICEL內的邏輯功能外,它也能通過使用它內部的LUT構造出分布式的64位RAM或者32位的移位寄存器(SRL32)或者2個SRL16。

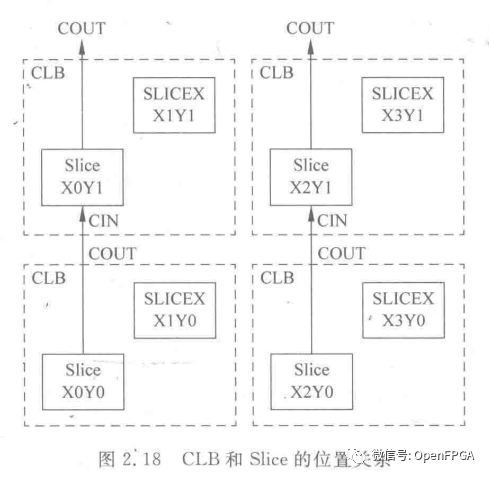

每個CLB由兩個Slice構成,如圖2.18所示。對于每個CLB來說:

(1)SLICE(0)在CLB的底部和左邊一列。

(2)SLICE(1)在CLB的頂部和右邊一列。

注:X后面的數字用于標識CLB內每個切片的位置,以及切片所在列的位置。

(1)X編號:切片位置從底部以順序0,1開始計算(第1列CLB),2、3(第2列CLB)等。公眾號:OpenFPGA

(2)Y編號:標識切片所在行的位置。在同一個CLB內Y后面的值是一樣的。計算從底部的CLB開始,從一行CLB遞增到下一行CLB。

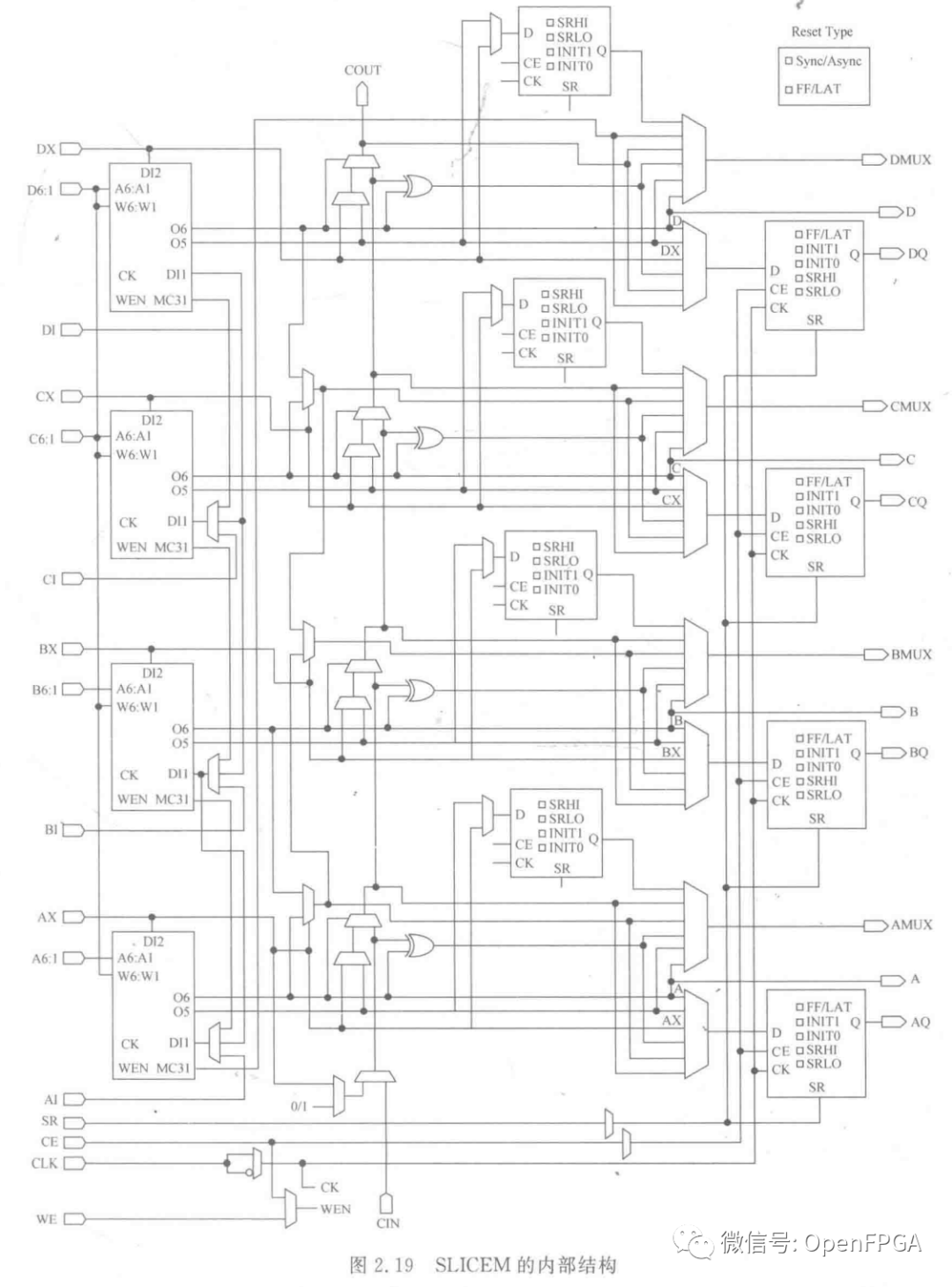

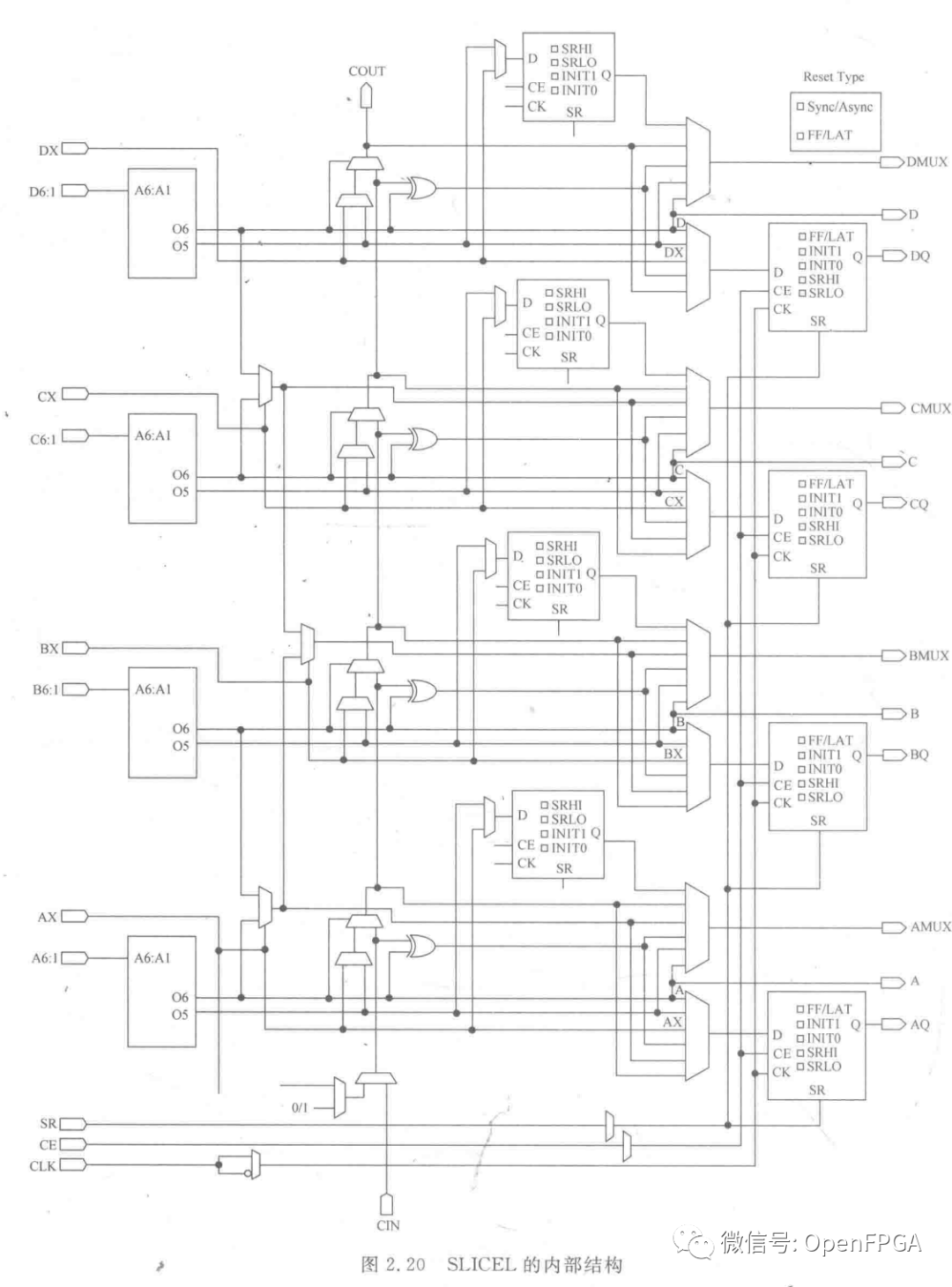

SLICEM的內部結構和SLICEL的內部結構分別如圖2.19和圖2.20所示。

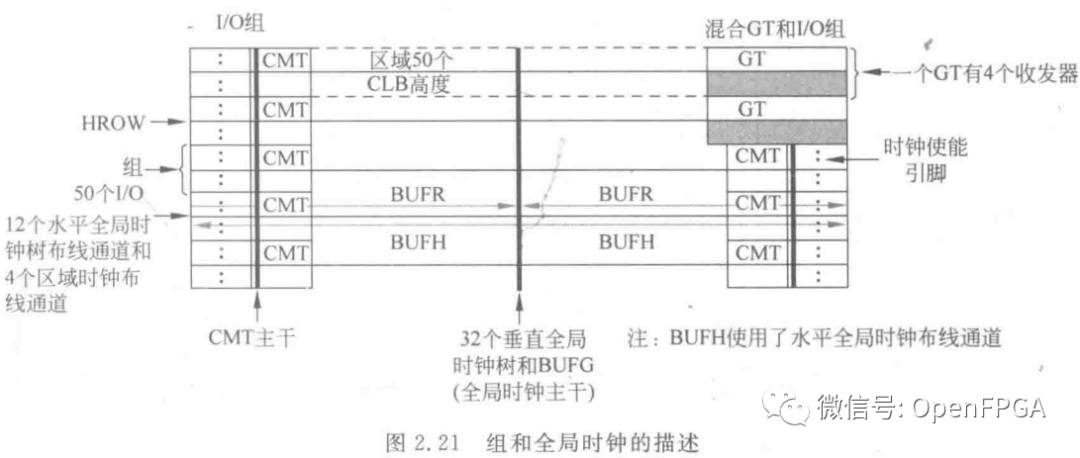

1.3時鐘資源

7系列的FPGA提供了6種不同類型的時鐘線,包括BUFG、BUFR、BUFIO、BUFH、BUFMR和高性能的時鐘,以此來解決不同的時鐘要求,這些要求包括高扇出、短傳遞延遲和特別低抖動。組和全局時鐘的描述如圖2.21所示。

1.全局時鐘

7系列FPGA提供了最高扇岀的32個全局時鐘線,它能到達每個觸發器時鐘,時鐘使能和置位/復位。通過水平時鐘緩沖區BUFH驅動在任何時鐘域的12個全局時鐘線。每個BUFH可以獨立地使能/禁止,并且允許關閉一個區域的時鐘,因此提供了細粒度控制時鐘域功耗的能力。全局時鐘緩沖區也能驅動全局時鐘線,可以實現無毛刺的時鐘復用和時鐘使能功能。全局時鐘常常由CMT驅動,能完全消除基本時鐘分布延遲。

2.區域時鐘

區域時鐘能驅動其區域內的所有時鐘目的。一個區域定義為一個包含50個I/O以及 50個CLB高度和跨越半個芯片寬度的區域 域內,提供4個時鐘跟蹤。通過4個時鐘使能(Clock-capable Clock,CCIO)輸入引腳的其中一個引腳,可以驅動每個區域時鐘緩沖區。在7系列FPGA中,有兩種類型的CCIO:兩個多區域(Multi-region Clock-capable,MRCC)和兩個單區域CCIO(Single-region Clock capable CLOCK,SRCC)。

CCIO的輸入為差分/單端模式,它用來驅動4個I/O時鐘BUFIO、4個區域時鐘BUFR以及本區域中任何一個CMT。公眾號:OpenFPGA

7系列FPGA引入了多時鐘區域緩沖區BUFMR提供了跨越區域/組的能力。

3.I/O時鐘

I/O時鐘頻率很高,它只用于I/O邏輯和串行/解串行電路。在7系列FPGA中,提供了從MMCM到I/O的直接連接,它為低扭曲和高性能接口提供時鐘。

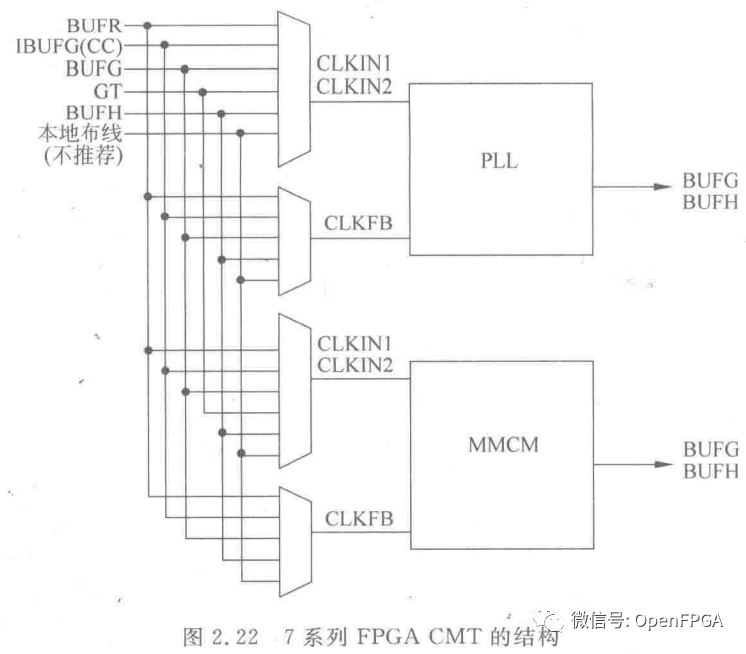

1.4時鐘管理模塊

7系列FPGA內的每個時鐘管理模塊(Clock Management Tile,CMT)包含一個混合模式的時鐘管理器(Mixed-mode Clock Manager,MMCM)和一個相位鎖相環(Phase Locked Loop,PLL)。PLL包含了MMCM功能的部分。

7系列FPGA內CMT的結構,如圖2.22所示,圖中給出各種時鐘源和MMCM/PLL的連接,輸人多路復用器從IBUFG、BUFG、BUFR、BUFH、GT或者本地互聯中,選擇參考源和反饋時鐘。

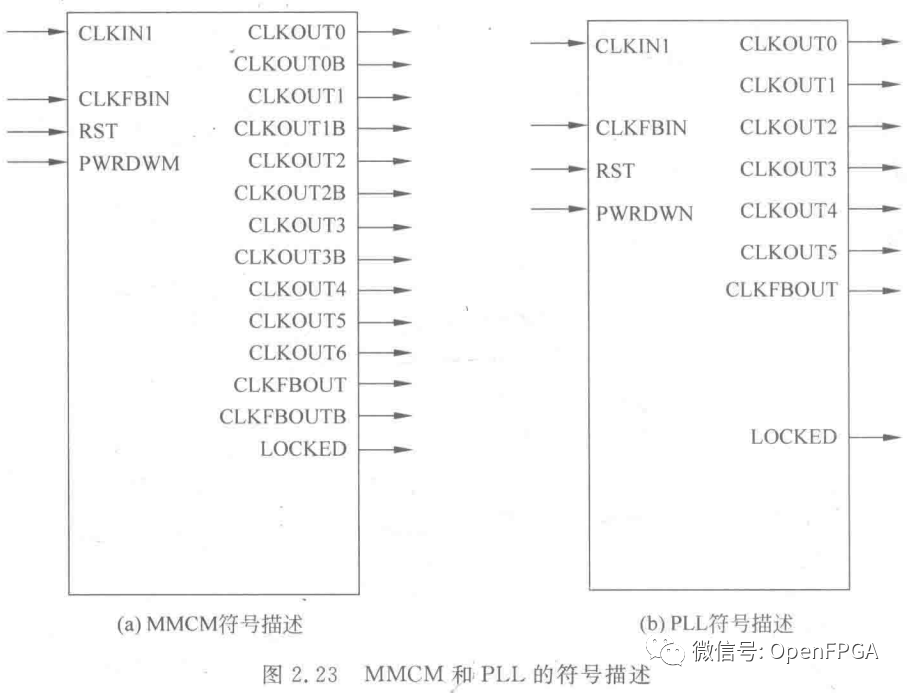

7系列的FPGA提供最多24個CMT。MMCM和Pll用于頻率合成器,用于寬范圍的頻率。MMCM和PLL的符號描述如圖2.23所示。

在7系列FPGA內,PLL是MMCM功能的一部分。MMCM支持的額外特性包括:

使用CLKOUT[0...3]實現到BUFR或者BUFIO的直接高性能路徑連接;

反相的時鐘輸出CLKOUT[0...3];

CLK0UT6;

CLK0UT4_CASCADE;

為CLKOUTO_DIVIDE_F行小數分頻;

為CLKFBOUT_MULT_F行小數倍頻;

細微的相位移動;

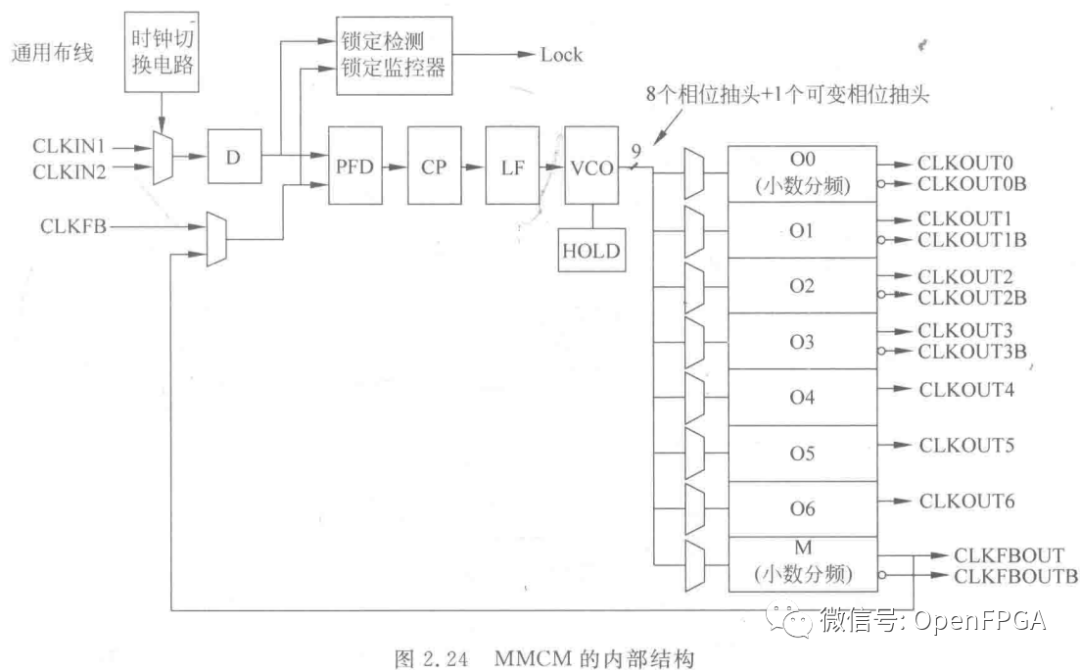

動態的相位移動。MMCM的內部結構,如圖2.24所示。MMCM的相位-頻率檢測器PFD用于比較輸入時鐘和反饋時鐘的上升沿頻率和相位。在兩個時鐘之間,PFD產生與相位和頻率成比例的信號,該信號驅動充電泵CP和環路濾波器LF,用于為壓控振蕩器VCO產生一個參考電壓。

1.5塊存儲器資源

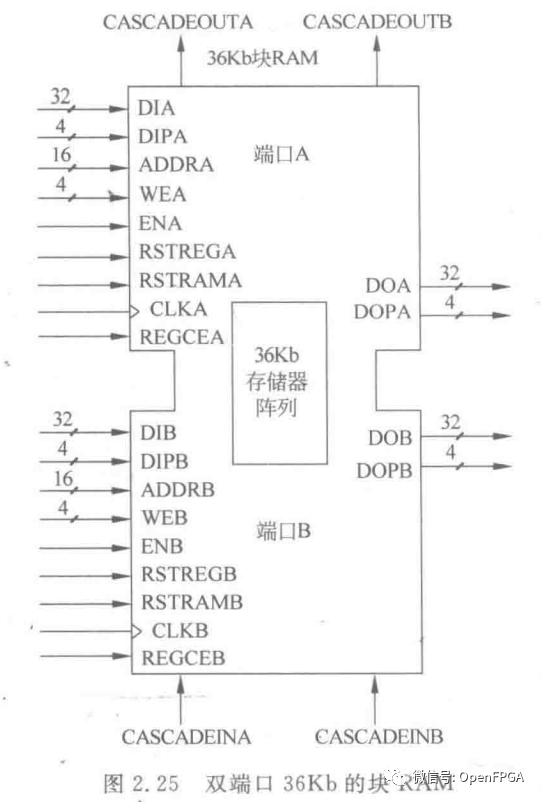

大多數FPGA都具有內嵌的塊RAM,這極大拓展了FPGA的應用范圍和靈活性。BRAM用于高效的數據存儲或者緩沖,可用于高性能的狀態機、FIFO緩沖區、大的移位寄存器、大的LUT或者ROM塊。RAM的結構如圖2.25所示。

7系列的FPGA提供了20?1880個雙端口的塊存儲器,每個BRAM的容量為36KB,在7系列FPGA內,BRAM的關鍵特性包括:

雙端口存儲器的數據寬度最多為72位;

可編程的FIFO邏輯;

內建可選的糾錯電路。

FPGA內的每個BRAM提供了兩個可訪問的端口,但是它也能配置為單端口RAM。

每個存儲器的讀/寫訪問由時鐘控制。所有的輸入數據、地址、時鐘使能和寫使能都經過寄存。輸人地址總是由時鐘驅動,一直保持數據,直到下一個操作。可選的輸出數據流水線寄存器,允許以一個額外時鐘的代價,產生更高的時鐘速率。

1.BRAM的配置

每個端口可以配置成32KX1、16KX2、8KX4、4KX9、2KX18、1KX36或者512X72。

兩個相鄰的BRAM能級聯構成一個64KX1的雙端口存儲器,且不需要添加任何邏輯。

注:上面的容量以比特計算。

2.檢錯和糾錯

每個64位寬的BRAM可以產生、保存和使用8位額外的海明碼。在讀過程中,可以糾正單比特錯誤以及檢測兩比特錯誤。在讀寫外部64?72位寬的存儲器時,也可以使用ECC邏輯。

3.UFO控制器

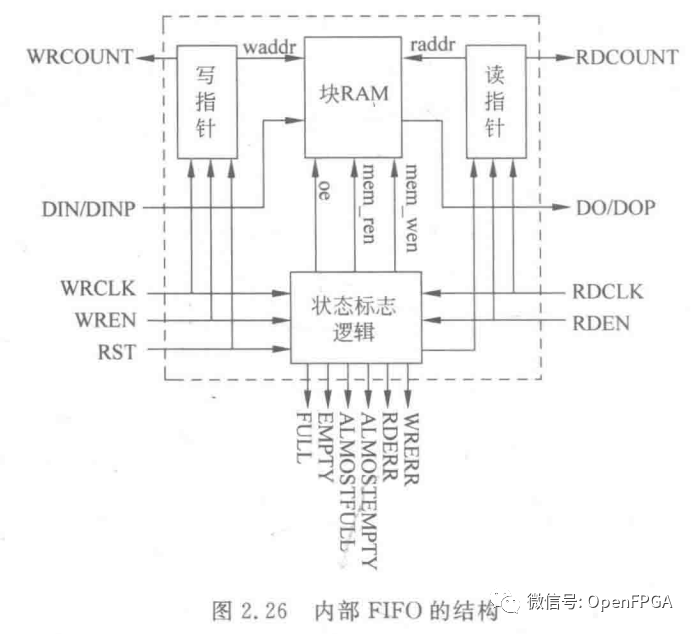

7系列FPGA提供了FIFO結構,內部結構如圖2.26所示。

該結構便用單時鐘(同步)或雙時鐘(異步)操作,遞增內部的地址,并且提供了4個握手信號線:full(滿)、empty(空)、almostfull(幾乎滿)和almostempty(幾乎空)。

注:1、可自由編程幾乎滿和幾乎空標志;2、FIFO的寬度和深度也可以編程,但是讀和寫端口總是相同的寬度;3、圖2.26中的讀寫指針專用于FIFO。

在首字跌落(First Word Fall-through)模式中,在第一個讀操作前,第一個寫人的字自動出現在數據輸出端。當讀取第一個字后,這個模式就和標準模式一樣了。

1.6互聯資源

互聯是FPGA內用于在功能元件,例如IOB、CLB、DSP和BRAM的輸人和輸出信號提供通路的可編程網絡。互聯也稱為布線以規則的陣列排列,被分段用于最優的連接。

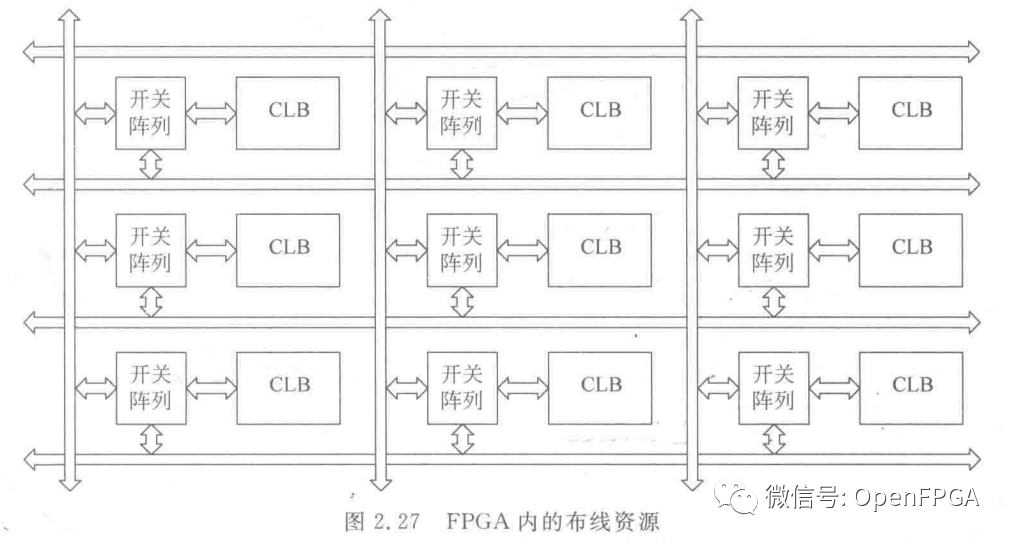

在7系列FPGA中,CLB以規則的陣列排列。每個島開關矩陣的連接用來訪問通用的布線資源,如圖2.27所示。

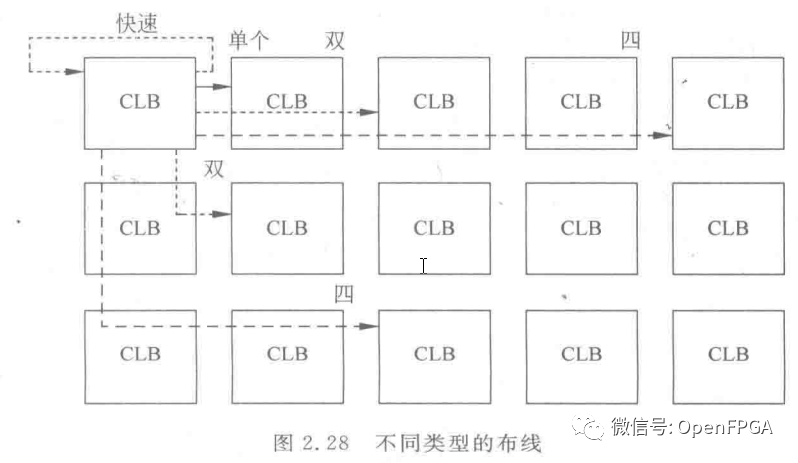

在7系列FPGA中,提供不同類型的布線,如圖2.28所示。這些布線通過長度來定義。互聯類型有:快速連接、單連接、雙連接和四連接。

(1)快速連接:將模塊的輸出連接到自己模塊的輸人。

(2)單連接:在垂直和水平方向上,布線連接到相鄰的單元。

(3)雙連接:在所有四個方向上,水平和垂直連接到所有其他的單元和對角線相鄰的單元。

(4)四連接:在水平和垂直方向上,每隔4個CLB連接一個單元或者以對角線方式連接到相隔兩行和兩列距離的單元。

1.7專用的DSP模塊

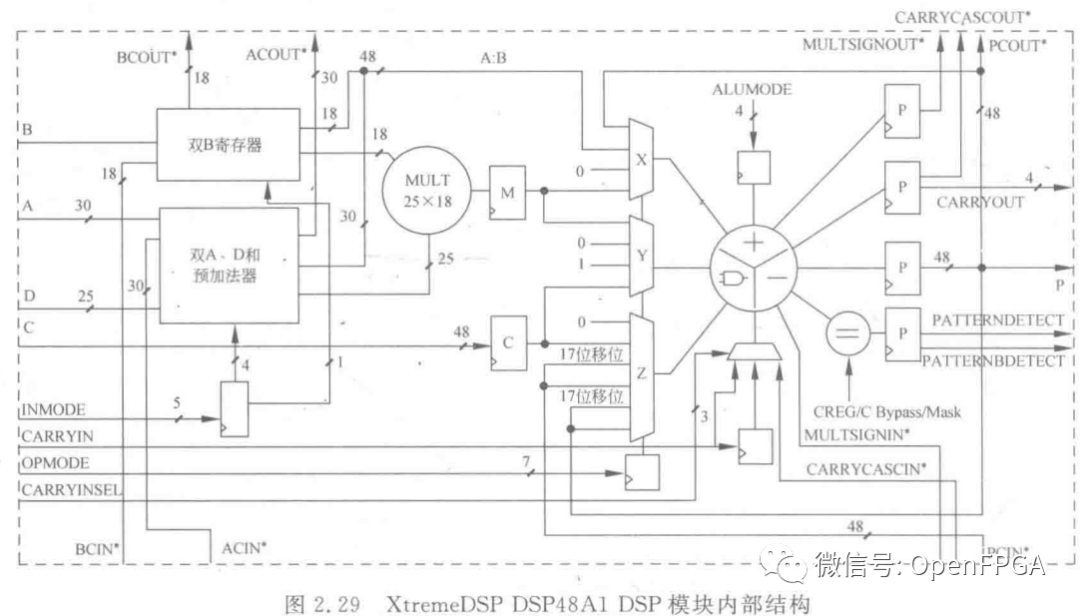

在7系列的FPGA中,集成了專用的、充分定制的低功耗的XtremeDSP ?DSP48E1 DSP模塊,其內部結構如圖29所示。其增強的特性主要表現在:

(1)25X18位的補碼乘法器/累加器,高分辨率48位信號處理器,其工作頻率最高可以達到638MHz;

(2)低功耗的預加法器可用于構建濾波器,它降低了所需的50% DSP Slice資源;

(3)高級的特性包括可選的流水線、可選的ALU以及用于級聯的專用總線。

在數字信號處理應用中,會使用大量的二進制乘法器和累加器,因此推薦在專用的DSP Slice中實現數字信號處理算法。在DSP Slice中,設計者可以動態選擇旁路掉乘法器。

此外,兩個48位的數據可以輸人到一個單指令多數據流SIMD算術單元(它可以實現雙24位加/減/累加,或者4個12位加/減/累加)操作,或者一個邏輯單元(它可以實現10種不同的邏輯功能運算)。

在DSP Slice中還提供一個48位的模式檢測器,用于收斂或者對稱的四舍五人操作。當它與邏輯單元一起使用時,模式檢測器也可以實現96位寬度的邏輯功能。

DSP Slice所提供的流水線以及擴展功能,顯著提高了數字信號處理算法的處理速度和處理效率。

1.8 輸入和輸出塊

7系列FPGA對輸入和輸出進行了優化,這樣可以在物理級和邏輯級上滿足不同的要求,這些要求包括高速存儲器、網絡、視頻平板和傳感器接口,高速的ADC/DAC連接,以及傳統接口。7系列的FPGA使用了統一的I/O架構。公眾號:OpenFPGA

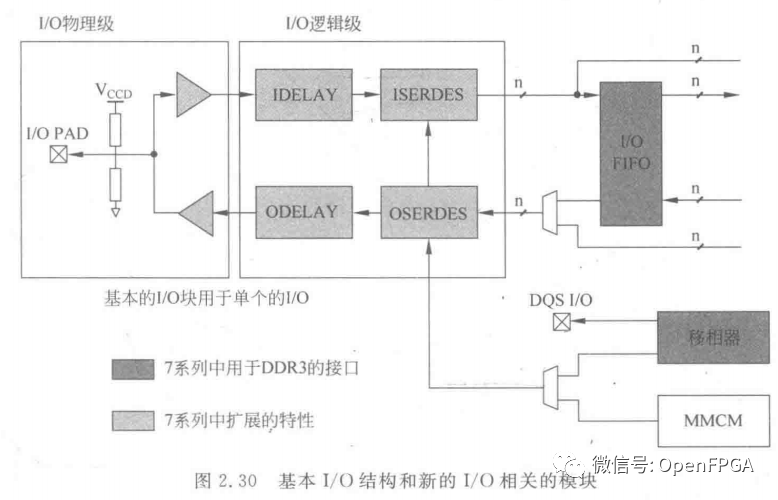

物理I/O能力和結構提供了一個I/O標準范圍、端接和低功耗模式。每個I/O組的I/O數量,它們相對時鐘和新I/O資源放置的位置以及I/O在FPGA晶圓上的排列順序同等重要。此外,I/O綁定邏輯功能,例如輸入/輸岀延遲和串行化/解串行化功能,它對于支持高帶寬應用也非常關鍵。在I/O上所增加的新功能,如移相器、PLL和I/O FIFO完整接口特性,可用于支持最高性能的DDR3以及其他存儲器接口。基本I/O結構和新I/O相關的模 塊,如圖2.30所示。

1.I/O物理級

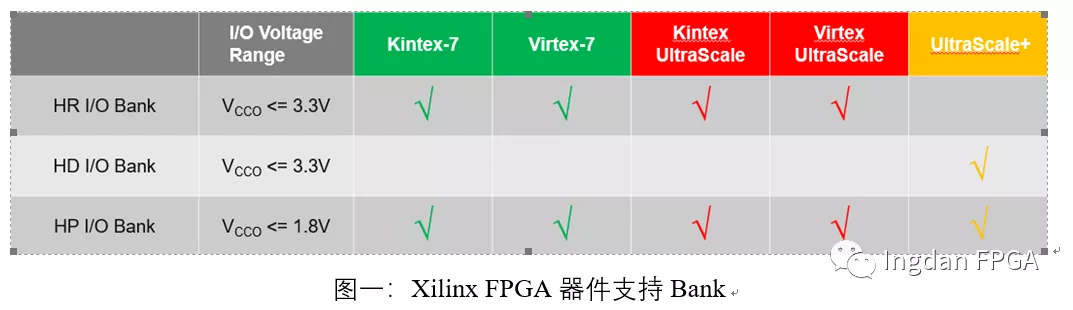

在物理級上,I/O要求支持一個給定范圍的驅動電壓和驅動強度,以及功能接口可接受的不同I/O標準。此外,I/O也支持不同的輸入/輸出端接特性。在7系列的FPGA中,支持兩種不同類型的I/O。

(1)高性能(High Performance,HP)I/O。在I/O組中,將它們稱為HP I/O組。

(2)寬范圍(High Range,HR)I/O。在I/O組中,將它們稱為HR I/O組,它支持寬范圍的I/O標準。

在7系列FPGA中,這兩種I/O類型被分別綁定到一個包含50 I/O的整個I/O組內。

(1)在Artix-7系列的FPGA中,只有3.3V的HR I/O組。

(2)在Virtx-7和Kintex-7系列的FPGA中,既有HP I/O組,也有HR I/O組。

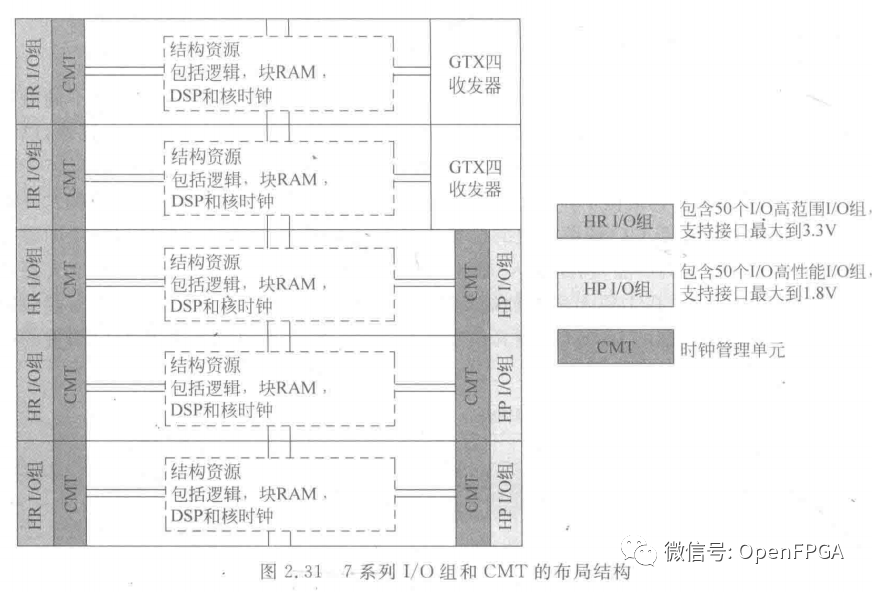

下面詳細介紹HP I/O和HR I/O組。Kintex-7 XC7K160T的I/O組和CMT的布局結構如圖2.31所示。

用于存儲器接口的I/O電源主要有三個元件:

(2)參考輸入接收器,用于將I/O電壓調整到核電壓。

(3)IDELAY用于將信號同步到時鐘。

2.I/O邏輯級

在7系列FPGA中,所有I/O都能被配置成組合或者寄存方式。所有的輸入/輸出支持雙數據率(Double Data Rate, DDR),通過對IDEALY和ODELAY編程,可以對任何一個輸入和某些輸出進行延遲。

每個I/O塊包含一個可編程的絕對延遲原語IDELAY2。IDELAY可以連接到ILOGICE2/ISERDESE2或者ILOGICE3/ISERDESE2模塊。每個HP I/O組包含一個可編程絕對延遲原語稱為ODELAY2。

注:

(1)原語(primitive)是指FPGA內部的基本功能模塊。

(2)對于HR I/O組來說,不提供ODELAY2原語。

此外,對于很多應用而言需要.連接外部高速設備。在這些應用中,往往外部提供高速的串行比特流,然后轉換成FPGA內并行低速的寬字節操作。因此,要求在I/O結構內提供一個串行化器和解串行化器。在7系列FPGA的每個I/O引腳中,提供了8位IOSERDES原語,它可以實現串行-并行或并行-串行之間的轉換。

注:

7系列內用于精確實現ISERDES的原語是ISERDESE2,精確實現OSERDES的是OSERDESE2。

1.9 吉比特收發器

在7系列FPGA內,提供吉比特收發器,其重要特性包括:

(1)高性能的收發器,其速率最高可以達到6.6Gb/s(GTP)、12.5Gb/s(GTX)、13.1Gb/s(GTH)和28.05Gb/s(GTZ)。

(2)優化的低功耗模式,用于芯片到芯片的接口。

(3)高級的預發送和后加重、接收器線性CTLE以及判決反饋均衡(Decision Feedback Equalization,DFE),包括用于額外余量的自適應均衡。

目前,與光纖和PCB內IC直接、背板、長距離的超高速串行數據發送,變得日益流行,因此,要求專業的專用片上電路和差分I/O能應對這些高數據率的信號完整性問題。

注:Artix-7和Kintex-7系列內提供了0?32個收發器電路。Virtex-7系列提供最多96個收發器。

每個串行收發器是發送器和接收器的組合。不同7系列的串行收發器使用了環形振蕩器以及LC諧振的組合。每個收發器有大量用戶定義的特性和參數,它們可以在配置設備的時候進行定義,某些參數和特性甚至可以在操作的時候進行修改。

發送器是一個并行-串行的轉換器,轉換率為16、20、32、40、64或80。此外,GTZ發送器支持最多160位的數據寬度。這些發送器的輸出使用差分輸岀信號驅動PC板。通過一個可選的FIFO以及額外的硬件,輸人數據支持8B/10B、64B/66B和64B/67B編碼策略。

接收器是一個串行-并行的轉換器,它將接收到的位串行差分信號變成并行的字流,其寬度為16、20、32、40、64或80位。此外,GTZ接收器支持最多160位的數據寬度。接收器將接收的差分數據流送到FPGA內可編程的線性和判決反饋均衡器,使用參考時鐘來初始化時鐘識別。數據模式使用NRZ編碼。

1.11 XADC模塊

在“數字化革命”時代,模擬技術的需求依然強勁。嚴格定義來說,常用于測量真實世界信息的大多數傳感器都是模擬電路。電壓、電流、溫度、壓力、流量和重力等均屬于連續的時域信號。由于數字技術具有高度的精確性和可重復性,它常用于監控和控制這些模擬信號。數據轉換器(包含ADC DAC和模擬多路復用器),為數字世界和模擬世界架起了至關重要的橋梁。

隨著模擬傳感器市場和數字控制系統市場的不斷發展,對連接模擬世界和數字世界的需求持續增長。推動模擬混合信號技術市場發展的因素包括智能電網技術、觸摸屏、工業控制安全系統、高可用性系統、先進馬達控制器,以及對各種設備更高安全性的需求。

2005年,隨著Virtex-5系列FPGA的推出,Xilinx意識到有必要集成名字為System Monitor的子系統以支持模擬混合信號功能。通過System Monitor子系統,設計人員可實現對FPGA關鍵性指標和外部環境的監控。

在經歷兩代FPGA產品之后,Xilinx進一步強化了這方面的工作,推出了具備模擬混合信號功能的Artix-7、Kintex-7和Virtex-7 FPGA以及Zynq-7000 SoC通過在7系列FPGA內集成兩個獨立通用1MHz釆樣率的12位分辨率ADC。顯著增強了嵌入式模擬子系統的功能。該功能強大的模擬子系統與高度靈活、功能強勁的FPGA邏輯緊密結合,實現了高度可編程混合信號平臺—靈活混合信號解決方案。

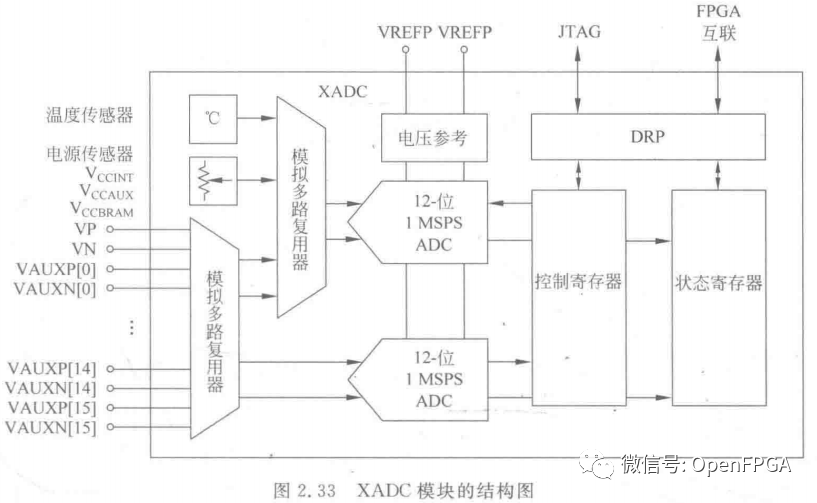

需要注意是,Xilinx的FPGA也在向混合信號處理方向發展。與Xilinx前幾代FPGA系列產品相比,采用28nm工藝的7系列FPGA擴展了模擬子系統的功能。在7系列FPGA中,將模擬子系統命名為XADC。在XADC中,包含兩路獨立的12位1MHz采樣率模數轉換器(ADC)以及一個17通道模擬多路復用器。這種將模擬系統與可編程邏輯結合的全新技術被XIlinx稱為靈活混合信號處理(AMS)技術。

7系列XADC模塊的內部結構,如圖2.33所示。該ADC(XADC)子系統包括:

(1)17個支持單極性和雙極性模擬輸入信號的差分模擬輸入通道。

(2)可選擇片上或者外部參考電源。

(3)提供片上電壓和溫度傳感器。

(4)采樣序列控制器。

(5)片上傳感器的可配置閾值邏輯及相關告警功能。

其中,控制和狀態寄存器為數字可編程邏輯提供了無縫接口。

XADC提供兩種類型的接口:JTAG接口和XADC FPGA接口。

XADC的一項獨特功能就是能夠通過JTAG端口直接訪問,因此無需占用FPGA資源源。也不必配置FPGA JTAG訪問同時支持數據和控制,可以讓JTAG提供另一級功能和系統健康狀況監控。負責控制JTAG總線的中央處理器能夠采集遠程的功率、溫度和其他模擬數據,然后執行系統范圍內的系統監控。對高可靠性系統,靈活混合信號提供了一種監控系統、控制冗余硬件和報告需求的低成本途徑。Vivado提供的分析器為訪問片上傳感器 的信息以及通過JTAG配置XADC.提供了便利的訪問途徑。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論