久違的科普整理欄目回來了,去年年底結束的ICCAD上,本土的EDA企業數量又增多了。這一期,我們就來聊一聊EDA相關的FPGA原型驗證。

如果大家有什么想了解的內容,可以在后臺留言,我們會盡力去整理、編撰相應的短文,與大家分享獲得的知識點。

什么是FPGA原型驗證?

EDA工具的使用主要分為設計、驗證和制造三大類。驗證工作貫穿整個芯片設計流程,可以說芯片的驗證階段占據了整個芯片開發的大部分時間。從芯片需求定義、功能設計開發到物理實現制造,每個環節都需要進行大量的驗證。

大規模集成電路設計復雜性的提升,使芯片驗證面臨資金與時間的巨大挑戰。早期開發者想驗證芯片的設計是否符合預設,只有等待漫長的模擬結果,或是等待流片成果。時間成本和經濟成本都較高。

現如今驗證方法也越來越多,例如:邏輯仿真(功能驗證),形式驗證,原型驗證。功能驗證基于軟件,驗證成本較低,驗證環境方便,但性能較差;形式驗證為靜態驗證方式,但不可仿真DUT的一些動態行為。

而開發者即可通過用FPGA板拼湊出有效的流程來對設計進行驗證,FPGA原型驗證這一解決方案就此應運而生。

FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產品(ASSP)和片上系統(SoC)的功能和性能。

FPGA原型驗證,是SoC基于FPGA的一種驗證方式,一般是在前端RTL設計和RTL仿真之后。FPGA和ASIC前端代碼都是基于 Verilog HDL 開發的,所以ASIC代碼理論上是可以在FPGA平臺上跑起來的,在流片之前,盡可能的去確定芯片功能的正確性的一種驗證方式。

FPGA的應用范圍廣泛,且基于FPGA可以反復擦寫,使用的語言和ASIC設計都是一樣的,因而被當作一種性價比優越的芯片驗證基礎設施。FPGA原型驗證已是當前原型驗證的主流且成熟的芯片驗證方法。

FPGA原型在數字芯片設計中非常重要,因為相比用仿真器,或者加速器等來跑仿真,FPGA的運行速度,更接近真實芯片,可以配合軟件開發者來進行底層軟件的開發。這一流片前的軟硬件的協同開發,是其最不可替代的地方。

為什么要做原型驗證

1、在流片之前,盡可能還原芯片真實使用場景,達到充分驗證芯片功能的目的,確保功能模塊的可靠性和穩定性,評估其性能;

2、可以縮短芯片類產品上市的時間,也可以給有需求的客戶演示,開始預售;

3、原型驗證可以降低成本,在芯片原型驗證這個階段,改代碼相對容易很多,可以節省大量成本;也可以給軟件設計人員提供驗證平臺。

原型驗證的原則

1、在芯片設計中,FPGA所有工作都是為芯片服務的;

2、在芯片設計中,芯片的邏輯規模遠大于FPGA設計邏輯。一般FPGA原型驗證都選用資源邏輯相對多的FPGA芯片,同時一要對芯片邏輯進行正確的分割;

3、在芯片設計中,芯片的主頻遠高于FPGA平臺上的時鐘。在原型驗證過程中,一定要做的就是降低主頻。

用FPGA對ASIC進行原型驗證

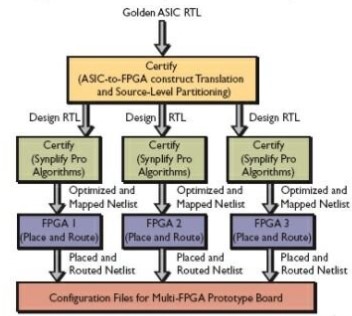

ASIC→FPGA原型步驟:

1.FPGA選型

需考慮:容量(純邏輯容量,存儲容量,DSP單元容量等)、內置IP(時鐘,存儲控制,CPU等硬核)、接口(普通接口與專用高速接口)、速度(資源占用率在50%左右時的速度,一般被用來評估原型)

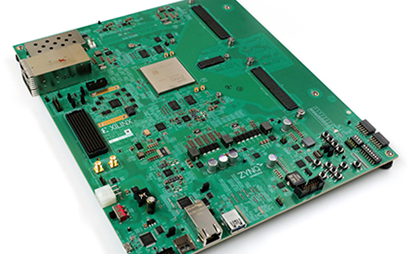

2.做板或者購買原型板

3.將ASIC設計轉換裝入FPGA

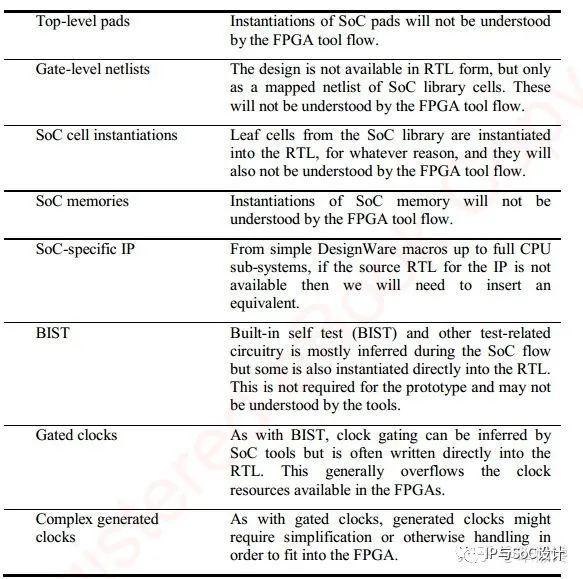

以下內容需要修改:

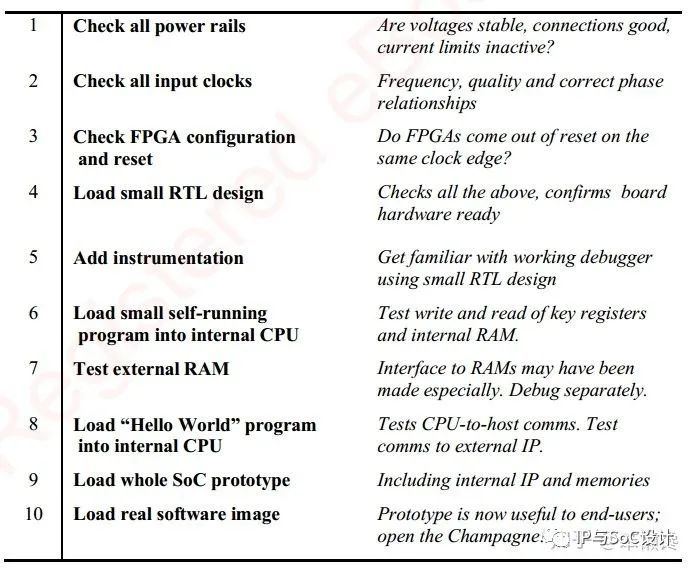

4.調試啟動FPGA原型

5.載入軟件協同運行

6.軟硬件系統驗證

FPGA原型驗證的優缺點

FPGA原型設計的優點是什么

性能?

FPGA通常建立在最新的制造流程上,以實現最高的密度和運行速度。即使是采用主流工藝構建的FPGA,也可以提供高門限等效計數(FPGA通常以可容納多少個標準查找表來衡量)。

超過最大FPGA功能的設計有時在多個FPGA上進行原型設計。這使得將源RTL映射到FPGA原型環境變得更加困難,并且可能會降低原型的性能。?

成本?

FPGA是批量生產的芯片,具有競爭力的價格。許多公司將它們集成到現成(OTS)原型板上,盡管一些公司更喜歡建立自己的原型印刷電路板(PCB) 。?

基礎設施?

兩家主要FPGA供應商(原型設計市場領導者Xilinx及其競爭對手Altera)都提供了廣泛的工具來支持他們的產品。他們還與主要的EDA供應商建立了聯盟,這些供應商為軟件套件提供了增強的FPGA原型設計。?

其他OTS主板供應商也與這些和其他工具供應商以及他們自己的軟件有合作關系。?

可移植性?

FPGA板可以在與最終SoC相同的嘈雜環境中進行測試。這對于打算用于便攜式消費設備以及工業,通信基礎設施,醫療和軍事/航空航天市場的產品有益。?

可用性

FPGA原型的成本相對較低意味著公司通常可以構建其中的幾個,這加速了硬件驗證,軟件開發,硬件/軟件協同驗證和軟件驗證。每個團隊都可以有自己的原型。?

FPGA原型驗證的缺陷

-編譯時間比較長

-debug方式不是特別成熟

FPGA原型驗證面臨的技術挑戰?

分區

大型設計可能需要在多個FPGA之間進行分離(分區)以實現所需的門控容量。這項任務通常被認為是FPGA原型設計的最大挑戰。?

分區過程本身很可能是一個棘手的迭代過程,涉及將設計映射到設備的眾多判斷調用,以及從RTL或軟件中的實際錯誤中過濾出并糾正映射錯誤。?

手動干預

FPGA原型設計可能需要幾種類型的手動干預。?

由于原始設計RTL被轉換為FPGA綜合和布局工具所需的硬件描述語言(HDL),因此即使工具已經實現了大部分翻譯的自動化,也可能需要一些手動編碼才能使原型工作。? ?

映射的各個方面都面臨著挑戰。FPGA上的時鐘樹路由(特別是原始設計具有門控時鐘的地方)非常困難。如果允許關鍵路徑通過緩慢的芯片到芯片到芯片路徑運行,原型性能將會受到影響。原創中的內存和加密塊也會帶來重大困難。? ?

調試可見性

可用的可見性往往局限于單個FPGA,這使得跨多個FPGA映射的設計使調試可見性變得更加困難。? ?

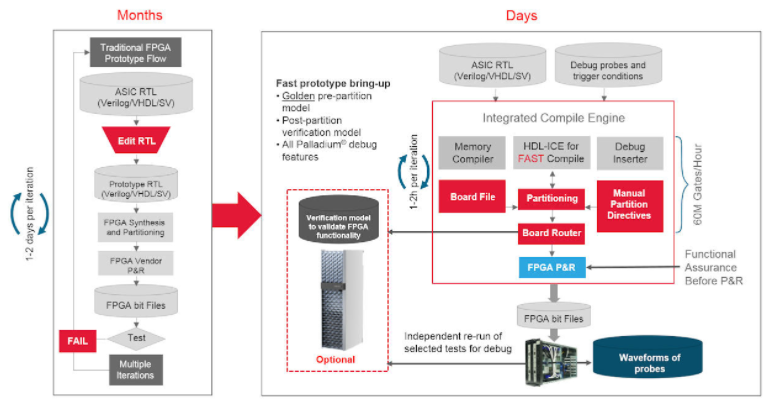

編譯時間

編譯FPGA原型如果產生錯誤,修復錯誤后,需要從頭開始重新編譯。這會造成很嚴重的延誤。

容量限制和性能要求

對于大型的設計(大于2千萬等效ASIC門),一塊FPGA往往容納不下,此時必須將多塊FPGA互聯才能驗證整個設計,在這種情況下,就需要對大型的設計進行Partition即分割。Partition引入了新的問題,而這些問題其實在芯片中并不存在,很多時候耗費很多人力去實現一個可用的Partition方案,僅僅是受限于FPGA的容量而不得已的處理辦法。Partition引入的最大問題是對I/O的需求激增。另一個方面,由于在SoC原型驗證中模塊常常會增減,導致需要頻繁的改動Partition方案,如果手動去處理,則需要花費很多精力才能得到一個上文提到可用但折中的方案。此外,處理大量的Cross-FPGA信號非常容易出錯,所以對于大型的SoC FPGA原型驗證,必須采用自動化的工具去完成Partition,這對EDA工具而言亦是全新的挑戰。

迭代速度

由于SoC芯片的設計頻率很高,為了讓原型驗證平臺盡可能和SoC芯片性能接近,開發者期望讓FPGA原型平臺運行在盡可能高的頻率上,但是由于SoC的RTL代碼是為芯片實現設計,大量深層次組合邏輯的存在,導致了SoC RTL代碼在FPGA上實現時時序收斂困難。

可觀測性

FPGA也是芯片產品,所以內部的信號無法直接觀測。通常需要借助于FPGA的Debug工具在生成Bit文件前選取要觀察的信號。當Bit文件加載運行時,必須通過配套的Debug工具觀察指定的信號波形,但是受限于Block RAM的容量以及信號優化等原因,如此調試的效率比較低。

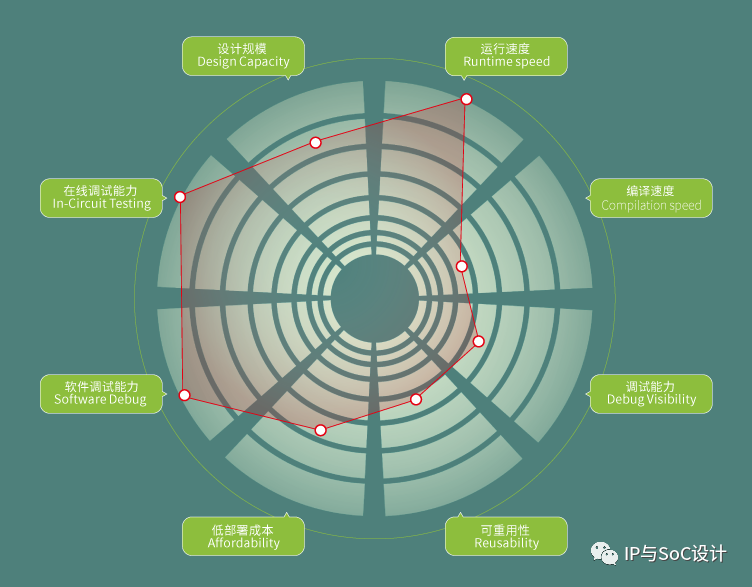

FPGA原型驗證平臺的分類與選擇

FPGA原型驗證平臺基本可以分為兩大類,自研的原型驗證平臺和商業的原型驗證平臺。而這種選擇則基于自身項目決定。

自研的原型驗證平臺

一些公司會選擇使用自研,因為它們內部就有硬件設計部門,所以會直接從Xilinx或者從Intel采購FPGA,自行設計研制的FPGA平臺。由于同屬一個體系,針對新的項目或者新的原型驗證平臺需求,能夠快速進行實現平臺更新或者重新設計,并且可以定制化一些特殊的接口來滿足自己芯片的某些特殊應用。

商業的原型驗證平臺

國微思爾芯-S2C

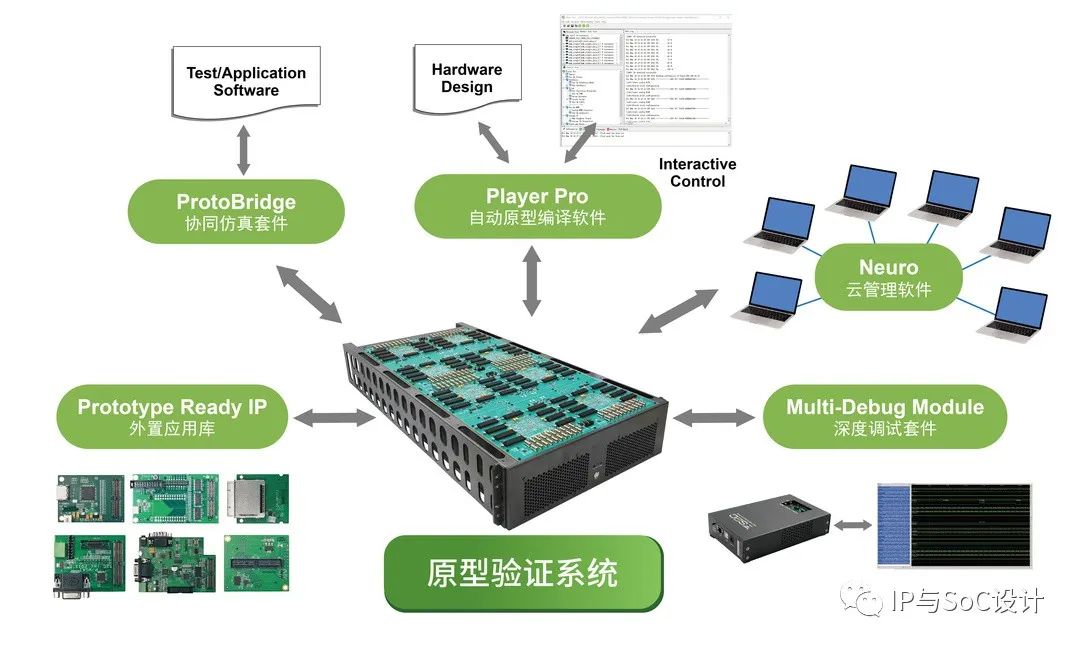

S2C公司是一家國內的 FPGA 快速原型驗證解決方案供應商,他提供豐富種類的FPGA原型驗證硬件平臺。芯神瞳邏輯矩陣 Logic Matrix(LX)是國微思爾芯結合多年的原型驗證產品經驗,與當前高端分割、互聯技術相結合所推出的高密原型驗證平臺。芯神瞳邏輯矩陣 LX 每個平臺均配備了8顆 FPGA,LX1 選用的是賽靈思 (Xilinx) 的 Virtex UltraScale VU440,LX2 選用的是Virtex UltraScale+ VU19P,并且都能搭配使用芯神瞳自動原型編譯軟件、深度調試套件、協同仿真套件、以及外置應用庫來快速搭建原型驗證環境。除了硬件平臺,S2C還提供了Prodigy系列軟件。其中Player Pro能提供基于網表(EDIF)的自動分割功能。

·高性能高密多核硬件

·自動設計分割

·深度調試系統

·豐富的接口庫

Synopsys公司的HAPS系列

HAPS是Synopsys公司推出的FPGA原型驗證平臺,該平臺自2003年第一代HAPS-10起,到目前已經發展到HAPS-100。HAPS原型驗證平臺是一個集成解決方案,包含了硬件部分和軟件部分。被廣泛應用的HAPS80系列,發布于2014年,最大規模的硬件平臺HAPS80-S104,內含4顆Xilinx的VU440 FPGA,及支持多用戶模式和多臺級聯(最高可達64臺)模式來滿足不同設計的需求。集成軟件除了提供編譯,綜合等功能,最大的亮點是支持多FPGA和多臺HAPS的Auto Partition(自動分割),同時擁有強大的調試能力,比如DTD(深度跟蹤調試)和GSV(全局信號可見)功能。

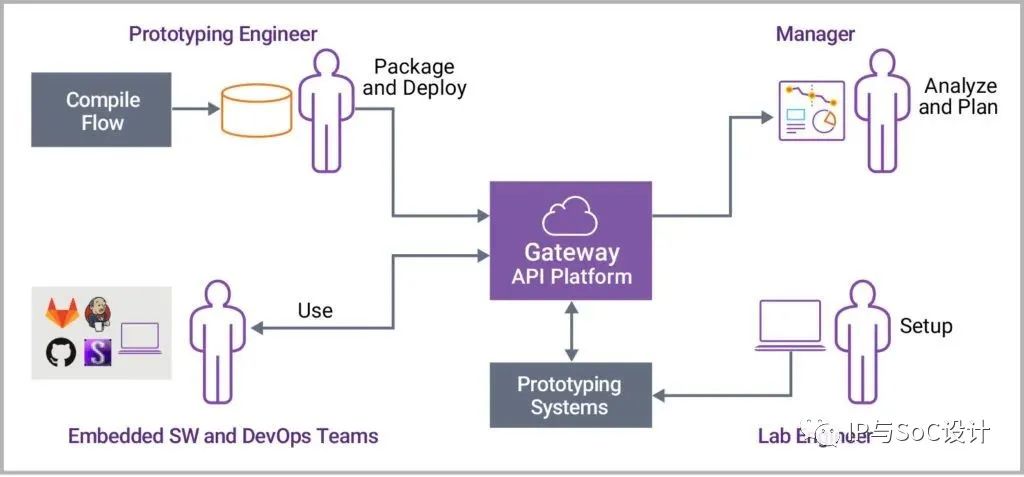

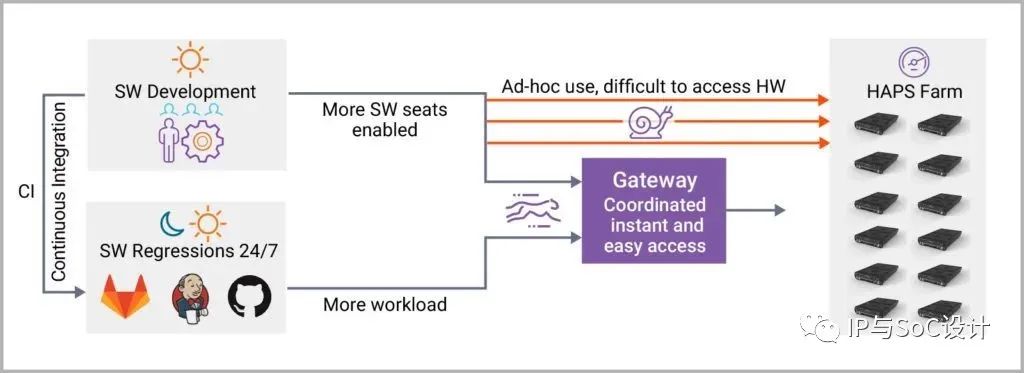

新思的云原生Web

Cadence公司的Protium系列

Cadence公司在FPGA原型驗證平臺上起步比較晚,2017年嘗試推出了第一代FPGA原型驗證平臺Protium S1,于2019年發布了改進的第二代Protium X1。Protium X1 硬件采用Blade/Rack結構,一個Blade/Rack包含了6顆Xilinx VU440 FPGA,集成軟件除了支持編譯,綜合以外,也支持跨FPGA的Auto Partition(自動分割),同時支持DCC(Data Capture Card)調試等。2021年,發布了Protium X2系統。新一代系統基于下一代硬件仿真核心處理器和 Xilinx UltraScale+ VU19P FPGA,將為客戶帶來2倍容量提升和1.5倍性能提升,以更少的時間為大規模芯片驗證完成更多次數的迭代。

除此之外,國內還有一些優秀的公司提供FPGA原型驗證工具,例如亞科鴻禹和芯啟源。

亞科鴻禹

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論