基于FPGA實現(xiàn)各種設計的首要前提是理解并掌握數字的表示方法,計算機中的數字表示方法有兩種:定點數表示法和浮點數表示方法。

2022-10-10 10:30:16 1120

1120 最近需要在6618上做速度優(yōu)化,準備采用定點代替浮點的方式,但是沒有找到針對66X系列的虛擬定點數學庫。采用C64+系列的定點虛擬庫代替,發(fā)現(xiàn)32bit數據的乘法速度竟然比直接進行浮點運算的速度還要

2018-06-21 11:23:09

了 100 GFLOPS。在所有信號處理算法中,對于只需要動態(tài)范圍浮點算法的很多高性能 DSP應用,這是非常重要的優(yōu)點。選擇 FPGA并結合浮點工具和 IP,設計人員能夠靈活的處理定點數據寬度、浮點數據精度和達到的性能等級,而這是處理器體系結構所無法實現(xiàn)的。

2019-08-13 06:42:48

定點dsp能不能處理浮點數,如果不能為什么通過硬件仿真可以用printf輸出正確的浮點數據?//g_lpTemp,g_lpOrient分別指向存儲圖像數據的兩個數組問題是下面的函數在VC6.0++

2013-10-03 13:13:47

定點數和浮點數的區(qū)別目的:理解定點數和浮點數在傅里葉變換(FFT)的實際應用中的選擇單片機中如果需要進行一定的運算(常見的傅里葉變換)時,需要在不同情況下對AD采集的數據進行一定的處理才能得到正確

2022-02-21 07:22:23

第17章 DSP功能函數-定點數互轉本期教程主要講解功能函數中的Q7,Q15和Q31分別向其它類型數據轉換。目錄第17章 DSP功能函數-定點數互轉17.1 初學者重要提示17.2 DSP基礎運算指令17.3 ...

2021-08-11 08:04:44

本帖最后由 mr.pengyongche 于 2013-4-30 03:11 編輯

一數的定標 在定點DSP芯片中,采用定點數進行數值運算,其操作數一般采用整型數來表示。一個整型數的最大表示

2012-01-31 11:50:28

使用LabVIEW FPGA模塊中的CORDIC IP核,配置arctan(X/Y)算法,配置完成之后,IP核只有一個輸入。我參考網上VHDL CORDIC IP核,說是將XY合并了,高位X低位Y。不知道在LabVIEW中如何將兩個值X、Y合并成一個(X、Y均為定點數)。具體情況如下圖:

2019-09-10 20:07:07

全書從計算、轉換和處理的角度,系統(tǒng)介紹二進制定點數和十進制定點數、浮點數,算術運算常用函數計算,代碼轉換,表格處理,數字濾波等程序,具有很強的實用性

2016-04-15 01:01:40

定點數字信號處理器,軍用SM320C6415-EP增強型產品定點數字信號處理器SM320C6424-EP增強型產品定點數字信號處理器SM320C6472-HIREL定點數字信號處理

2019-11-26 13:13:02

verilog程序中需要用到定點數,用浮點數太復雜。。。有誰有關于定點數比較系統(tǒng)的資料嗎。。。我找到黑金的教程,是關于浮點數運算的verilog實現(xiàn),很詳細,先傳上來 Verilog 最后的私私細語 第一章 不同世界的自然.pdf (3.45 MB )

2019-03-27 06:35:16

處理研究的內容2.2 數字信號處理系統(tǒng)架構分析2.3 基于FPGA的數字信號處理的相關問題2.3.1 基于FPGA的數字信號處理系統(tǒng)設計流程2.3.2 定點數與浮點數參考文獻第3章 數字信號處理中

2012-04-24 09:33:23

第13章SupportFunctions的使用(一) 本期教程主要講解支持函數中的數據拷貝,數據賦值和浮點數轉換為定點數。 13.1 數據拷貝Copy 13.2 數據填充Fill 13.3 浮點數轉定點數 Float to Fix 13.4 總結

2015-06-11 15:12:53

第14章SupportFunctions的使用(二) 本期教程主要講解支持函數中的Q7,Q15和Q31分別向其它類型數據轉換。 14.1 定點數Q7轉換 14.2 定點數Q15轉換 14.3 定點數Q31轉換 14.4 總結

2015-06-12 11:27:45

第7章DSP定點數和浮點數(重要) 本期教程主要跟大家講解一下定點數和浮點數的基礎知識,了解這些基礎知識對于后面學習ARM官方的DSP庫大有裨益。特別是初學的一定要理解這些基礎知識。 7.1 定點數和浮點數概念 7.2 IEEE浮點數 7.3 定點數運算 7.4 總結

2015-06-03 11:47:44

的數轉換為二進制數3.2 二進制的數轉換為十進制數4 定點數和浮點數的概念4.1 定點數4.1.1 定點數存儲格式(Q格式)4.1.2 定點數與浮點數之間的轉換4.1.2.1 浮點數到定點數

2021-12-15 07:00:05

本帖最后由 eehome 于 2013-1-5 10:07 編輯

fpga中定點乘法器設計(中文)

2012-08-24 00:55:37

第16章 DSP功能函數-數據拷貝,數據填充和浮點轉定點本期教程主要講解功能函數中的數據拷貝,數據填充和浮點數轉換為定點數。目錄第16章 DSP功能函數-數據拷貝,數據填充和浮點轉定點16.1 初學者重要提示16....

2021-08-17 07:41:07

第16章 DSP功能函數-數據拷貝,數據填充和浮點轉定點本期教程主要講解功能函數中的數據拷貝,數據填充和浮點數轉換為定點數。目錄第16章 DSP功能函數-數據拷貝,數據填充和浮點轉定點16.1 初學者重要提示16....

2021-08-17 07:37:26

馮·諾依曼機工作方式的基本特點是什么?計算機系統(tǒng)中采用補碼運算的目的是什么?在定點二進制運算器中,減法運算一般通過什么來實現(xiàn)?在定點數運算中產生溢出的原因是什么?和外存儲器相比,內存儲器的特點是什么?

2021-08-11 08:44:26

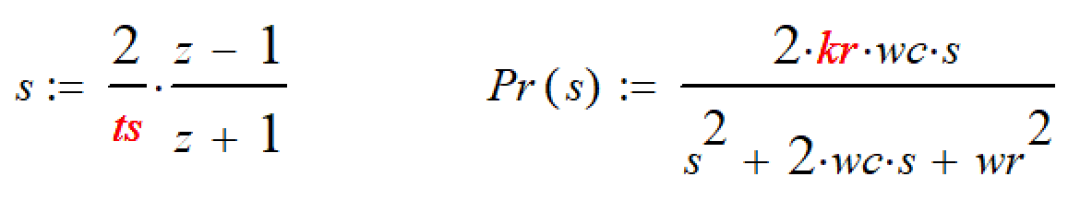

了浮 定點 控制器的硬件實現(xiàn),提出了溢出 飽和等問題的解決方法,單次運算時間分別達 ,并對兩種控制器的性能進行了分析和比較 設計了單精度浮點數和 位定點數之間的轉換控制器,增強了浮點 的普適性設計了

2012-08-11 15:58:43

擴充浮點運算集的時候,是否需要自己在FPGA板子上設置一個定點數轉為浮點數的部分?

2023-08-11 09:13:34

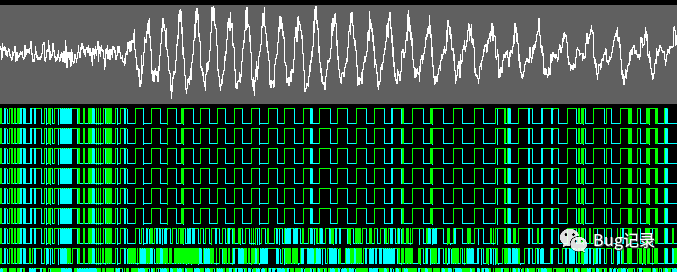

工具◆u3000XilinxAtlys板卡和ISIM仿真支持◆u3000有符號定點數和浮點數IEEE庫示例◆u3000概述并行全通IIR濾波器設計◆u3000CA和PCA系統(tǒng)級設計◆u3000MP3和ADPCM的語音和音頻編碼

2023-09-19 06:38:28

,數據轉換和校準的過程是由模塊完成的,校準的結果是一個范圍在-16~16之間的定點數?問題:1、在程序中這個模擬量輸入值時是不是直接使用就可以了?比如我外部實際輸入電壓值為5V,則程序中處理完的定點數

2018-08-10 10:48:31

程序如下: 你的學號,以最后兩位所組成的數為被除數,設為定點數A;以最左兩委組成的書為除數,設為定點數B,編寫一段程序完成該定點除法,及A/B,要求把得到的商存放在R1中。謝謝!!!!

2015-11-15 13:17:08

本帖最后由 gk320830 于 2015-3-5 23:17 編輯

數制,浮點數與定點數的文檔,上數電時老師給的。有興趣的同學可以來看看

2013-03-27 21:31:15

轉dsp系列教程本期教程主要講解支持函數中的數據拷貝,數據賦值和浮點數轉換為定點數。13.1 數據拷貝 Copy13.2 數據填充 Fill13.3 浮點數轉定點數 Float to Fix13.4

2016-09-24 09:37:07

轉dsp系列教程本期教程主要講解支持函數中的Q7,Q15和Q31分別向其它類型數據轉換。 14.1 定點數Q7轉換 14.2 定點數Q15轉換 14.3 定點數Q31轉換 14.4 總結14.1

2016-09-24 09:44:08

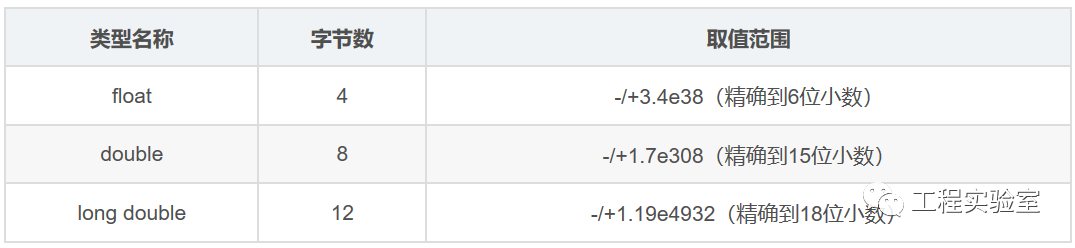

。7.1.2 浮點數 在計算機系統(tǒng)的發(fā)展過程中,曾經提出過多種方法表達實數。典型的比如相對于浮點數的定點數(Fixed Point Number)。在這種表達方式中,小數點固定的位于實數所有數字中間

2016-09-22 13:02:21

本帖最后由 一只耳朵怪 于 2018-6-14 11:52 編輯

28335為浮點DSP ,現(xiàn)在假如我采用兩種方法:1.浮點數使用IQmath轉換后當定點數計算2.直接用浮點數進行計算這兩種

2018-06-14 05:59:15

定點數具有哪幾種表示的形式?FPGA是如何實現(xiàn)數字信號處理定點運算的?

2021-06-18 09:19:18

處理器相關的兩個問題,望哪位大神不吝指教下:1.是不是不帶FPU的處理器都是定點處理器啊? 比如定點數值信號處理器 C55XX系列的,比如51單片機,再比如RAM常用的Cortex-M3內核處理器!2.對于定點處理器上面大神分享的經驗是不是都通用的,還是根據編譯器而定的?

2019-05-13 01:09:48

得到的ADC數據需要進行定點數到浮點數的轉換,為了節(jié)省開銷,想使用匯編程序進行定點和浮點之間的轉換。請問ADSP-21469的匯編指令集ISA/VISA中有沒有專門用來進行浮點數和定點數轉換的指令?

2018-07-24 07:21:18

得到的ADC數據需要進行定點數到浮點數的轉換,為了節(jié)省開銷,想使用匯編程序進行定點和浮點之間的轉換。請問ADSP-21469的匯編指令集ISA/VISA中有沒有專門用來進行浮點數和定點數轉換的指令?

2023-11-29 08:03:15

您好! 1.DSP從FPGA接收到定點的數據,怎么樣轉換為浮點數,2.TI對于6748有沒有關于維特比譯碼的函數庫

2018-07-31 06:48:56

介紹了G.729語音編碼器算法和定點數字信號處理芯片TMS320VC549,重點討論了低速率語音編碼器在TMS320VC549上實時實現(xiàn)過程中軟、硬件設計中的關鍵技術。采用了定點數字信號處理器

2009-02-19 23:37:13 26

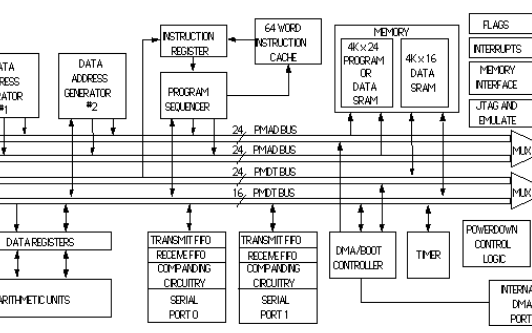

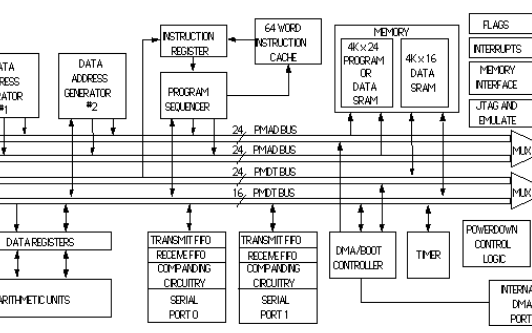

26 ADSP2195是美國AD公司推出的新型定點數字信號處理器.該器件在繼承了AD公司原有DSP芯片優(yōu)點的基礎上,進一步提高了運行速度.文中對ADSP2195的特點參數、內部結構及片內資源做了詳細介

2009-04-28 15:43:07 12

12 在借鑒現(xiàn)有的快速傅里葉變換頻譜校正算法的基礎上,提出了改進的雙窗法,并根據應用系統(tǒng)的特點,給出了改進的定點數字信號處理擴展精度快速傅里葉變換算法。從理論上分

2009-05-20 19:57:00 37

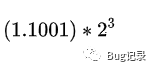

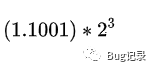

37 在定點DSP芯片中,采用定點數進行數值運算,其操作數一般采用整型數來表示。一個整型數的最大表示范圍取決于DSP芯片所給定的字長,一般為16位或24位。顯然,字長越長,所能表

2009-07-04 16:57:47 24

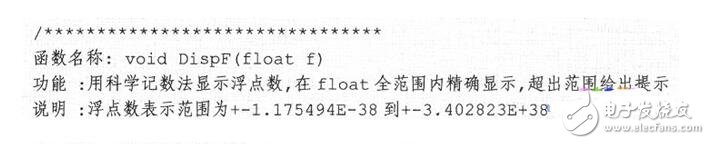

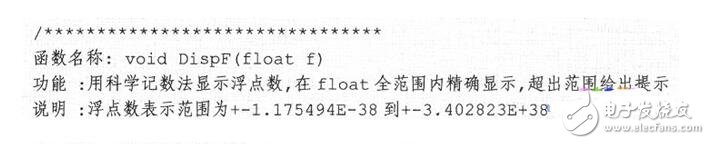

24 單片機能夠直接處理的數是定點數,然而實際上需要輸入、處理和顯示的數據卻是浮點數,本文詳細介紹了浮點數在單片機系統(tǒng)中的實現(xiàn)。關鍵詞:浮點數單片機數據處理Ab

2009-08-13 15:38:22 44

44 基于定點DSP的實時噪聲消除系統(tǒng):介紹了一個基于16 位定點數字信號處理芯片ADSP-2187L 的實時音頻噪聲消除器,采用89C51作為控制單元協(xié)調輸入,輸出接口電路和DSP 處理電路的工作。

2009-09-08 09:13:08 19

19 DSP芯片的定點運算3.1 數 的 定 標在定點DSP芯片中,采用定點數進行數值運算,其操作數一般采用整型數來表示。一個整型數的最大表示范圍取決于DSP芯片所給定的字長,一般

2010-04-06 14:07:12 33

33 定點數字信號處理器(DSP)技術與應用

數字信號處理器(DSP)的應用領域•通用數字信號處理(數字濾波、卷積、相關、變換等)•通信(高效調制/解調、編/解碼

2010-04-07 10:30:36 23

23 提出了一種用于嵌入式系統(tǒng)的定點解碼算法。該算法的核心是用定點數和定點計算代替浮點算法, 并對解碼的各個過程進行優(yōu)化設計。該算法在以處理器為核心的嵌入式系統(tǒng)上完

2010-10-26 16:24:50 30

30 功能:雙字節(jié)十六進制定點數轉換成格式化浮點數

入口條件:雙字節(jié)定點數的絕對值在[R0]中,數符在位1FH中,整數部分的位數在A中。

2009-01-19 22:45:28 2900

2900 、5G 無線以及汽車等領域,客戶必須滿足高級駕駛員輔助 (ADAS)、雷達和深度學習等應用中嚴峻的散熱、功耗和成本要求。 要實現(xiàn)這些目標,一種極為有效的方法是用定點數實現(xiàn)信號處理鏈。

2018-06-30 11:37:00 667

667

采用 這樣的一種規(guī)范來表示定點數。其中s表示符號位,m表示字長,n表示整數字長。LabVIEW中定點數存儲空間,最大限定為64bit。 圖:有符號定點數表示方法 比如一個字長為8,整數字長為4的無符號定點數。

2017-11-16 13:04:20 7757

7757

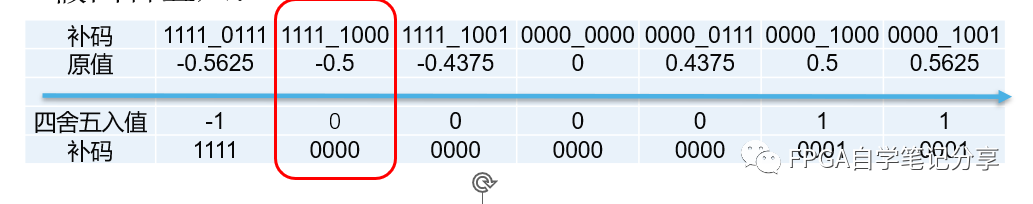

浮點數與定點數表示法是我們在計算機中常用的表示方法 所以必須要弄懂原理,特別是在FPGA里面,由于FPGA不能像在MCU一樣直接用乘除法。 首先說一下簡單的定點數,定點數是克服整數表示法不能表示實數

2017-11-18 02:15:40 8422

8422

定點小數運算 有些FPGA中是不能直接對浮點數進行操作的,只能采用定點數進行數值運算。 所謂定點小數就是把小數點的位置固定,我們要用整數來表示小數。 先以10進制為例。如果我們能夠計算12+34=46的話,當然也就能夠計算1.2+3.4 或者 0.12+0.34了。

2018-06-28 15:49:00 6261

6261 單片機執(zhí)行程序的過程,實際上就是執(zhí)行我們所編制程序的過程。即逐條指令的過程。本文詳細介紹了浮點數在單片機中的表示方式和匯編子程序,浮點數比定點數加減法要困難,但是克服了定點數表示范圍小的問題,總之定點數和浮點數各有各得的特點,讀者可以在實際運用中加以優(yōu)化運用。

2018-03-07 15:19:11 9446

9446

在定點DSP芯片中,采用定點數進行數值運算,其操作數一般采用整型數來表示。

2018-04-04 14:51:00 5

5 定點數學庫(qmath)包含數學/三角例程,開發(fā)一個易于使用的庫,這是關系到用戶的抯應用。

2018-04-12 09:44:12 2

2 本文的主要內容介紹的是TI的產品TMS320VC5510 和5510A的定點數字信號處理器詳細介紹概述

2018-04-25 17:04:50 5

5 TMS320VC5509A定點數字信號處理器(DSP)是基于TMS320VC5X DSP處理器的CPU核。C55X微處理器的DSP架構通過提高并行性和減少功耗的總關注來實現(xiàn)高性能和低功耗。CPU支持

2018-04-25 17:17:44 0

0 TMS3VC5506定點數字信號處理器(DSP)是基于TMS3C35X DSP的CPU處理器核心。C55 x DSP架構實現(xiàn)了高性能和低功耗。增加的并行性和總的精力集中在減少功耗。CPU支持內部總線

2018-04-26 09:39:05 7

7 本文的主要內容是對TMS320VC5505定點數字信號處理器資料的英文詳細介紹

2018-04-26 09:52:21 1

1 本文的主要內容介紹的是TI的產品TMS320VC5504定點數字信號處理器的資料英文詳細概述

2018-04-26 10:49:47 1

1 本文的主要內容介紹的是TI的產品TMS320VC5501定點數字信號處理器的詳細英文原版資料介紹

2018-04-26 14:15:48 0

0 TMS320VC5402A定點數字信號處理器(DSP)(以下簡稱設備)除非另有說明,它基于一個具有一個程序的高級修改哈佛體系結構。存儲器總線和三個數據存儲器總線。該處理器提供算術邏輯單元(ALU

2018-04-26 16:19:38 0

0 本文的主要內容介紹了TMS320VC5401定點數字信號處理器的英文原版資料

本節(jié)描述了TMS320VC5401的主要特點,列出了引腳分配,并描述了每個引腳的功能。該數據手冊還提供了關于可用包裝

2018-04-26 16:38:21 0

0 TMS32 VC54 9定點數字信號處理器(DSP)(以下簡稱為549)是基于一種先進的改進的哈佛體系結構,它具有一個程序存儲器總線和三個數據存儲器總線,該處理器還提供了一個高度邏輯的算術邏輯單元

2018-04-26 16:43:46 3

3 TMS320LC549定點數字信號處理器(DSP)(以下簡稱為“549”)是基于一種先進的改進哈佛體系結構,具有一個程序存儲器總線和三個數據存儲器總線。處理器還提供具有高度并行性的算術邏輯單元(ALU),特定于應用的硬件邏輯、處理器存儲器和附加的處理器外圍設備。

2018-04-26 17:09:26 5

5 本文檔主要的內容介紹的是TI的產品TMS320LC548定點數字信號處理器(DSP)的詳細資料介紹

2018-04-26 17:13:15 4

4 本文檔介紹的內容是TMS320C54x,LC54x,VC54x 定點數字信號處理器(DSP)的詳細介紹和對比

2018-04-27 09:38:53 7

7 SMJ320LC549定點數字信號處理器(DSP)(以下稱為549)是基于先進的改進哈佛體系結構,具有一個程序存儲器總線和三個數據存儲器總線。處理器還提供算術邏輯單元(ALU),其具有高度并行性

2018-04-28 09:37:49 6

6 SM320VC5416 定點數字信號處理器(DSP)(以下簡稱為5416),是基于一種先進的改進的哈佛架構,它具有一個程序存儲器總線和三個數據存儲器總線。該處理器提供算術邏輯單元(ALU),具有

2018-04-28 09:48:52 10

10 本文檔的主要內容介紹的是TI的產品SM320VC5409EP定點數字信號處理器的詳細資料概述

2018-04-28 09:53:30 9

9 本文的主要內容介紹的是TI的產品SM320VC5510AEP定點數字信號處理器的詳細英文資料概述

2018-05-03 10:16:21 1

1 該設備是TI公司的TMS320C5000型定點數字信號處理器(DSP)產品系列的成員,是為低功耗應用而設計的。

2018-05-08 10:31:28 0

0 該設備是TI公司的TMS320C5000型定點數字信號處理器(DSP)產品系列的成員,是為低功耗應用而設計的。

2018-05-08 10:48:17 2

2 TMS320VC5420定點數字信號處理器(DSP)是一種可長達200 MIPS的雙CPU設備。性能。5420個由兩個獨立的54個子系統(tǒng)組成,這些子系統(tǒng)能夠進行核心到核心通信。

2018-05-08 11:24:56 16

16 轉化為的浮點數可以是單精度也可以是雙精度。

2018-07-05 08:09:00 3703

3703

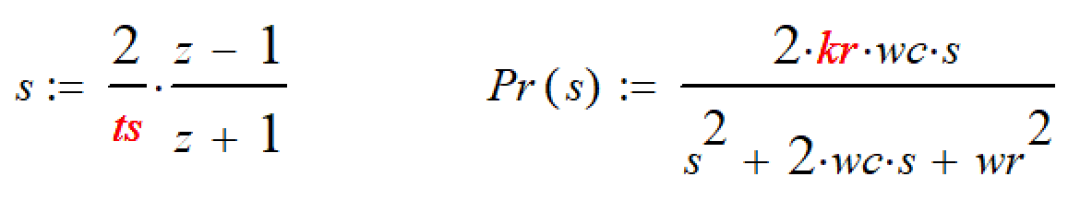

控制器的硬件實現(xiàn),提出了溢出、飽和等問題的解決方法,單次運算時間分別達480 ns、120 ns,并對兩種控制器的性能進行了分析和比較。設計了單精度浮點數和16 位定點數之間的轉換控制器,增強了浮點PID 的普適性。設計了基于FPGA 的全數字逆變焊接電源的實驗平

2019-03-05 09:43:46 22

22 ADSP-21csp01是新推出的ADI系列16位定點數字信號處理器的第一個成員,專為快速有效地處理多個信號而設計,并有效地處理以高速寫入的編譯代碼等級語言。

2019-04-15 14:58:18 1673

1673

TMS320VC5402定點數字信號處理器(DSP)(以下簡稱5402,除非另有說明)基于一種改進的高級哈佛架構,該架構具有一個程序存儲器總線和三個數據存儲器總線。該處理器提供具有高度并行性的算術

2020-01-13 08:00:00 4

4 不會比浮點差多少,但速度會快太多。因此浮點運算自然需要轉換為定點運算!如何轉換?確實包含很多原則和技巧!本文內容會特別的多,請大家耐心看完! 如何將定點數轉換為浮點數?通過量化!量化過程有技巧嗎?當然,后續(xù)慢慢講。此時第

2021-06-29 14:19:22 2916

2916 定點數和浮點數的區(qū)別目的:理解定點數和浮點數在傅里葉變換(FFT)的實際應用中的選擇單片機中如果需要進行一定的運算(常見的傅里葉變換)時,需要在不同情況下對AD采集的數據進行一定的處理才能得到正確

2021-12-24 19:22:13 16

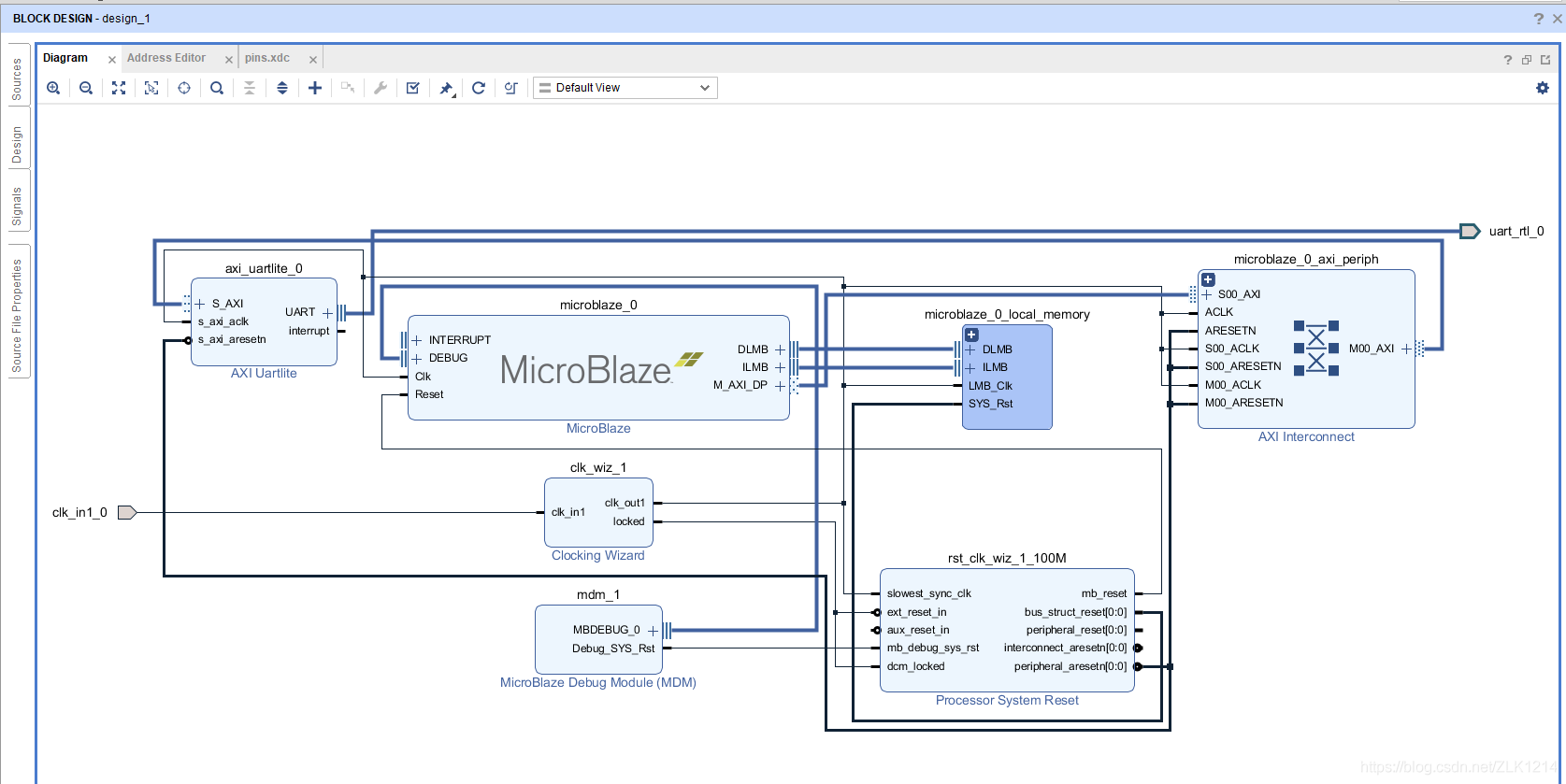

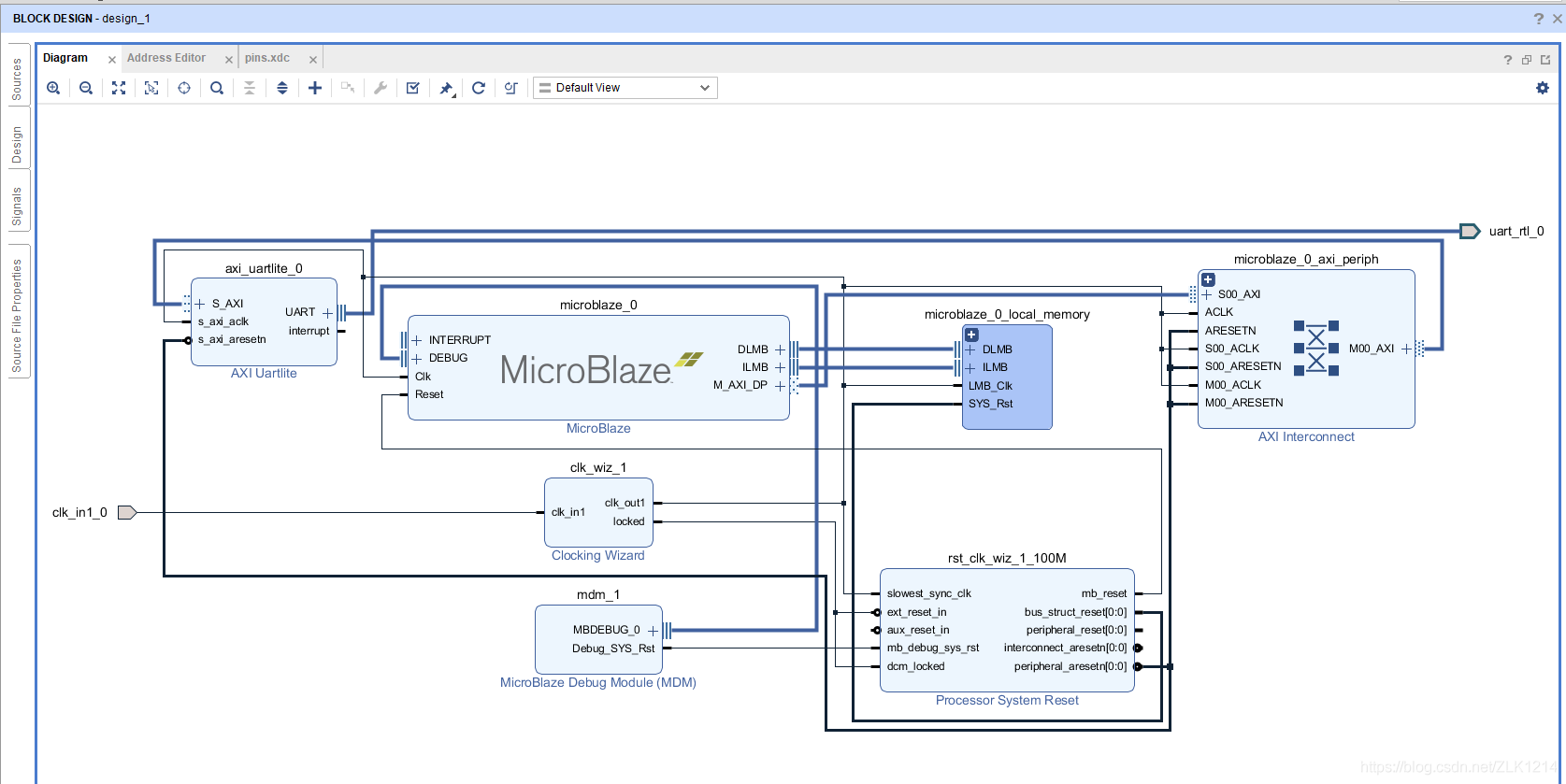

16 本文以浮點數Floating-point IP核將定點數轉換為浮點數為例,詳細講解AXI DMA IP核的使用方法。

2022-02-16 16:21:37 7547

7547

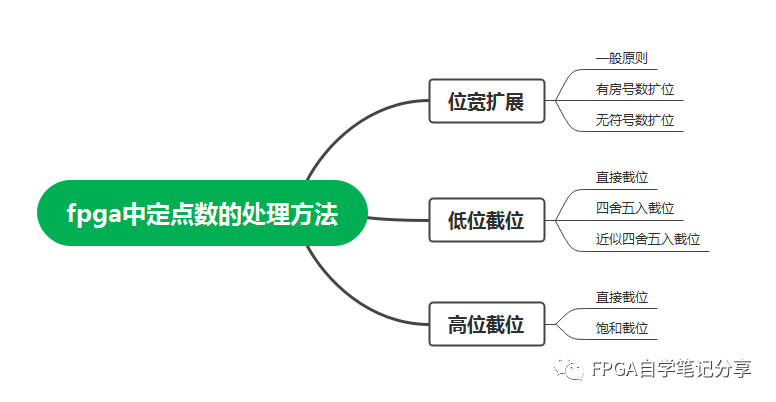

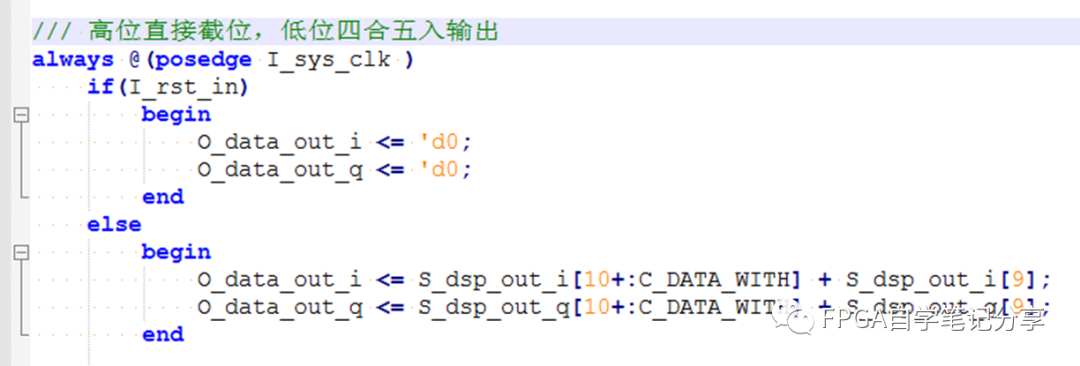

FPGA在常規(guī)運算時不能進行浮點運算,只能進行定點整型運算,在處理數據的小數乘加運算和除法運算時FPGA一般是無能為力的,其中一種常用的處理方法就是數據進行浮點到定點的轉換。

2022-10-13 16:23:50 3752

3752 計算機體系結構中浮點和定點數據的表示 1、定點數: 定點數指小數點在數中的位置是固定不變的,通常有定點整數和定點小數或者說是定點分數。在對小數點位置作出選擇之后即定標定了Q值后,運算中的所有數均應

2022-12-06 10:00:01 2602

2602 通常情況下單精度浮點在小數點后的精度為1/(2^23),理論上使用32位定點IQ24就可以覆蓋單精度浮點的精度問題,但是在16bit上,使用i1.q15的方法來算,僅有1/(2^15)的精度,如果直接使用則會遇到量化精度引起的誤差問題。

2023-02-08 15:11:18 583

583

圖像處理的算法中,大部分需要采用 浮點數 運算,而浮點數運算再FPGA中是非常不劃算的,因此需要轉換成定點數計算,此時會設計到浮點運算轉定點運算時精度下降的問題。 3.軟件和硬件的合理劃分 這里的軟件是指DSP,CPU,硬件是指FPGA;一般?結構規(guī)則

2023-02-15 16:35:08 896

896 圖像處理的算法中,大部分需要采用浮點數運算,而浮點數運算再FPGA中是非常不劃算的,因此需要轉換成定點數計算,此時會設計到浮點運算轉定點運算時精度下降的問題。

2023-02-17 09:16:15 1449

1449 處理的算法中,大部分需要采用浮點數運算,而浮點數運算再FPGA中是非常不劃算的,因此需要轉換成定點數計算,此時會設計到浮點運算轉定點運算時精度下降的問題。 3.軟件和硬件的合理劃分這里的軟件是指DSP,CPU,硬件是指FPGA;一般 結構規(guī)則

2023-03-21 19:40:02 377

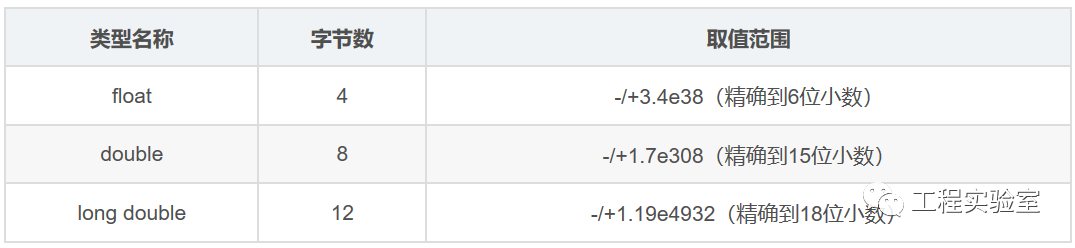

377 定點數硬件實現(xiàn)簡單,但表示的范圍有限,且部分的小數運算IP核只支持浮點數運算,因此這里還需要提到浮點數的相關內容。

2023-06-16 15:41:53 872

872

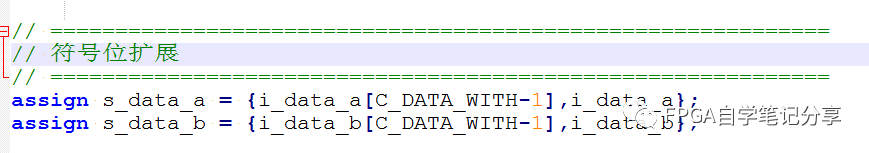

FPGA內部表示正負數,小數的規(guī)則。兩者相比之下,定點數實現(xiàn)簡單,表達更為直觀,所以在很多時候FPGA通常使用定點數表示小數。

2023-06-19 10:44:52 642

642

定點數,小數點位置固定不變,參與運算的數據其小數點固定的位于所有數字中間的某個位置,比如貨幣的表達,規(guī)定了使用2位整數位+2位小數表示的模式,具體數據如99.00、10.55、68.66等。定點數

2023-08-22 16:06:59 2170

2170

電子發(fā)燒友App

電子發(fā)燒友App

評論