綜合

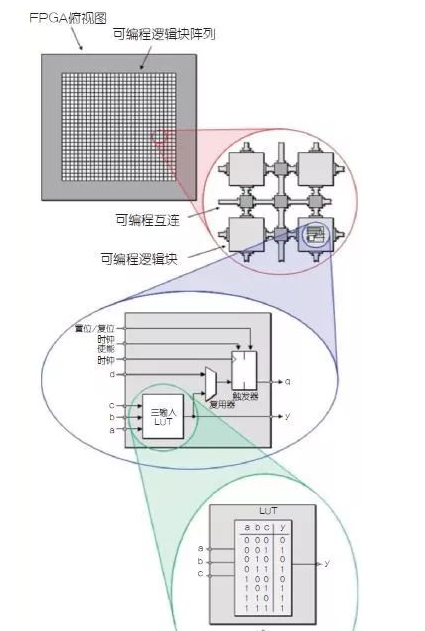

構建FPGA的第一階段稱為綜合。此過程將功能性RTL設計轉換為門級宏的陣列。這具有創建實現RTL設計的平面分層電路圖的效果。

在這種情況下,宏實際上是內部FPGA單元的模型。這可以是FPGA中的任何數字元素,例如觸發器,RAM或查找表(LUT)。

綜合工具

我們可以使用許多不同的工具來運行綜合過程。

兩個主要的FPGA供應商(Xilinix 和 Intel)都提供適用于大多數項目的免費綜合工具。

除此之外,還有許多 我們可以使用的開源綜合工具。這些工具中最流行的是 yosys ,它經常與 Lattice FPGA一起使用。

也有用于此目的的付費工具。這些工具中最著名的是Synopsys的Synplify Pro 和Mentor Graphics的Leonardo Spectrum。

與免費工具相比,付費工具通常能夠提供更多優化的網表。通常,對于大型或高速設計,我們只需要付費工具即可。

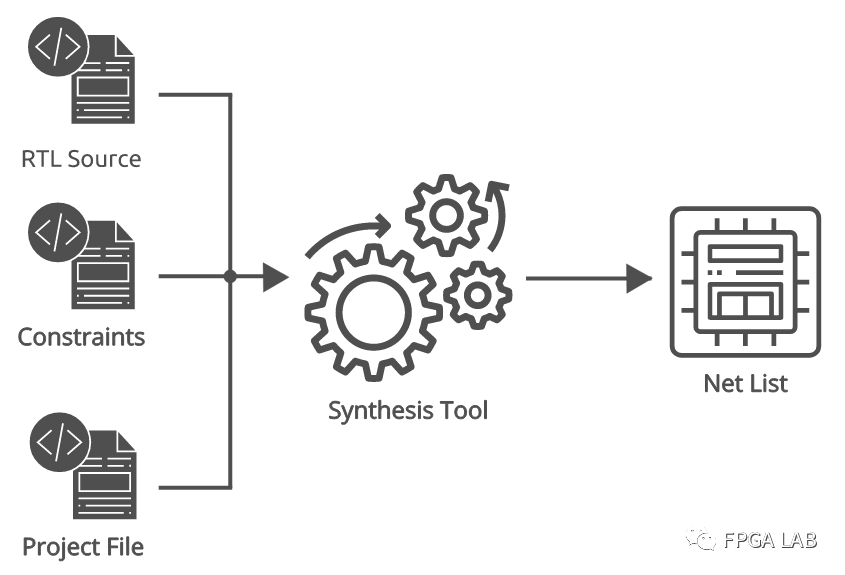

綜合過程至少需要兩個輸入。

其中第一個是我們設計的源代碼。

我們還需要一個腳本或項目文件,用于定義綜合工具的配置。該腳本通常告訴工具目標為哪個FPGA,設計的引腳以及在運行綜合時使用哪種策略。

除此之外,優良作法是創建一個文件,該文件定義設計的時序約束,我們稱之為約束文件。

綜合

我們使用時序約束來定義有關FPGA的細節,而這些細節無法在源代碼中指定。

這些細節決定了綜合器為優化FPGA內的時序投入了多少精力。

邏輯利用率

作為綜合過程的一部分,我們還可以對設計進行一些分析。但是,在布局和布線過程之后,此信息通常更可靠。

這些分析中的第一個是設計的邏輯利用率。該分析詳細說明了我們設計使用的每種不同類型的FPGA單元有多少個。

設備中的各個單元隨芯片的不同以及供應商之間的不同而不同。

幾乎所有現代芯片都將包括RAM,某種形式的LUT和觸發器。

高端芯片還可以包括專用的DSP內核,時鐘管理模塊(例如PLL)以及其他外圍接口(例如ADC)或專用的高速接口。

完成綜合過程后,我們可以生成報告,以絕對值和器件中所有可用單元的百分比告訴我們設計中使用了多少個單元。

在運行綜合過程之后,經常會發現我們的設計對我們的設備而言太大了。發生這種情況時,我們有很多選擇。

通常可以通過更改綜合工具的配置來降低利用率。這樣的示例可以是更改FSM編碼或選擇其他綜合算法。

如果我們的設計僅比我們選擇的FPGA大一點,那么這種減少就足夠了。

如果這還不能充分降低利用率,那么我們必須選擇一個新的FPGA或提高原始代碼的效率。

時序分析

運行綜合后,我們還可以分析FPGA的時序。

我們使用該分析來確定FPGA是否可以以所需的頻率運行我們的設計。

當我們的設計不能以所需的頻率運行時,我們不能確定內部觸發器將不會有時序違規。因此,我們無法保證我們的設備能夠按預期運行。

我們通常會在布局和布線過程之后詳細分析設計的時序。由于時序取決于FPGA中單元的位置,因此經過此過程,結果將更加準確。

綜合后仿真

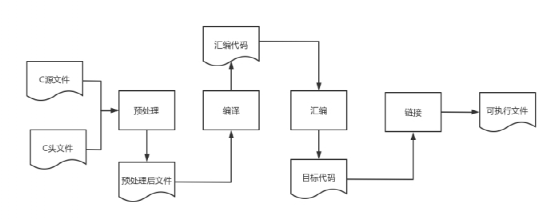

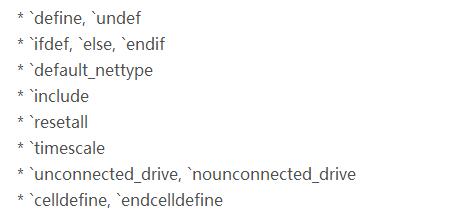

在綜合過程中,我們可以要求該工具以VHDL或verilog生成網表。

此過程還生成一組時序延遲,該時序延遲可對信號通過FPGA的傳播進行建模。

然后,我們可以使用此信息來運行我們的綜合網表的仿真。

由于這些仿真還可以對我們的設計時序進行建模,因此它們可以為最終設備的行為提供更準確的模型。

無論我們在設計中使用哪種語言,我們通常都使用verilog生成綜合后仿真模型。

這樣做的原因是基于Verilog的模型比其VHDL等效模型的仿真速度更快。這對于綜合后仿真尤其重要,因為它們通常執行時間較長。

運行綜合后仿真有兩個主要優點。

- 首先,這些仿真有助于確保我們生成的網表與原始RTL模型的行為相匹配。

- 其次,可以更緊密地考慮芯片的時序。這有助于我們發現可能與基于時序的錯誤(例如時序違規)相關的錯誤。

盡管運行后綜合仿真有很多優點,但是我們通常不會在設計流程中這樣做。

- 原因之一是這些仿真需要很長時間才能運行。綜合后的仿真需要幾天來運行全套測試的情況并不少見。

- 另一個原因是,我們也可以在由我們的布局和布線工具生成的網表上運行仿真。

由于這些網表更能代表最終的芯片方案,因此最好使用該網表進行任何時序仿真。

布局布線(實現)

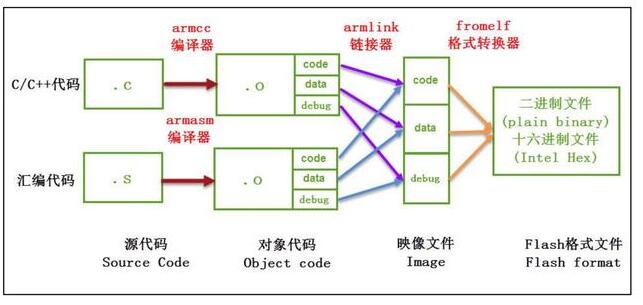

完成綜合后,我們需要將網表映射到FPGA中的實際資源。此過程稱為“布局布線”,實際上包含幾個不同的步驟。

- 通常,此過程的第一階段涉及優化網表。我們使用此過程刪除或替換網表中任何多余或重復的元素。

- 然后,將優化后的網表映射到FPGA中的物理單元,這通常稱為布局。

- 完成布局過程后,然后運行稱為布線的過程。

我們使用構建過程的這一部分來定義所選FPGA中不同單元之間的互連。

為了滿足設計的時序要求,我們通常會執行此過程的幾次運行。但是,布局布線工具負責根據我們的配置安排這些多次運行。

當我們難以使設計滿足時序要求時,通常會增加允許工具執行的運行次數和類型。

布局布線工具

對于Xilinx或Intel部件,沒有第三方布局和布線工具,這意味著我們必須使用供應商特定的工具。這些版本可以免費下載,盡管也提供付費版本。

這些工具也有付費版本可用,盡管通常只有針對高端FPGA的設計才需要它們。

對于萊迪思的FPGA,開源的nextpnr軟件是一種流行的布局布線工具。

根據我們設計的大小,布局和布線過程可能需要幾個小時才能完成。

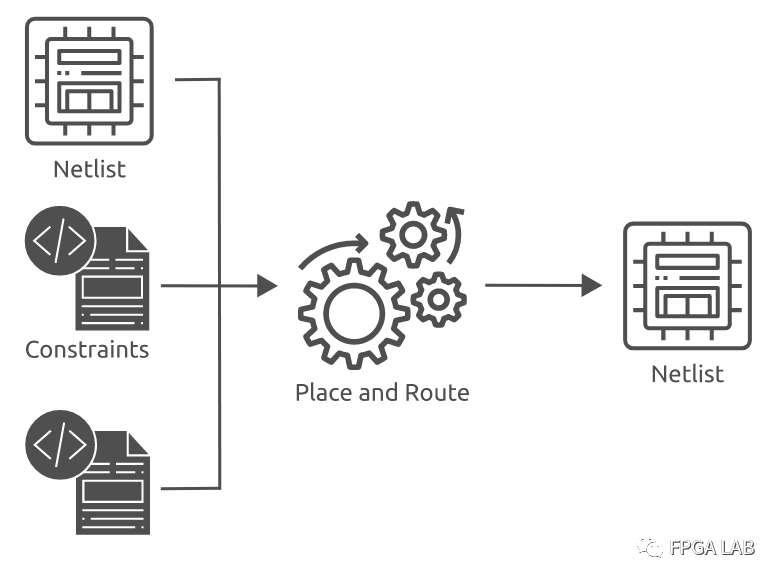

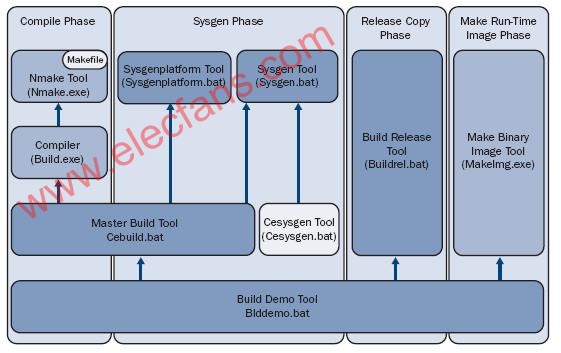

與綜合過程一樣,布局布線工具需要大量輸入才能正確運行。

我們使用綜合工具生成的網表是最重要的輸入。該網表通常是.edf文件,盡管這在工具之間有所不同。

通常,我們還使用項目文件或腳本來確定布局和布線工具的配置。

我們使用它來定義重要信息,例如FPGA零件號和封裝。除此之外,我們使用此腳本定義布局和路線工具的配置。

我們還需要向工具提供一個約束文件,以定義我們設計的時序特征。該文件通常與我們在綜合過程中使用的文件相同,該文件定義了有關時鐘頻率和域的信息。

我們還使用約束文件來定義我們的設計的物理特性,而這些特性在HDL代碼中無法描述。至少,這將包括輸入和輸出到設備物理引腳的映射。

流程圖顯示了綜合網表,約束和項目文件作為布局和布線工具的輸入,網表作為輸出。

布局布線

時序與利用率

與綜合過程一樣,在布局和路線完成之后,我們可以生成許多報告。這使我們可以進一步分析設計以確保其正常工作。

我們通常會在完成布局和布線過程后運行實用程序報告。

該報告詳細介紹了我們用于通過FPGA實現設計的不同單元的數量。

該報告與我們在綜合過程中可以生成的報告完全相同。但是,當我們在完成布局布線過程后生成此報告時,該報告會更準確。

我們通常在完成布局和布線過程后執行的另一項分析是靜態時序分析(STA)。

我們使用此過程來計算設計中所有邏輯鏈的延遲時間。通過計算此信息,布局布線工具可以確定芯片是否能夠以指定的時鐘頻率運行。

布局布線工具會在最壞情況和最佳情況下的定時條件下執行此分析。但是,最常見的情況是在硅中出現最壞情況下的延遲會導致時序問題。

我們通常將STA報告用作設計驗證的關鍵部分。

如果我們的設計使STA失敗,那么我們將無法保證FPGA能夠可靠地工作。發生這種情況時,我們要么必須使用不同的設置再次運行實施過程,要么必須更改設計。

編程文件生成

FPGA設計實現的最后階段是生成編程文件。

通常,我們使用布局和布線工具來生成我們的編程文件。

但是,我們通常將其作為單獨的過程運行。

僅當布局和布線過程生成其輸出后,才能運行此過程。我們只需要告訴工具生成該輸出所需的文件類型即可。

完成此過程后,我們可以使用生成的文件對FPGA進行編程。

電子發燒友App

電子發燒友App

評論