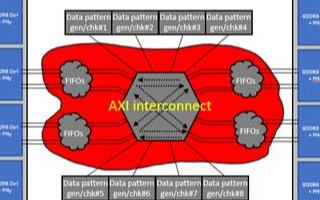

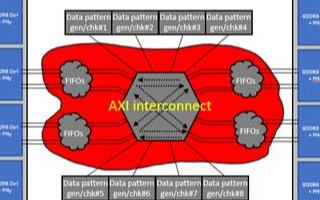

對(duì)于AXI interconnect模塊,我們采用Github上開源的AXI4總線連接器來實(shí)現(xiàn),這個(gè)AXI4總線連接器將4個(gè)AXI4總線主設(shè)備連接到8個(gè)AXI4總線從設(shè)備,源代碼可以在參考文獻(xiàn)

2020-09-03 12:39:38 797

797

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一種總線協(xié)議, Xilinx從 6 系列的 FPGA 開始對(duì) AXI 總線提供支持,目前使用 AXI4

2020-12-04 12:22:44 6179

6179

構(gòu)成的傳輸數(shù)據(jù)的通道, 一般由數(shù)據(jù)線、地址線、 控制線構(gòu)成。?Xilinx從6系列的 FPGA 開始對(duì) AXI 總線提供支持, 此時(shí) AXI 已經(jīng)發(fā)展到

2020-12-25 14:07:02 2957

2957

在 AXI 基礎(chǔ)第 2 講 一文中,曾提到賽靈思 Verification IP (AXI VIP) 可用作為 AXI 協(xié)議檢查工具。在本次第4講中,我們將來了解下如何使用它在 AXI4 (Full) 主接口中執(zhí)行驗(yàn)證(和查找錯(cuò)誤)。

2022-07-08 09:31:38 1945

1945 狀態(tài)。然后使用PL部分消抖處理后的按鍵進(jìn)行啟動(dòng)AXI總線工作,控制數(shù)據(jù)寫入。通過AXI互聯(lián)模塊連接到AXI_HP0端口,由PS端口進(jìn)行數(shù)據(jù)的讀取操作,并通過串口進(jìn)行讀寫數(shù)據(jù)的監(jiān)控。

2022-07-18 09:53:49 3902

3902

AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互連以及其他AXI4系統(tǒng)外設(shè)上生成特定序列(流量)。它根據(jù)IP的編程和選擇的操作模式生成各種類型的AXI事務(wù)。是一個(gè)比較好用的AXI4協(xié)議測(cè)試源或者AXI外設(shè)的初始化配置接口。

2023-11-23 16:03:45 580

580

VLANs 5.內(nèi)嵌ARP 6.用XGMII高速接口連接10G PMA-PCS PHY 7.一個(gè)工作在156.25MHz的64bit的axi4—stream接口讓用戶調(diào)試使用 8.可通過一個(gè)32bit

2016-03-11 10:57:58

最近在搞AXI4總線協(xié)議,有一個(gè)問題困擾了兩天,真的,最后知道真相的我,差點(diǎn)吐血。 問題是這樣的,我設(shè)置了突發(fā)長(zhǎng)度為8,結(jié)果,讀了兩個(gè)輪回不到,斷了,沒有AWREDATY信號(hào)了,各種找,最后發(fā)現(xiàn)設(shè)置

2016-06-23 16:36:27

如果在仿真的時(shí)候出現(xiàn)可以寫,可以讀,但是讀出來的數(shù)據(jù)一直是那么幾個(gè)的問題,很有可能,你和我一樣,是個(gè)馬大哈了,去看DQ,是不是地址也來來去去就那么幾個(gè)?是的話,可以考慮考慮你的地址的問題,AXI4

2016-06-24 16:25:38

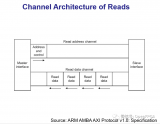

AXI4協(xié)議基于猝發(fā)式傳輸機(jī)制。在地址通道上,每個(gè)交易有地址和控制信息,這些信息描述了需要傳輸?shù)臄?shù)據(jù)性質(zhì)。主從設(shè)備間的數(shù)據(jù)傳輸有兩種情況,一種是主設(shè)備經(jīng)過寫通道向從設(shè)備寫數(shù)據(jù)(簡(jiǎn)稱寫交易

2021-01-08 16:58:24

AXI4-Stream跟AXI4的區(qū)別在于AXI4-Stream沒有ADDR接口,這樣就不涉及讀寫數(shù)據(jù)的概念了,只有簡(jiǎn)單的發(fā)送與接收說法,減少了延時(shí),允許無限制的數(shù)據(jù)突發(fā)傳輸規(guī)模

2021-01-08 16:52:32

AXI總線學(xué)習(xí)AXI協(xié)議的主要特征主要結(jié)構(gòu)通道定義讀寫地址通道讀數(shù)據(jù)通道寫數(shù)據(jù)通道寫操作回應(yīng)信號(hào)接口和互聯(lián)寄存器片基本傳輸Read burstOverlapping read burstWrite

2022-02-09 07:17:23

1、AXI接口協(xié)議詳解 AXI 總線 上面介紹了AMBA總線中的兩種,下面看下我們的主角—AXI,在ZYNQ中有支持三種AXI總線,擁有三種AXI接口,當(dāng)然用的都是AXI協(xié)議。其中三種AXI總線

2022-10-14 15:31:40

AXI 總線上面介紹了AMBA總線中的兩種,下面看下我們的主角—AXI,在ZYNQ中有支持三種AXI總線,擁有三種AXI接口,當(dāng)然用的都是AXI協(xié)議。其中三種AXI總線分別為:AXI4

2022-04-08 10:45:31

到新的通道。錯(cuò)誤的處理例化了一個(gè)Axi4ReadOnlySlaveError:可以看到,只有所有slave端口的地址段大小總和小于Axi4總線能覆蓋的地址范圍時(shí)方例化

2022-08-04 14:28:56

本帖最后由 eehome 于 2013-1-5 10:06 編輯

FPGA讀寫SDRAM的實(shí)例

2012-08-15 16:38:04

JTAG轉(zhuǎn)AXI-Lite),然后在PC端用VS2010調(diào)用API函數(shù)即可讀寫FPGA內(nèi)部用戶定義的寄存器,代替了常規(guī)復(fù)雜的嵌入式敲命令方式,節(jié)省了開發(fā)時(shí)間和周期,簡(jiǎn)化了系統(tǒng)聯(lián)調(diào)環(huán)境復(fù)雜度,實(shí)現(xiàn)了

2020-09-27 10:45:13

除數(shù)和商通道以及必要的時(shí)鐘和復(fù)位邏輯接口。每個(gè)AXI總線通道總是包括tdata tuser tlast 和握手信號(hào)tvalid tready,其中tuser為附加信息,tlast表示流模式下最后一個(gè)

2018-08-13 09:27:32

、AXI總線開發(fā)34_AXI總線協(xié)議介紹35_PL讀寫PS端DDR之Vivado創(chuàng)建過程36_PL讀寫PS端DDR之Vitis工程創(chuàng)建及聯(lián)合調(diào)試37_PS與PL交互之BRAM讀寫Vivado創(chuàng)建過程

2022-07-21 10:34:51

Xilinx FPGA EDK開發(fā)實(shí)例

2012-08-15 18:46:27

Xilinx FPGA EDK開發(fā)實(shí)例

2012-08-17 08:48:23

Xilinx FPGA入門連載47:FPGA片內(nèi)RAM實(shí)例之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述該工程

2016-01-20 12:28:28

實(shí)例內(nèi)部系統(tǒng)功能框圖如圖所示。我們通過IP核例化一個(gè)FIFO,定時(shí)寫入數(shù)據(jù),然后再讀出所有數(shù)據(jù)。通過ISE集成的在線邏輯分析儀chipscope,我們可以觀察FPGA片內(nèi)FIFO的讀寫時(shí)序。 2 模塊

2016-02-26 10:26:05

`Xilinx FPGA入門連載55:FPGA 片內(nèi)異步FIFO實(shí)例之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能

2016-03-07 11:32:16

`Xilinx FPGA入門連載59:FPGA 片內(nèi)ROM FIFO RAM聯(lián)合實(shí)例之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2016-03-16 12:43:36

Xilinx FPGA SF-SP6入門指南 -- FPGA片內(nèi)存儲(chǔ)器聯(lián)合實(shí)例之chipscope調(diào)試Lesson64 特權(quán)Xilinx FPGA SF-SP6入門指南 -- 基于SRAM批量讀寫的UART

2015-07-22 11:49:20

我想我在Xilinx 2015.4生成的verilog AXI組件代碼中發(fā)現(xiàn)了一個(gè)問題。為清楚起見,我選擇了“工具>創(chuàng)建和打包IP”,選擇“創(chuàng)建AXI4外設(shè)”,并選中“啟用中斷支持”。我能夠

2020-08-12 06:43:37

您可以將協(xié)議斷言與任何旨在實(shí)現(xiàn)AMBA?4 AXI4的接口一起使用?, AXI4 Lite?, 或AXI4流? 協(xié)議通過一系列斷言根據(jù)協(xié)議檢查測(cè)試接口的行為。

本指南介紹SystemVerilog

2023-08-10 06:39:57

本文介紹了AMBA3.0AXI的結(jié)構(gòu)和特點(diǎn),分析了新的AMBA3.0AXI協(xié)議相對(duì)于AMBA2.0的優(yōu)點(diǎn)。它將革新未來高性能SOC總線互連技術(shù),其特點(diǎn)使它更加適合未來的高性能、低延遲設(shè)計(jì)。最后介紹了基于AXI協(xié)議的設(shè)計(jì)實(shí)例,探討了利用IP復(fù)用技術(shù)和DesginWareIP搭建基于AXI協(xié)議的SOC系統(tǒng)。

2023-09-20 08:30:25

XHB將AXI4協(xié)議轉(zhuǎn)換為AHB-Lite協(xié)議,并具有AXI4從接口和AHB-Lite主接口。有關(guān)AXI4事務(wù)如何通過XHB橋接到AHB-Lite的信息,請(qǐng)參閱第2-2頁(yè)的表2-1

2023-08-02 06:51:45

in the reference design consist of AXI4, AXI4-Lite, andAXI4-Stream interfaces as described in the AMBA AXI4

2012-01-26 18:57:03

的fifo接口),用戶只要操作fifo接口,無需關(guān)心PCIE的內(nèi)部驅(qū)動(dòng)。為了便于讀者更加明白,可以深入了解PCIE,我們將會(huì)制作一個(gè)PCIE的連載系列。今天,首先說一下自定義AXI4的IP核,至于AXI4

2019-12-13 17:10:42

這是SoC Designer AXI4協(xié)議包的用戶指南。該協(xié)議包包含SoC Designer組件、探針和ARM AXI4協(xié)議的事務(wù)端口接口(包括對(duì)AMBA4 AXI的支持)。

2023-08-10 06:30:18

或起點(diǎn)嗎?此外,我的VHDL模塊具有AXI4流接口,而其他模塊具有自定義接口。如何使它們兼容?將等待有用的回復(fù)。問候

2020-05-22 09:24:26

data.)面向高速流數(shù)據(jù)傳輸;去掉了地址項(xiàng),允許無限制的數(shù)據(jù)突發(fā)傳輸規(guī)模。AXI4總線和AXI4-Lite總線具有相同的組成部分:(1)讀地址通道,包含ARVALID, ARADDR, ARREADY

2018-01-08 15:44:39

。

●AXI4: 主要面向高性能地址映射通信的需求,允許最大256輪的數(shù)據(jù)突發(fā)傳輸。

●AXI4-Lite: 是一個(gè)輕量級(jí)的,適用于吞吐量較小的地址映射通信總線,占用較少的邏輯資源

2023-11-03 10:51:39

主從設(shè)備間直接進(jìn)行數(shù)據(jù)的讀寫,主要用于高速數(shù)據(jù)傳輸?shù)膱?chǎng)合,如視頻、高速AD等。AXI-lite:可用于單個(gè)數(shù)據(jù)傳輸,主要用于訪問一些低速外設(shè)。3) AXI接口具有5個(gè)獨(dú)立通道:WriteAddress

2016-12-16 11:00:37

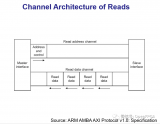

重點(diǎn)介紹AXI4接口,它由五個(gè)獨(dú)立的通道構(gòu)成:1、讀地址2、讀數(shù)據(jù)3、寫地址4、寫數(shù)據(jù)5、寫響應(yīng)下面是使用讀地址和讀數(shù)據(jù)通道實(shí)現(xiàn)讀傳輸過程的示意圖:圖 9.1.1 讀傳輸過程示意圖從上圖中可以看到,在

2020-10-22 15:16:34

,Xilinx在IP核中繼續(xù)使用AXI協(xié)議。本章我們對(duì)AXI協(xié)議作一個(gè)簡(jiǎn)單介紹,并在Vivado中實(shí)現(xiàn)一個(gè)AXI4接口的IP核,用于對(duì)ZYNQ PS端的DDR3進(jìn)行讀寫測(cè)試。本章包括以下幾個(gè)部分:1515.1

2020-09-04 11:10:32

,等)構(gòu)建起連續(xù)的數(shù)據(jù)流。這種接口適合做實(shí)時(shí)信號(hào)處理。 AXI4和AXI4-Lite接口包含5個(gè)不同的通道: Read Address Channel Write Address Channel

2021-01-07 17:11:26

介紹使用 AMD-Xilinx FPGA設(shè)計(jì)一個(gè)全連接DNN核心現(xiàn)在比較容易(Vitis AI),但是利用這個(gè)核心在 DNN 計(jì)算中使用它是另一回事。本項(xiàng)目主要是設(shè)計(jì)AI加速器,利用Xilinx

2023-02-21 15:01:58

的基礎(chǔ)上進(jìn)行擴(kuò)展,增加到 8 個(gè) AXI4 總線主設(shè)備連接到 8 個(gè) AXI4 總線從設(shè)備,同時(shí)加上了跨時(shí)鐘域邏輯。為了進(jìn)行對(duì)比,我們用另外一個(gè)設(shè)計(jì),目的還是用這 8 個(gè)讀寫模塊去訪問 8 個(gè)

2020-09-07 15:25:33

國(guó)外的融合技術(shù)專家展示了一項(xiàng)基于FPGA的數(shù)據(jù)采集系統(tǒng),用于合成孔徑成像技術(shù)。采用了Xilinx ISE設(shè)計(jì)軟件,支持ARM AMBA AXI4接口。文風(fēng)犀利,觀點(diǎn)新穎,FPGA中使用ARM及AMBA總線中不可多得的資料在賽靈思FPGA中使用ARM及AMBA總線[hide][/hide]

2012-03-01 15:48:17

設(shè)計(jì)的基于AXI4的DDR3多端口方案雖然傳輸速率有所提高,但由于AXI4協(xié)議本身的復(fù)雜性增加了開發(fā)使用的難度。本文實(shí)現(xiàn)并驗(yàn)證了期貨行情數(shù)據(jù)加速處理中基于FPGA的DDR3六通道UI接口讀寫防沖突

2018-08-02 09:32:45

對(duì)應(yīng)axi4stream_vip_pkg。第二個(gè)import是導(dǎo)入剛才例化的vip的pkg,格式為import {Component Name}_pkg

2022-10-09 16:08:45

在這個(gè)代碼的基礎(chǔ)上進(jìn)行擴(kuò)展,增加到8個(gè)AXI4總線主設(shè)備連接到8個(gè)AXI4總線從設(shè)備,同時(shí)加上了跨時(shí)鐘域邏輯。為了進(jìn)行對(duì)比,我們用另外一個(gè)設(shè)計(jì),目的還是用這8個(gè)讀寫模塊去訪問8個(gè)GDDR6通道

2020-10-20 09:54:00

多選一的抉擇相較于Axi4寫通路,多通路的多選一就容易多了。對(duì)于Axi4ReadOnlyArbiter,其僅需處理兩個(gè)問題:Ar通路多端口仲裁,其處理和寫通路aw通路基本相同,采用多端口RR調(diào)度即可

2022-08-08 14:32:20

`1、在開發(fā)zynq工程時(shí)遇到多個(gè)axi_hp總線讀寫ddr時(shí),總線鎖死。現(xiàn)象就是axi_hp的wready信號(hào)一直為低。架構(gòu)圖: 2、應(yīng)用write1、wrtie2、read1同時(shí)并行讀寫ddr3

2020-04-15 21:57:28

元素(如混合端序結(jié)構(gòu))的支持。

本文檔重點(diǎn)介紹AXI4中定義的AXI的關(guān)鍵概念,并強(qiáng)調(diào)了差異

適用時(shí),適用于AXI3。AXI5擴(kuò)展了AXI4,并引入了一些性能和Arm

架構(gòu)特征。此處描述的關(guān)鍵概念仍然適用,但

AXI5在此未涵蓋

2023-08-09 07:37:45

使用AXI4流快速讀取?如果這不是一個(gè)不錯(cuò)的方法,還有其他方法可以使用Virtex-7來解決這個(gè)問題嗎?以上來自于谷歌翻譯以下為原文Hey all. I'm currently working

2019-05-05 13:14:10

你好是否可以使用帶有AXI4接口的邏輯核心ip reed solomon編碼器版本9。問候Rose Varghese

2020-05-20 15:44:58

我想在ZYNQ上的PS也就是ARM上跑linux系統(tǒng),然后PL中有加入一個(gè)AXI4的IP,IP中有多個(gè)寄存器,我不知道該如何開發(fā)驅(qū)動(dòng)程序來對(duì)這個(gè)寄存器列表進(jìn)行讀寫。然后單個(gè)寄存器在Embedded

2015-07-22 19:11:29

` 1概述Zynq將ARM和FPGA整合到了一個(gè)芯片上,它的過人之處不僅是功耗、面積、成本的優(yōu)化,更多的是將二者之間原本極為受限的數(shù)據(jù)交互方式轉(zhuǎn)移到芯片內(nèi)部完成,4條AXI GP通道(2個(gè)從機(jī)、2個(gè)

2019-11-12 10:23:42

芯片可以做到了最優(yōu)狀態(tài)。因此,對(duì)于用Zynq做開發(fā)的工程師而言,如何玩轉(zhuǎn)AXI HP總線就成為了必修課。本實(shí)例(zstar_ex56)通過一個(gè)簡(jiǎn)單的AXIHP總線主機(jī)的讀時(shí)序和寫時(shí)序邏輯,來帶領(lǐng)讀者掌握

2019-11-26 09:47:20

` 1概述用于PL與DDR3交互的AXI HP總線,它的性能到底如何?吞吐量是否能滿足我們的應(yīng)用?必須4個(gè)通道同時(shí)使用?還是只使用1個(gè)通道?時(shí)鐘頻率的高低對(duì)AXI HP總線的帶寬有什么影響?這些

2019-11-28 10:11:38

的FPGA開始引入的一個(gè)接口協(xié)議(AXI3)。在ZYNQ中繼續(xù)使用,版本是AXI4,ZYNQ內(nèi)部設(shè)備都有AXI接口。AXI4-Lite則是AXI4的一個(gè)簡(jiǎn)化版本,實(shí)現(xiàn)AXI4運(yùn)行起來的最少接口

2019-05-06 16:55:32

`玩轉(zhuǎn)Zynq連載4——AXI總線協(xié)議介紹22 信號(hào)描述2.1 全局信號(hào)表2-1 全局信號(hào)信號(hào)來源描述ACLK時(shí)鐘源全局時(shí)鐘信號(hào)。所有的信號(hào)都在全局時(shí)鐘的上升沿采樣。ARESETn復(fù)位源全局復(fù)位信號(hào)

2019-05-10 16:15:22

讀寫分離的設(shè)計(jì)在Axi4總線中,讀和寫通道是完全相互獨(dú)立,互不干擾。故而無論是在設(shè)計(jì)Decoder還是Arbiter時(shí),均可以采用讀寫分離的方式。如前文所述,SpinalHDL在基于Axi4總線

2022-08-03 14:27:09

。writeIssuingCapability:指明AXI4總線寫最大同時(shí)支持的指令個(gè)數(shù)。combinedIssuingCapability:其值應(yīng)不小于前兩者,用于在AXI4總線讀寫地址通道共用的場(chǎng)景

2022-08-02 14:28:46

microblaze通過串口讀寫FPGA內(nèi)部axi4總線上的寄存器

2020-12-23 06:16:11

1.AXI通道每次數(shù)據(jù)交換都稱為事務(wù)。事務(wù)包括地址和控制信息,發(fā)送的數(shù)據(jù)以及任何響應(yīng)信息。實(shí)際數(shù)據(jù)以突發(fā)方式發(fā)送,其中包含多次傳輸。圖1顯示了由4個(gè)拍子或數(shù)據(jù)傳輸組成的讀寫突發(fā)。我們將在本文后面詳細(xì)討論

2020-09-28 10:14:14

目的是利用嵌入在Xilinx FPGA中的MicroBlaze核實(shí)現(xiàn)基于AXI總線的雙核嵌入式系統(tǒng)設(shè)計(jì)以及共享實(shí)現(xiàn)LED燈的時(shí)控.

2012-03-09 14:17:01 91

91 Xilinx的視頻的IP CORE 一般都是 以 AXI4-Stream 接口。 先介紹一下, 這個(gè)IP的作用。 下面看一下這個(gè)IP 的接口: 所以要把標(biāo)準(zhǔn)的VESA信號(hào) 轉(zhuǎn)為

2017-02-08 08:36:19 531

531

基于AXI4Stream總線協(xié)議,在Xilinx公司提供的FPGA上實(shí)現(xiàn)了一個(gè)具有缺陷像素校正、色彩濾波陣列插值、圖像降噪實(shí)時(shí)圖像采集與顯示功能的視頻系統(tǒng)。AXI4Stream總線協(xié)議由ARM公司

2017-11-17 08:58:01 4189

4189 1、AXI 總線通道,總線和引腳的介紹 AXI接口具有五個(gè)獨(dú)立的通道: (1)寫地址通道(AW):write address channel (2)寫數(shù)據(jù)通道( W): write data

2018-01-05 08:13:47 9601

9601

了期貨行情數(shù)據(jù)加速處理中基于FPGA的DDR3六通道UI接口讀寫防沖突設(shè)計(jì),簡(jiǎn)化了DDR3多通道讀寫的復(fù)雜度,隨著有效數(shù)據(jù)周期的提升,最高端口速率可達(dá)5.0 GB/s以上,帶寬利用率

2018-08-01 15:25:11 3184

3184

AXI-4 Memory Mapped也被稱之為AXI-4 Full,它是AXI4接口協(xié)議的基礎(chǔ),其他AXI4接口是該接口的變形。總體而言,AXI-4 Memory Mapped由五個(gè)通道構(gòu)成,如下圖所示:寫地址通道、寫數(shù)據(jù)通道、寫響應(yīng)通道、讀地址通道和讀數(shù)據(jù)通道。

2020-09-23 11:20:23 5453

5453

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實(shí)現(xiàn),不能直接和PS相連,必須通過AXI

2020-09-24 09:50:30 4289

4289

對(duì)于地址遞增或地址循回的猝發(fā),并且要求傳輸數(shù)據(jù)的寬度比數(shù)據(jù)總線上的要窄,這中猝發(fā)過程中,每次數(shù)據(jù)傳輸,使用不同的字節(jié)通道,這些通道對(duì)應(yīng)于猝發(fā)中每一個(gè)時(shí)鐘節(jié)拍。一個(gè)固定格式的猝發(fā),其地址保持不變,每拍數(shù)據(jù)傳輸都使用相同的字節(jié)通道。

2020-09-24 10:29:53 15587

15587

在FPGA程序設(shè)計(jì)的很多情形都會(huì)使用到AXI接口總線,以PCIe的XDMA應(yīng)用為例,XDMA有兩個(gè)AXI接口,分別是AXI4 Master類型接口和AXI-Lite Master類型接口,可通過

2020-10-30 12:32:37 3953

3953

新的賽靈思器件設(shè)計(jì)中不可或缺的一部分。充分了解其基礎(chǔ)知識(shí)對(duì)于賽靈思器件的設(shè)計(jì)和調(diào)試都很有幫助。 本篇博文將介紹賽靈思器件上的 AXI3/AXI4 的相關(guān)基礎(chǔ)知識(shí)。首先,我們將從一些通俗易懂的知識(shí)、理論

2020-09-27 11:06:45 5857

5857

XDMA是Xilinx封裝好的PCIE DMA傳輸IP,可以很方便的把PCIE總線上的數(shù)據(jù)傳輸事務(wù)映射到AXI總線上面,實(shí)現(xiàn)上位機(jī)直接對(duì)AXI總線進(jìn)行讀寫而對(duì)PCIE本身TLP的組包和解包無感。

2020-12-28 10:17:23 2692

2692 ZYNQ中DMA與AXI4總線 為什么在ZYNQ中DMA和AXI聯(lián)系這么密切?通過上面的介紹我們知道ZYNQ中基本是以AXI總線完成相關(guān)功能的: 圖4?34連接 PS 和 PL 的 AXI 互聯(lián)

2020-11-02 11:27:51 3880

3880

在 AMBA 系列之 AXI 總線協(xié)議初探 中,了解到 AXI 總線交互分為 Master / Slave 兩端,而且標(biāo)準(zhǔn)的 AXI 總線支持不同的位寬,既然是總線,那么必須要支持總線互聯(lián),多 Master,多 Slave的場(chǎng)景

2021-02-23 06:57:00 45

45 本系列我想深入探尋 AXI4 總線。不過事情總是這樣,不能我說想深入就深入。當(dāng)前我對(duì) AXI總線的理解尚談不上深入。但我希望通過一系列文章,讓讀者能和我一起深入探尋 AXI4。

2021-03-17 21:40:29 25

25 AXI是個(gè)什么東西呢,它其實(shí)不屬于Zynq,不屬于Xilinx,而是屬于ARM。它是ARM最新的總線接口,以前叫做AMBA,從3.0以后就稱為AXI了。

2021-04-09 17:10:10 4970

4970

本文介紹了AMBA 3.0 AXI的結(jié)構(gòu)和特點(diǎn),分析了新的AMBA 3.0 AXI協(xié)議相對(duì)于AMBA 2. 0的優(yōu)點(diǎn)。它將革新未來高性能SOC總線互連技術(shù),其特點(diǎn)使它更加適合未來的高性能、低延遲

2021-04-12 15:47:39 28

28 AXI總線學(xué)習(xí)AXI協(xié)議的主要特征主要結(jié)構(gòu)通道定義讀寫地址通道讀數(shù)據(jù)通道寫數(shù)據(jù)通道寫操作回應(yīng)信號(hào)接口和互聯(lián)寄存器片基本傳輸Read burstOverlapping read burstWrite

2021-12-05 16:21:03 5

5 本系列我想深入探尋 AXI4 總線。不過事情總是這樣,不能我說想深入就深入。當(dāng)前我對(duì) AXI總線的理解尚談不上深入。但我希望通過一系列文...

2022-02-07 11:36:33 4

4 AXI4 是一種高性能memory-mapped總線,AXI4-Lite是一只簡(jiǎn)單的、低通量的memory-mapped 總線,而 AXI4-Stream 可以傳輸高速數(shù)據(jù)流。從字面意思去理解

2022-07-04 09:40:14 5818

5818 本文主要介紹了AXI通道以及在每個(gè)通道下信號(hào)的概述。

2022-08-04 10:49:17 9635

9635 本系列我想深入探尋 AXI4 總線。不過事情總是這樣,不能我說想深入就深入。當(dāng)前我對(duì) AXI總線的理解尚談不上深入。但我希望通過一系列文章,讓讀者能和我一起深入探尋 AXI4。

2022-08-29 14:58:44 1272

1272 AXI (高性能擴(kuò)展總線接口,Advanced eXtensible Interface)是ARM AMBA 單片機(jī)總線系列中的一個(gè)協(xié)議,是計(jì)劃用于高性能、高主頻的系統(tǒng)設(shè)計(jì)的。AXI協(xié)議是被優(yōu)化

2022-10-10 09:22:22 8632

8632 Xilinx vivado下通常的視頻流設(shè)計(jì),都采用Vid In to axi4 stream --> VDMA write --> MM --> VDMA read -->

2022-10-11 14:26:03 4556

4556 上面兩圖的區(qū)別是相比AXI3,AXI4協(xié)議需要確認(rèn)AWVALID、AWREADY握手完成才能回復(fù)BVALID。為什么呢?

2023-03-30 09:59:49 668

668 AXI4 協(xié)議定義了五個(gè)不同的通道,如 AXI 通道中所述。所有這些通道共享基于 VALID 和 READY 信號(hào)的相同握手機(jī)制

2023-05-08 11:37:50 700

700

上文FPGA IP之AXI4協(xié)議1_協(xié)議構(gòu)架對(duì)協(xié)議框架進(jìn)行了說明,本文對(duì)AXI4接口的信號(hào)進(jìn)行說明。

2023-05-24 15:05:46 842

842

上文FPGA IP之AXI4協(xié)議1_信號(hào)說明把AXI協(xié)議5個(gè)通道的接口信息做了說明,本文對(duì)上文說的信號(hào)進(jìn)行詳細(xì)說明。

2023-05-24 15:06:41 669

669

AXI4協(xié)議是ARM的AMBA總線協(xié)議重要部分,ARM介紹AXI4總線協(xié)議是一種性能高,帶寬高,延遲低的總線協(xié)議。

2023-06-19 11:17:42 2097

2097

從 FPGA 應(yīng)用角度看看 AMBA 總線中的 AXI4 總線。

2023-06-21 15:21:44 1729

1729

AXI4:高性能內(nèi)存映射需求(如讀寫DDR、使用BRAM控制器讀寫BRAM等),為了區(qū)別,有時(shí)候也叫這個(gè)為 AXI4-Full;

2023-06-25 16:23:14 714

714

外部存儲(chǔ)器接口( EMIF )通信常用于FPGA和DSP之間的數(shù)據(jù)傳輸,即將FPGA作為DSP的外部SRAM、或者協(xié)同處理器等。Xilinx提供了AXI-EMC IP核,將其掛載到AXI總線用于

2023-08-31 11:25:41 2357

2357

本文開源一個(gè)FPGA項(xiàng)目:基于AXI總線的DDR3讀寫。之前的一篇文章介紹了DDR3簡(jiǎn)單用戶接口的讀寫方式:《DDR3讀寫測(cè)試》,如果在某些項(xiàng)目中,我們需要把DDR掛載到AXI總線上,那就要通過MIG IP核提供的AXI接口來讀寫DDR。

2023-09-01 16:20:37 1896

1896

LogiCORE JTAG至AXI Master IP核是一個(gè)可定制的核,可生成AXIAXI總線可用于處理和驅(qū)動(dòng)系統(tǒng)中FPGA內(nèi)部的AXI信號(hào)。AXI總線接口協(xié)議可通過IP定制Vivado

2023-10-16 10:12:42 410

410

以AXI4為例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有關(guān)IP核中,經(jīng)常見到AXI總線接口,AXI總線又分為三種: ?AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 386

386

在介紹AXI之前,先簡(jiǎn)單說一下總線、 接口 以及協(xié)議的含義 總線、接口和協(xié)議,這三個(gè)詞常常被聯(lián)系在一起,但是我們心里要明白他們的區(qū)別。 總線是一組傳輸通道,是各種邏輯器件構(gòu)成的傳輸數(shù)據(jù)的通道,一般

2023-12-16 15:55:01 248

248 本文主要集中在AMBA協(xié)議中的AXI4協(xié)議。之所以選擇AXI4作為講解,是因?yàn)檫@個(gè)協(xié)議在SoC、IC設(shè)計(jì)中應(yīng)用比較廣泛。

2024-01-17 12:21:22 224

224

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論