?

現(xiàn)場可編程門陣列或 FPGA 是一種集成電路,可以在制造后重新編程以模擬數(shù)字電路。

這些非常適合在批量生產(chǎn)之前制作新功能的原型,或者服務(wù)于對于定制芯片來說不經(jīng)濟的罕見用例。FPGA 并不是第一個具有此功能的器件,但它們是迄今為止商業(yè)上最成功的。他們的發(fā)展故事是技術(shù)與商業(yè)的迷人結(jié)合。

幾十年來,人們一直在尋找重新編程芯片的方法。

?開始

回到過去,如果有人想在某些實際硬件上制作原型并測試其邏輯功能,那么他們基本上只有兩種選擇。

首先,他們可以使用TTL芯片,這些是可以插入印刷電路板的晶體管。該方法的缺點是受到電路板尺寸和功耗限制的限制。

另一種選擇是定制芯片。正如所料,這種選擇會產(chǎn)生大量的前期成本。這意味著要支付光掩模費用,然后等待數(shù)月的制造時間。如果在設(shè)計中犯了一個錯誤,那么就無法準確地編輯JS 文件并重新編譯。

如今,這些定制芯片被稱為 ASIC 或?qū)S眉呻娐贰3悄愕挠美浅4螅駝t采取這條路徑可能沒有經(jīng)濟意義。

但是,如果需要擁有一個可以重新編程以具有你原型設(shè)計的功能的電路,該怎么辦?隨著 20 世紀 60 年代后集成電路的應(yīng)用越來越廣泛,現(xiàn)場可編程性開始變得更加迫切。

?PROM

第一個能夠?qū)崿F(xiàn)可編程邏輯功能的集成電路是可編程只讀存儲器—PROM。

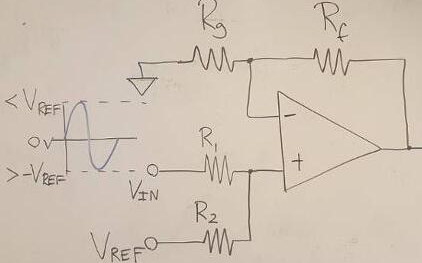

1970 年,Harris Semiconductor 推出了 PROM,可對其進行編程以實現(xiàn)可編程邏輯門陣列—AND 集和 OR 集。輸入首先進入 AND 集。然后,這些輸出會輸入 OR 集,最后輸出給最終用戶。

為什么是“與”門和“或”門?有一種邏輯函數(shù)稱為組合邏輯或與時間無關(guān)的邏輯。在這里,函數(shù)的輸出完全取決于你提供的輸入內(nèi)容,就像一個確定性系統(tǒng)。

這與順序邏輯函數(shù)相反,順序邏輯函數(shù)是一種輸出需要其他外部項的邏輯。就像滾動的總和一樣。如果你不記得之前的金額是多少,如何才能保留滾動金額?

回到組合。任何組合邏輯函數(shù)都可以由多個“或”門和“與”門來表達。這就是早期現(xiàn)場可編程邏輯電路的目標。

Harris 的 PROM 產(chǎn)品出廠時與門已修復(fù)。這意味著它們無法被修改。或門是可編程的。為了使它們可編程,Harris?在發(fā)貨時配備了由鎳鉻合金而不是傳統(tǒng)鋁制成的易熔金屬鏈接。

用戶通過“燒毀”開關(guān)進行編程——本質(zhì)上使它們只能一次性使用。這使得編程變得頗具挑戰(zhàn)性。你可以想象,為了不搞砸,有多大的壓力。

Harris在制造這些可燃保險絲方面做出了開創(chuàng)性的工作。他們在晶圓上創(chuàng)建了測試保險絲,并在測試過程中將其熔斷,以確保其正常工作。

事實證明,使用 PROM 實現(xiàn)可編程邏輯并不是真正有效,因為你不需要所有這些存儲單元來完成它,你需要更專業(yè)的東西。

?可編程邏輯陣列

1975 年,Signetics(后來成為 NXP Semiconductors 的一部分)向市場推出了可編程邏輯陣列 (PLA)。

通過 PLA,邏輯門的 AND 組和 OR 組都變得可編程。這使得用戶能夠?qū)崿F(xiàn)更廣泛的邏輯功能,例如最小乘積和,但成本很高。

PLA 需要更大的芯片,從而提高了總體成本。當時每個零件的價格按 1975 年美元計算約為 25 美元,相當于今天的 140 美元。

再次,通過燒毀保險絲連接來編程路線,因此錯誤的代價很高。巨大的靈活性帶來了巨大的容錯能力。不管怎樣,可以在這里看到市場的挑戰(zhàn)。盡管有這些優(yōu)點,PLA 卻從未真正流行起來。市場仍然需要一些東西來滿足現(xiàn)場可編程性的需求。

?可編程陣列邏輯和 MMI

1977 年,Monolithic Memories 的工程師 John Birkner 和 HT Chua 修改了 PLA,創(chuàng)建了一種新設(shè)備。

可編程陣列邏輯(PAL)。是的,實際上只是最后兩個詞顛倒了。PAL 犧牲了一些可配置性來獲得更好的性能和成本。它保留了可編程的 AND 門組,但固定了邏輯門的或集。PAL 設(shè)計所做的另一項修改是通過使用宏單元包含時序邏輯電路。

實際的計算機電路混合使用組合邏輯和時序邏輯。因此PAL設(shè)計者在PAL輸出端添加了觸發(fā)器等時序邏輯類型的器件。

觸發(fā)器是一種可以存儲一位信息(通常是 1 或 0)的電路,并可以將其用作輸出計算的一部分。就像電燈開關(guān)記住它是否被翻轉(zhuǎn)一樣。添加這些時序邏輯電路使 PAL 更適合消費者的日常使用。

然后在 20 世紀 80 年代初,新技術(shù)的出現(xiàn)使這些電路更易于重新編程。例如,你可以通過窗戶照射紫外線來將其擦除,不再需要保險絲。這些小型現(xiàn)場可編程器件(PLA、PAL 等)可歸類為簡單可編程邏輯器件。

PAL 取得了一些成功并被廣泛制作。內(nèi)存制造商發(fā)現(xiàn)它們與他們的核心產(chǎn)品足夠相似,可以添加到他們的產(chǎn)品中。Monolithic Memories 使用戶可以輕松學(xué)習(xí)如何使用它們。但 PAL 仍然面臨著一個大問題,新公司很快就出現(xiàn)來挑戰(zhàn)它們的缺點。

?阿爾特拉Altera

1980 年,一群原來自 Intel、Signetics 和 Intersil 的工程師創(chuàng)立了一家名為 Source III 的設(shè)計咨詢公司。他們專門幫助公司與其芯片供應(yīng)商合作,這在設(shè)計工具還不夠出色的時代是一件大事。

他們與 ASIC 芯片制造商合作的經(jīng)驗促使他們嘗試制造自己的現(xiàn)場可編程硬件。就這樣,他們從風(fēng)投那里籌集了 75 萬美元,并成立了一家新公司——Altera。

他們的第一款產(chǎn)品于 1984 年 7 月發(fā)布,是 EP300,一種采用 CMOS EPROM 工藝制成的簡單可編程邏輯器件。它是可擦除的,并且可以編程以滿足各種需求。

PAL 的一個大問題是它的結(jié)構(gòu)無法擴展。摩爾定律允許芯片上有更多的晶體管,但不能簡單地增加與門組并按比例獲得更好的性能。它變得太大并且開始減慢。

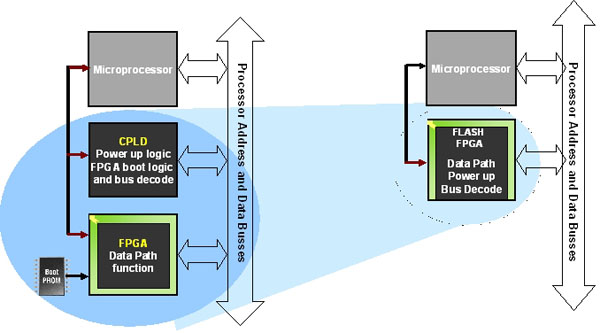

因此,為了更好地利用經(jīng)典微縮技術(shù),Altera 率先推出了復(fù)雜可編程邏輯器件。在這里,我們采用一堆較小的 PAL,并使用交叉連接將它們連接起來,以提高可擴展性。

Altera 選擇使用 CMOS 也具有影響力。當時美國還沒有CMOS,公司不得不去日本理光購買。

Altera 的成功預(yù)示著當今推動美國半導(dǎo)體世界發(fā)展的無晶圓廠設(shè)計模式的開始。

?賽靈思Xilinx

Altera 的復(fù)雜可編程邏輯器件向前邁出了一步,但正是另一家公司將這一概念變成了我們今天的樣子。

20 世紀 80 年代中期,美國半導(dǎo)體制造商 Zilog 的一位名叫 Ross Freeman 的工程師有了一個想法。

如果摩爾定律繼續(xù)下去,那么最終晶體管將變得如此便宜,以至于可以制造出滿足每個人需求的硅片。

他招募了一些 Zilog 同事加入他的新創(chuàng)業(yè)公司,幫助實現(xiàn)這個夢想。他們將其命名為 Xilinx,因為其原名 Logica 已被采用并于 1984 年 2 月正式啟用。

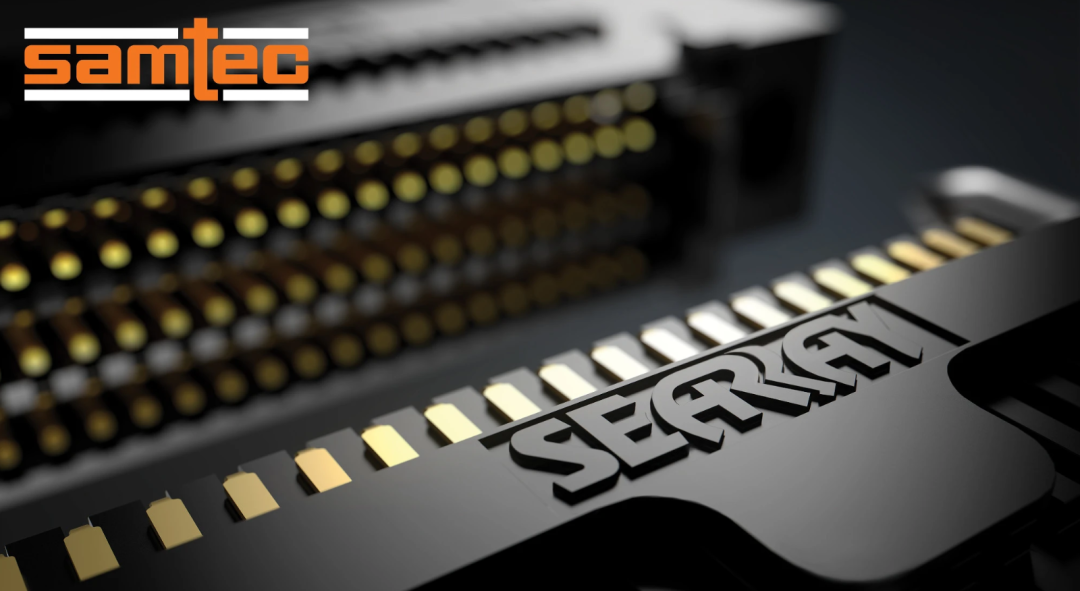

他們利用之前與精工公司(數(shù)字手表制造商)的聯(lián)系,達成了生產(chǎn)新芯片的協(xié)議。他們將其宣傳為精工保持工廠忙碌的一種方式,并提供在日本的獨家轉(zhuǎn)售權(quán)。

為了實際設(shè)計該產(chǎn)品,Xilinx 聘請了一位名叫 Bill Carter 的年輕設(shè)計師。Carter面臨著巨大的挑戰(zhàn)。他們唯一的設(shè)計指導(dǎo)是羅斯·弗里曼的專利申請。

此外,Seiko 使用 CMOS 2.5 微米工藝進行制造,而 Carter 此前沒有這方面的經(jīng)驗,他必須在與太平洋彼岸的一家講日語的晶圓廠溝通時即時學(xué)習(xí)它。

該芯片必須非常大,精工自己的工程師承認他們以前從未制造過這么大的東西,并提出了這個東西的風(fēng)險。對于一個年輕的初創(chuàng)公司來說,這樣的事情將是一場災(zāi)難。

Carter被反復(fù)告知要創(chuàng)造一些簡單的東西。不要嘗試任何瘋狂的事情,因為他們可能無法做到。他們制作的東西確實簡單而優(yōu)雅。

Xilinx XC2064,第一款 FPGA。

?FPGA 的出現(xiàn)

因此,如果我們回到 PAL,就會發(fā)現(xiàn)有一組與門和一組或門以及其他電路的宏單元,例如前面提到的觸發(fā)器。

與門是芯片現(xiàn)場可編程性的來源。正如我之前所說,PAL 架構(gòu)的核心問題是,如果 AND 門集變大,那么它就會變慢。這是因為該組內(nèi)的晶體管數(shù)量的增長速度遠遠快于“與”組兩側(cè)的輸入/輸出數(shù)量的增長速度。這些投入/產(chǎn)出無法快速增長。

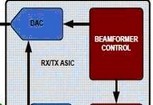

FPGA 針對這一缺點的解決方案是完全刪除 AND 門組。FPGA 將具有一系列與可編程開關(guān)連接在一起的可配置邏輯塊。設(shè)備輸入和輸出放置在設(shè)備周圍。

每個可配置邏輯塊內(nèi)部都有一對查找表,基本上就像映射到輸入的輸出數(shù)組。這個查找表就是 FPGA 實現(xiàn)任意邏輯功能的方式。

如有必要,函數(shù)結(jié)果可以路由到其他邏輯,例如觸發(fā)器。邏輯塊之間的互連本身是可編程的。連接可以配置為創(chuàng)建任意路徑,以便一個塊的輸出可以成為其相鄰塊的輸入。

第一批 Xilinx FPGA 要求用戶連接外部存儲器以在斷電時存儲編程。直到幾年后,一家名為 Actel 的公司發(fā)明了反熔絲技術(shù),對此有所幫助。

所有這一切與之前相比發(fā)生了根本性的變化。PAL 和 PLA 源自內(nèi)存芯片,它們的結(jié)構(gòu)具有家族相似性。另一方面,F(xiàn)PGA 看起來與此完全不同。

?第一個 FPGA

XC2064 是一款大型芯片,約有 85,000 個晶體管,排列成 64 個可配置邏輯塊和 58 個輸入/輸出塊。這相當于不到 1,000 個門,這在今天看來并不那么令人印象深刻。

然而,早在 1985 年,當該芯片首次流片時,其龐大的尺寸就限制了 Seiko 的制造能力。Carter 和他的團隊焦急地等待著精工收到第一盒 25 片晶圓。

他們打開盒子,希望能夠用一些東西對芯片進行編程。在這 25 個晶圓中,只有 1 個可以工作——第 11 個。Carter非常小心地拿走了最后一塊晶圓,并成功地在逆變器中進行了編程。它奏效了,于是第一個 FPGA 誕生了。

?FPGA 與 PAL

該設(shè)備與 Monolithic Memories 的 PAL 設(shè)備競爭,大多數(shù)客戶將兩者混為一談。它們看起來做著同樣的事情,但本質(zhì)上 FPGA 與 PAL 有很大不同。

首先,它的成本要高得多。這直接是因為模具太大,導(dǎo)致良率極低。因此,第一塊 FPGA 的成本為數(shù)百美元,而 PAL 則便宜得多。PAL 便宜得多,部分原因是它的結(jié)構(gòu)與內(nèi)存相似。如此相似,以至于內(nèi)存制造商將它們添加到他們的產(chǎn)品陣容中,每當內(nèi)存業(yè)務(wù)遇到困難時就大量生產(chǎn)它們。

其次,F(xiàn)PGA 的新穎性使其使用起來更加困難。Xilinx 推出了自己的電子設(shè)計自動化或 EDA 軟件,以幫助將設(shè)計融入 FPGA。它很復(fù)雜并且很難使用。此外,其性能也不容易預(yù)先預(yù)測。

與此同時,PAL 更容易理解。他們的 EDA 軟件很簡單,并且可以通過第三方廣泛使用,用戶發(fā)現(xiàn)很容易上手。

這種 EDA 福利對消費者來說非常友好,但事實證明它對 PAL 行業(yè)是一種長期損害。

?摩爾定律

然而,盡管存在所有這些早期的缺陷和缺點,第一款 FPGA 還是在市場上站穩(wěn)了腳跟,并最終蓬勃發(fā)展。FPGA 如何成為一個可行的競爭對手?

首先,我們得談?wù)勀柖伞PGA 的推出恰逢其時——技術(shù)與商業(yè)機會的交叉點

在技術(shù)方面,成熟的光刻技術(shù)將經(jīng)典縮放速度提高到了令人難以置信的速度。正如我所說,F(xiàn)PGA 可以擴展,而 PAL 則不能。因此,當晶體管成本大幅下降時,F(xiàn)PGA 最先受益。

需要連接晶體管。同樣重要的是,一種稱為化學(xué)機械拋光的新工藝使代工廠能夠大幅降低 FPGA 互連的制造成本。

突然之間,F(xiàn)PGA 的查找表數(shù)量和互連線長度開始呈指數(shù)增長。第一個 FPGA 速度緩慢且功能有限,但摩爾定律使其變得更快、更強大。那是技術(shù)方面。

在商機方面,20 世紀 90 年代初見證了獨立代工廠的興起。Altera 和 Xilinx 是無晶圓廠創(chuàng)業(yè)模式的早期先驅(qū)。突然之間,任何一組設(shè)計人員都可以提出一個想法,籌集資金,然后聯(lián)系一家晶圓廠來制造它,無需首先真正精通半導(dǎo)體制造。

代工廠則可以專注于解決早期困擾精工的問題。他們發(fā)現(xiàn)帶有大芯片的 FPGA 確實非常適合磨練和掌握他們的流程。

FPGA 市場因各種全新的 FPGA 初創(chuàng)公司而蓬勃發(fā)展。幾乎所有這些初創(chuàng)公司最終都關(guān)門大吉或退出 FPGA 業(yè)務(wù),但他們引入了優(yōu)化并發(fā)現(xiàn)了新功能。然后,Xilinx 和 Altera 將吸收他們的知識產(chǎn)權(quán)和專利,并將其添加到當前的產(chǎn)品陣容中。

?電子設(shè)計自動化EDA

另一個很大的區(qū)別是軟件。正如我之前提到的,PAL EDA 軟件更易于使用,并且可以通過第三方供應(yīng)商廣泛使用。

然而,這種對消費者友好的局面也有其劣勢。PAL 制造商無法控制軟件,因此無法決定其硬件的功能。這完全取決于他們的第三方 EDA 供應(yīng)商。PAL 制造商很快意識到他們只能做 EDA 軟件制造商能夠支持的事情,這限制了他們。

所有 PAL 制造商最終都生產(chǎn)類似的硬件,例如廉價的 Wintel PC 制造商。市場跌至最低點。

與此同時,F(xiàn)PGA 控制著自己的 EDA。就像 Nvidia 編寫自己的驅(qū)動程序一樣,它允許 FPGA 公司決定自己的未來,制作軟件以實現(xiàn)更多功能并增加自動化以提高生產(chǎn)力。

?結(jié)論

Xilinx 和 Altera 繼續(xù)占據(jù)數(shù)十億美元 FPGA 行業(yè)的多數(shù)份額。盡管這兩家公司不再獨立。英特爾早在 2015 年就以約 167 億美元的價格收購了 Altera。AMD 估計以 500 億美元收購了 Xilinx,最終于 2022 年完成。

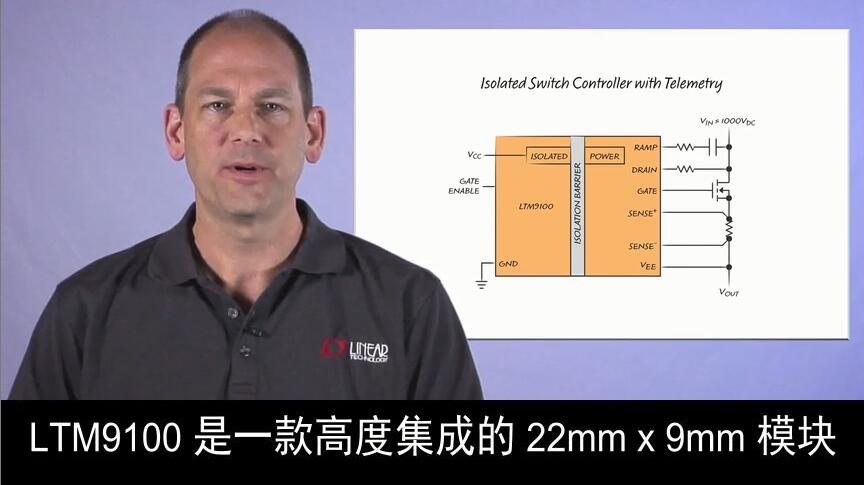

如今,F(xiàn)PGA 已廣泛應(yīng)用于各個行業(yè)。隨著 ASIC 的設(shè)計和制造成本越來越高,F(xiàn)PGA 填補了市場上的寶貴空白,尤其是在航空航天、軍事和電信領(lǐng)域。

它們不斷獲得新的功能,擴展到人工智能處理和數(shù)據(jù)中心等領(lǐng)域。挑戰(zhàn)仍然存在,我們將在以后的視頻中討論這些挑戰(zhàn),但 FPGA 的功能和成功是一個獨特的硅谷故事,也是行業(yè)創(chuàng)新能力的體現(xiàn)。

審核編輯:劉清

電子發(fā)燒友App

電子發(fā)燒友App

評論